一文详解RS触发器和D触发器

描述

上次我们介绍了RS触发器,他是由两个(或非门)或者(与非门)组成的。

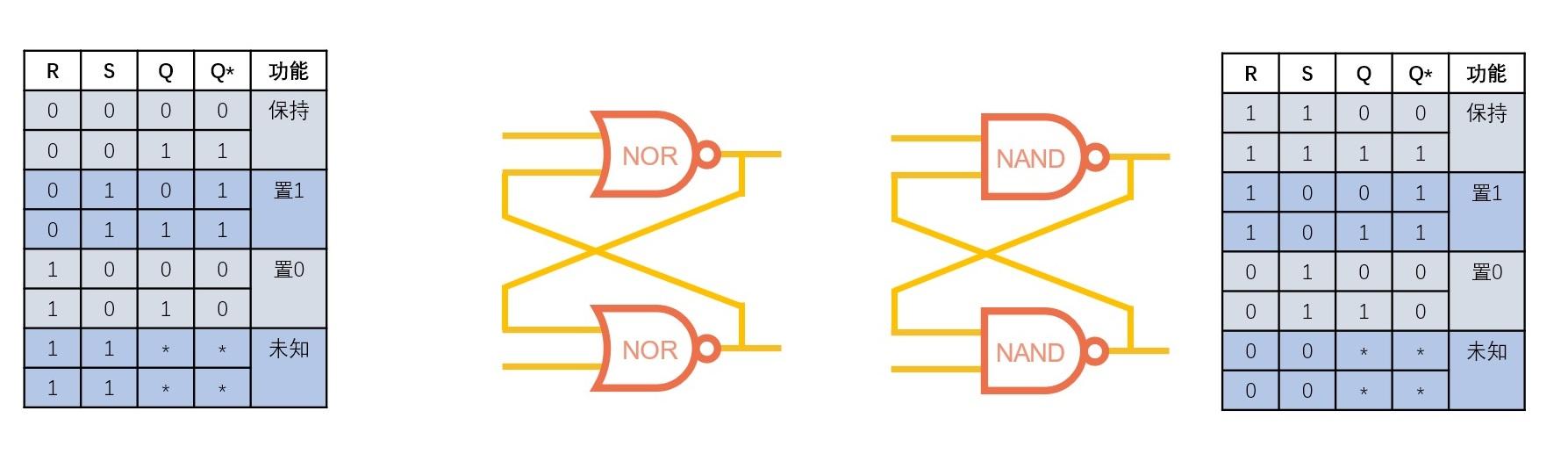

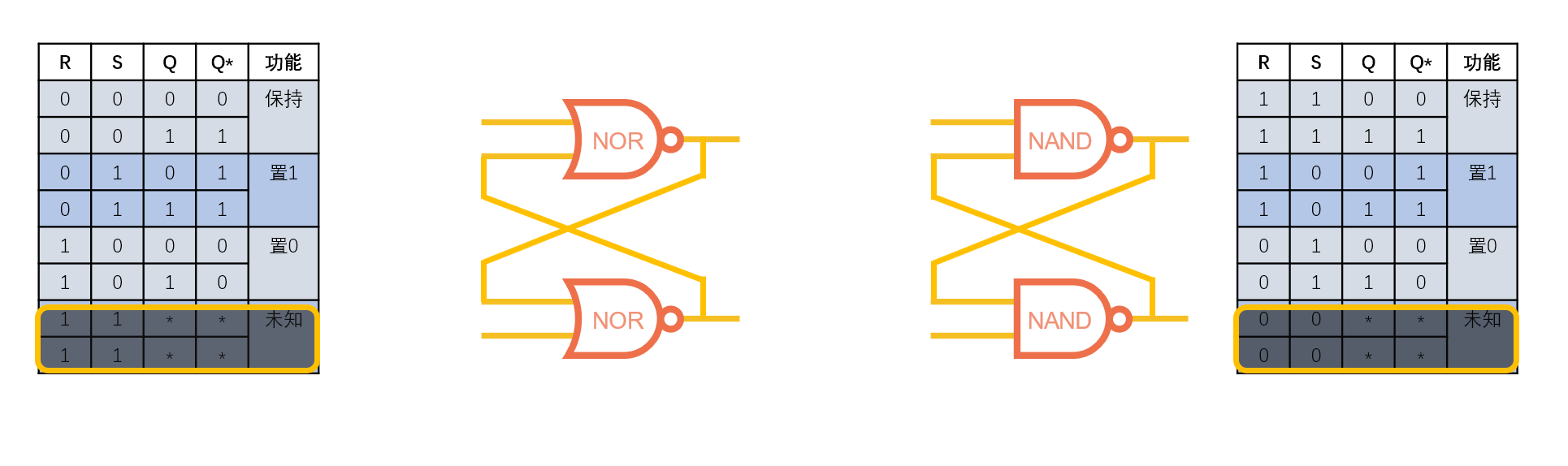

或非门RS触发器(左) 与非门RS触发器(右)

其核心就是图上的这个交叉反馈连接,而这条小小的反馈就完成了从组合逻辑到时序逻辑的跨越。让这个小小的电路有了记忆,可以记住上一刻发生的事(0和1)。

做过网络运维的小伙伴,一看到这个叉心里肯定一激灵。一个叉画起来简单,复杂性却是指数上升。

让我们来仔细把玩一下RS触发器。

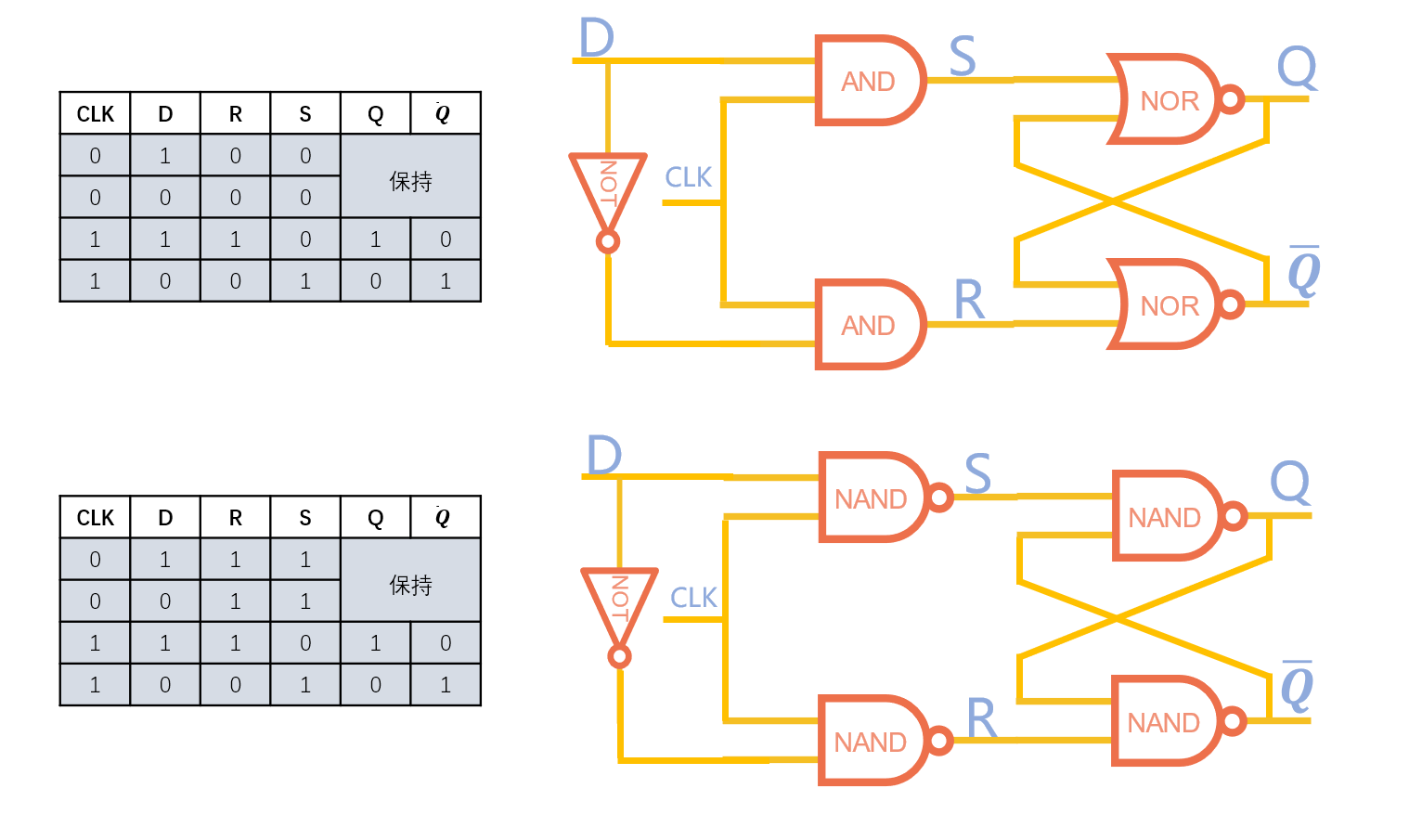

先看一下两种电路的真值表。(或非门)组成的RS触发器R=0,S=0时是保持状态,(与非门)的R=1,S=1时是保持状态。如下图所示

RS触发器的保持态

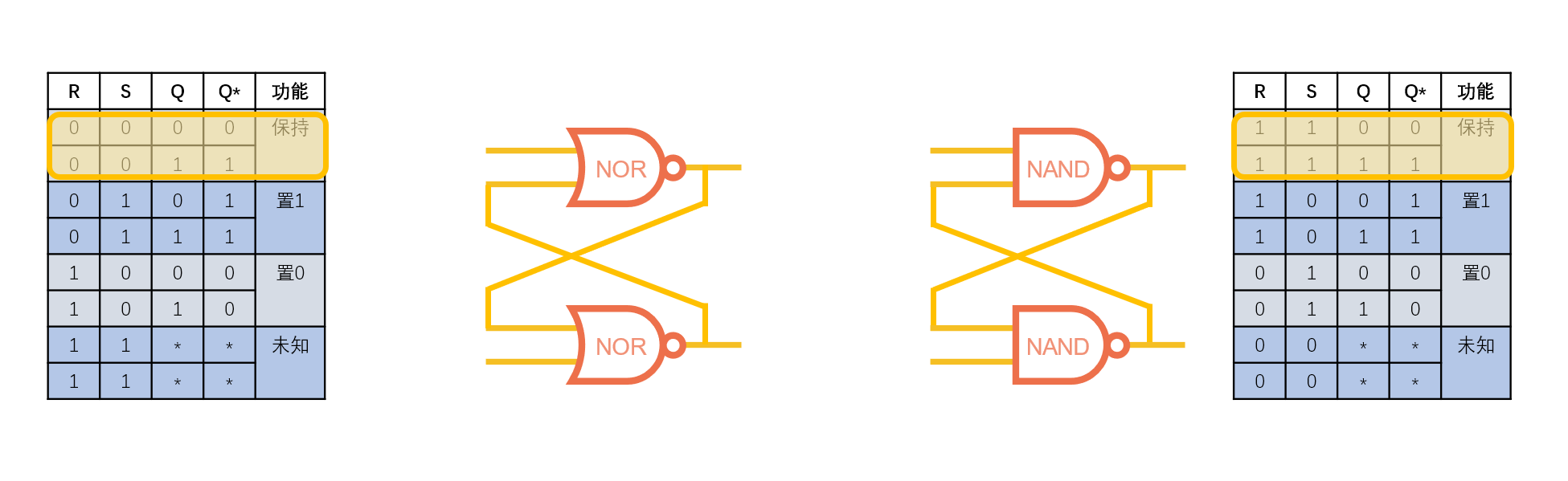

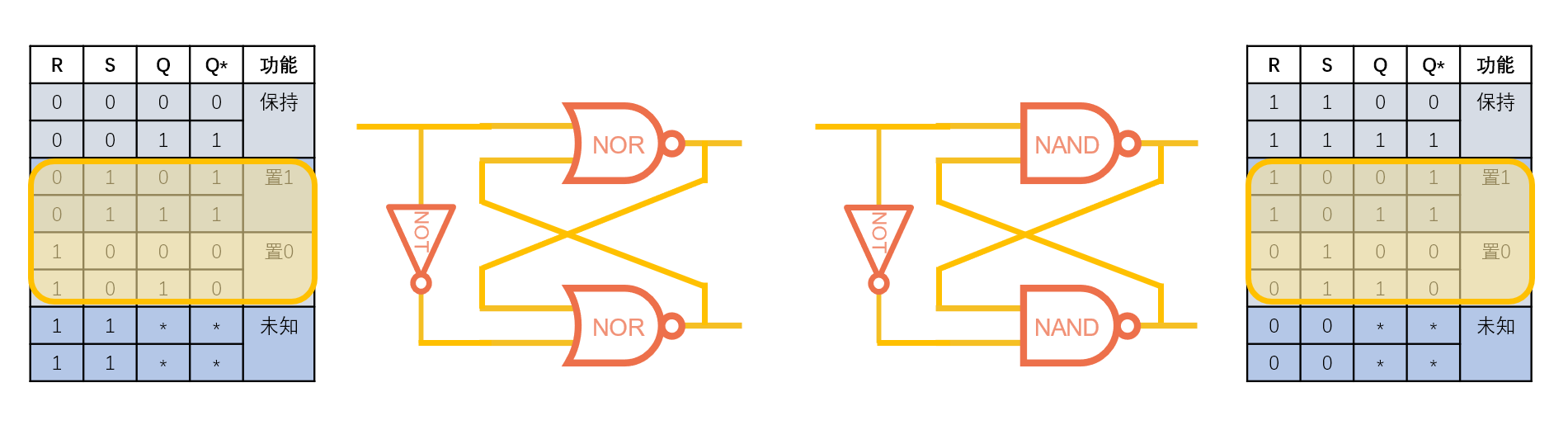

R=0,S=1时,(或非门)触发器的功能是置1,(与非门)的置1正好相反,是R=1,S=0。如下图所示

RS触发器置1

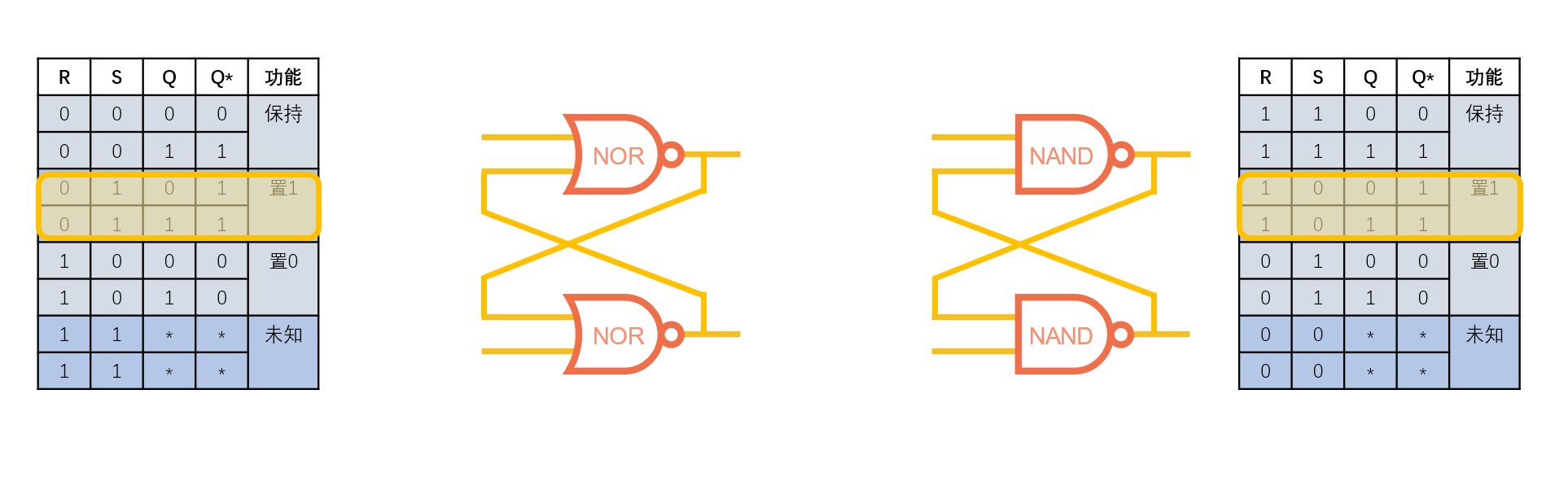

R=1,S=0时,(或非门)触发器置0,(与非门)反过来,是R=0,S=1。如下图所示

RS触发器置0

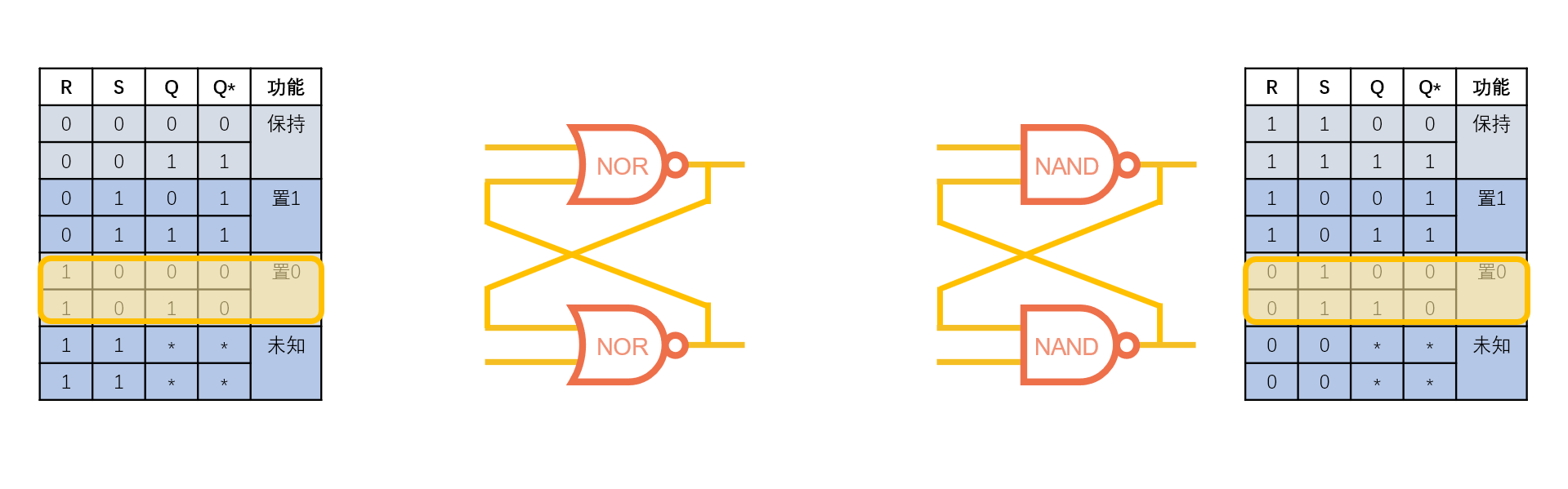

RS触发器有一个不可知的状态,对(或非门)电路来说,是RS同为1,(与非门)是同为0。如下图所示

RS触发器状态未知

不可知的状态并不是电路没有输出了,只是无法根据输入来确认输出,也就是说输出可能是这样,也可能是那样,因此我们没有办法来利用这个状态。

最初级的D寄存器

因为RS触发器存在一种输入在输出的时候无法确认状态,因此在使用的时候我们需要想办法避免这种输入的发生。

我们在输入的R和S之间加入一个(非门),使得RS永远不会相等,这样就变成了一个最简的D寄存器,D寄存器的D代表Data,可以实现数据的输入。如上图所示

相信大家已经发现,我们加入的(非门),虽然避免了RS触发器输出未知状态的可能,但却带来了新的的问题,电路的保持功能同样失效了,这意味着写入数据的功能也变得毫无意义,一旦输入信号撤走,或发生变化,电路输出的结果也会跟着改变。

RS 触发器输入装置

如何既要屏蔽未知输出,又要不失去触发器的保持功能呢?

我们需要给RS触发器设计一个前置输入装置。

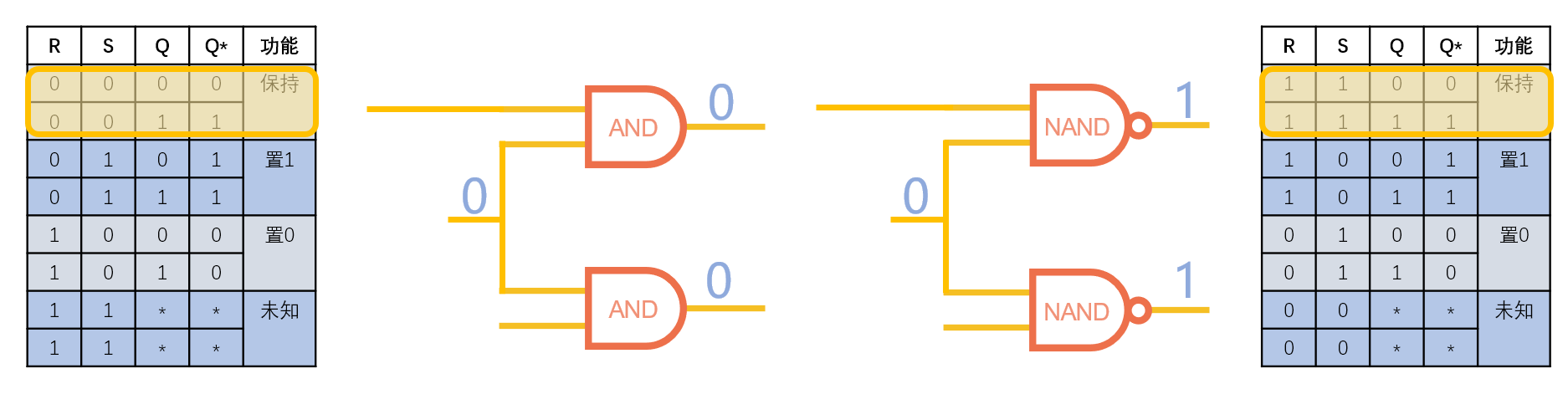

我们看真值表,对于(或非门)组成的RS触发器,当RS同为0时,保持触发器所存的数据。对 (与非门) 来说是RS同为1。因此我们用两个(与门) 或者两个 (与非门) 来实现这个功能,如上图所示。

我们把(与门)或者(与非门)的一个输入相连变成一个新的输入,我们叫这个新的输入CLK,根据(与门)和(与非门)的特点,我们给CLK输入0时,(与门)的逻辑一定输出两个0,(与非门)的逻辑一定输出两个1。

再把(与门)和(与非门)的另一个输入端之间放置一个(非门),(非门)的输入我们叫他D。新装置的真值表如下图,这个装置就能帮我们实现RS触发器所有的有效输入。

RS 触发器输入装置

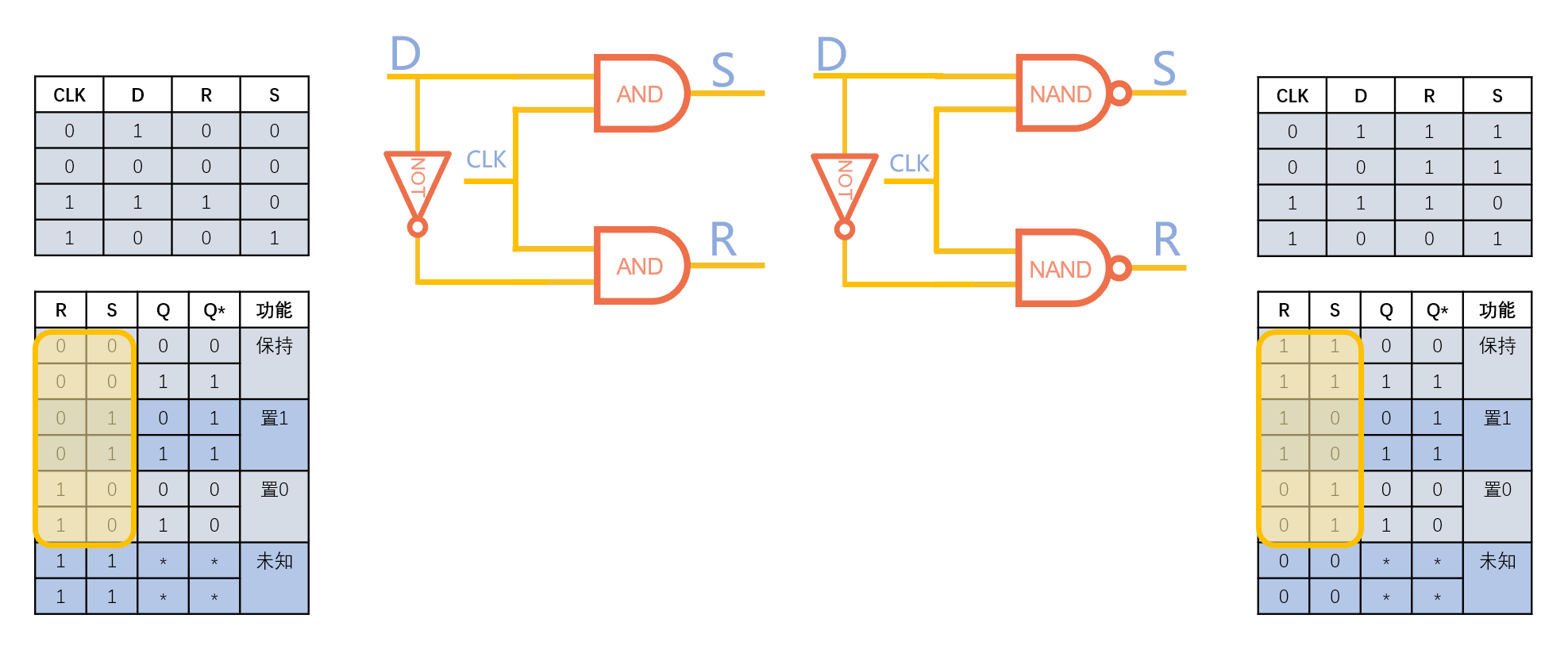

这时我们再把RS触发器拿出来,放置在这个输入装置的后端,这样就获得了一个有实际用途的D触发器。如下图所示。

看一下用不同门组成的D触发器和他们的真值表,仔细观察下他们之间的差异。

我们可以发现,功能上他们是完全一样的,电路上的差异,大家可以仔细端详一下。

D触发器有完整的读写控制能力,当CLK=0时,触发器处于保存状态,也就是无论这个时候D给出什么输入,触发器的内容不会变化。

当CLK=1的时候,D的值就会被写入触发器,完成写操作。

CLK可以是时钟信号,也可以是读写信号。

D触发器

以上简单的介绍了D触发器。D触发器实现了受控的数据存储能力,并且速度非常快,类似CPU中的寄存器就可以由D触发器来实现。

-

rs触发器的工作原理 rs触发器和sr触发器的区别2024-10-21 9710

-

d与rs触发器间功能的转换2024-08-28 2830

-

t触发器变为d触发器的条件2024-08-22 3747

-

t触发器与d触发器的区别和联系2024-08-11 6716

-

d触发器有几个稳态 d触发器和rs触发器的区别2024-02-06 5568

-

rs触发器和d触发器的区别 钟控rs触发器的作用是什么2023-09-07 7870

-

RS触发器是什么?解读rs触发器的作用和数字电路中的rs触发器的作用2022-10-19 15056

-

D触发器,D触发器是什么意思2010-03-08 5315

-

第十讲 基本RS触发器2009-03-30 11278

-

基本RS触发器2008-10-20 1608

-

JK触发器 D触发器 RS触发器 T触发器 真值表2007-09-11 20320

全部0条评论

快来发表一下你的评论吧 !