触发器的类型介绍

描述

触发器是构成时序逻辑电路的基本单元。它是一种具有记忆功能,能储存1位二进制信息的逻辑电路。在之前的文章中已经介绍过触发器了,这里再介绍一下其他类型的触发器。

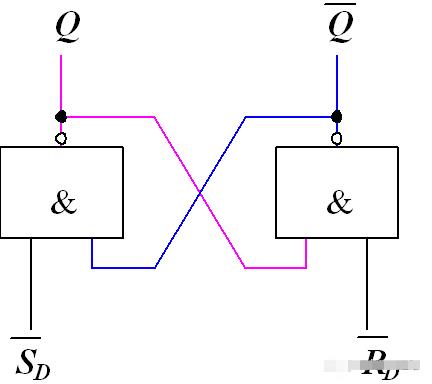

1、基本RS锁存器

最简单的触发器是基本RS触发器,基本RS锁存器可以由两个与非门构成,电路如下:

基本RS锁存器由电平触发,并且有一个重要的约束条件:/SD和/RD不能同时为零。即:/SD+/RD=1

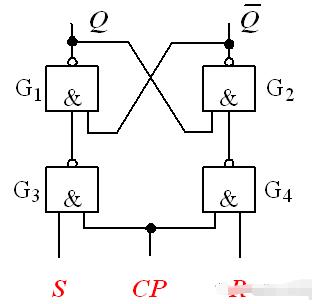

2、同步RS锁存器

许多时候,我们希望触发器只有在时钟来临时,输出状态改变,其它时候,触发器维持,因为这样做可以让多个电路单元的状态同时得以改变,这个时钟,我们称为同步时钟。

如下图所示,将基本RS锁存器的输入端分别经过一个与非门作为钟控信号。就变成了同步RS锁存器。

同步RS锁存器与基本RS锁存器的不同之处在于,只有时钟CP=1的时候,输出状态才能被改变。但是,同步锁存器也具有一个约束条件,就是当CP=1时,S和R不能同时为1。

此外,同步RS锁存器还有一个不足之处在于:当CP=1时,S和R若多次改变,每次改变都会影响输出。这种现象,称为空翻现象。

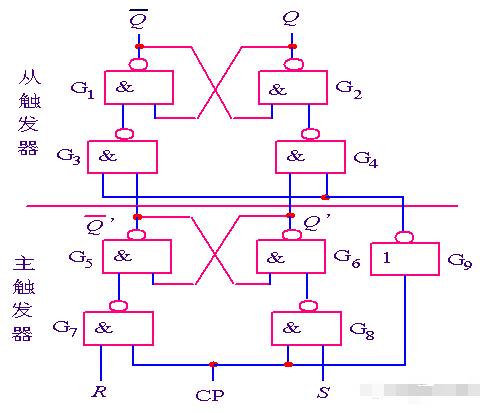

3、主从RS触发器

为了解决空翻为题,将两个同步RS触发器串联,电路如下:

主从触发器的触发翻转分为两个节拍:

(1)当CP=1时,CP’=0,从触发器被封锁,保持原状态不变:主触发器工作,接收R和S端的输入信号。

(2)当CP由1跃变到0时,即CP=0、CP’=1。主触发器被封锁,输入信号R、S不再影响主触发器的状态;从触发器工作,接收主触发器输出端的状态。

主从触发器的输出改变仅仅取决于CP的下降沿时刻。有效的解决了空翻问题。但是,主从RS触发器仍然存在约束条件:R、S不能同时为1。

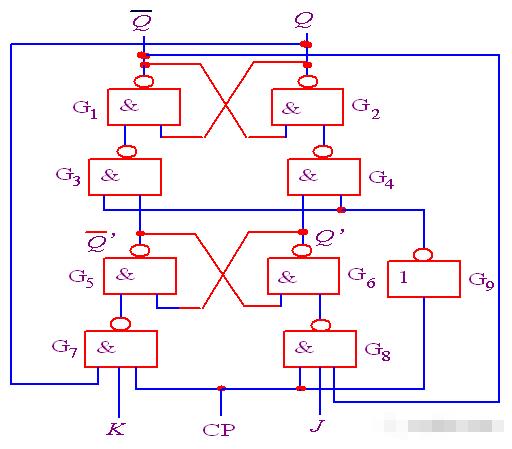

4、主从JK触发器

从基本RS锁存器可以看出,基本RS锁存器和同步RS锁存器的输出Q和/Q不会同时等于0,利用这个特点,若将主从RS锁存器的两个输出分别反馈至输入,即可解除这个约束。电路如下:

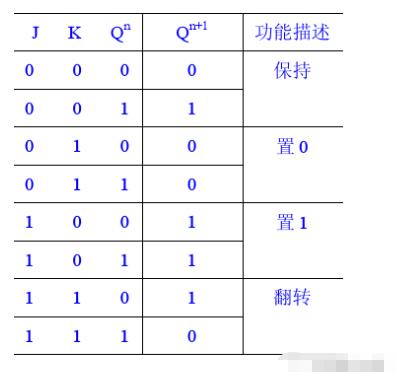

真值表如下:

功能描述:00不翻11翻,互补输入,J为打入端。

5、D触发器

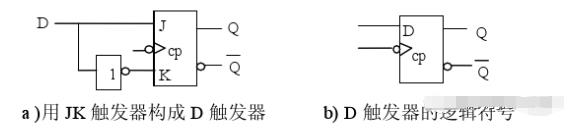

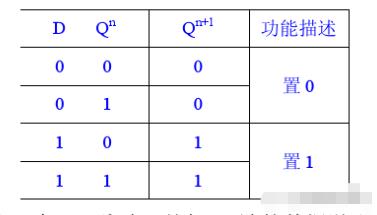

JK触发器可以很方便地构成D触发器,电路图和真值表如下所示。

6、T触发器

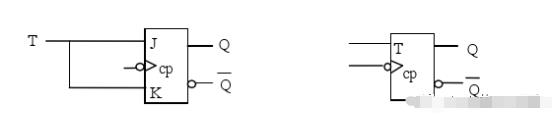

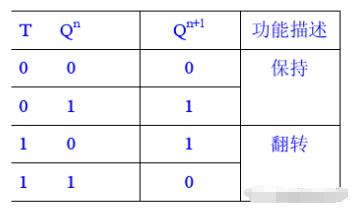

把JK触发器的两个输入端J、K连起来,作为一个输入端T,就构成T触发器了,电路图和真值表如下所示。

因为T=J=K,所以当T=0的时候,CP脉冲来后触发器维持原状不变。当T=1的时候,每一个CP脉冲来的时候,触发器状态翻转一次。

-

t触发器变为d触发器的条件2024-08-22 4567

-

同步触发器和边沿触发器的区别2024-08-12 3992

-

边沿触发器的类型有哪些2024-08-11 2272

-

触发器的基本概念、类型及工作原理2024-07-23 11157

-

d触发器有几个稳态 触发器上升沿下降沿怎么判断2024-02-06 8342

-

触发器的触发顺序是什么2024-02-05 2597

-

寄存器和触发器的区别介绍2018-04-11 28206

-

单稳态触发器有哪些_单稳态触发器工作原理介绍2018-03-28 44015

-

触发器的作用_触发器的特点介绍2018-03-27 22474

-

什么是边沿触发器_边沿D触发器介绍2018-01-31 73422

-

jk触发器是什么原理_jk触发器特性表和状态转换图2017-12-25 192883

-

触发器的类型转换2010-08-23 5839

-

触发器介绍及分类2010-08-19 20638

全部0条评论

快来发表一下你的评论吧 !