一种改进的流水线级运放共享电路设计

应用电子电路

描述

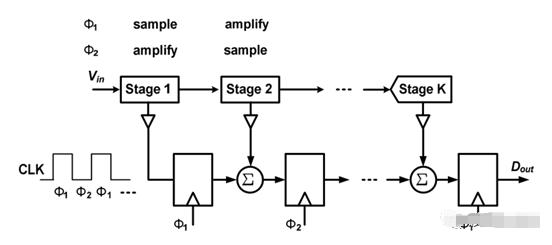

图1 流水线级电路的交替工作原理

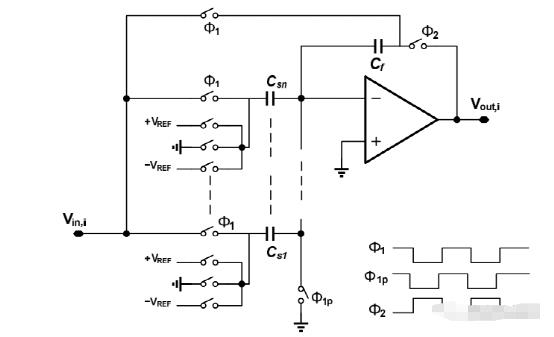

图 2 第 i 级开关电容的 MDAC

OP共享的优点:降低功耗,节省芯片面积

由图1可知,当pipeline ADC正常工作时,各级流水线量化电路交替工作于采样和放大相。由图 2 所示的级电路的实现原理可以看出,采样相时,各级MDAC 中的运算放大器并没有工作,它的输入、输出分别置于复位状态,因此可以考虑将运算放大器在毗邻的流水线级之间共享 ,这样运算放大器的数目会减少一半,可以有效地降低功耗,同时也节省了芯片面积。

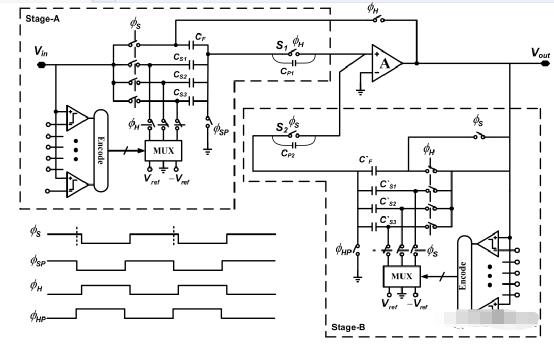

图 3传统的流水线级运放共享原理

OP共享的缺点:引入信号相关的采样误差图 3是传统流水线级间运放共享的电路原理。从图中可以看到,首先,实现流水线级间运放的共享需要额外的开关,如图中的开关 S 1 和 S 2 ,而开关的寄生电容 C p1 和 C p2 会成为一条潜在的耦合通路,使相邻的前后两级间发生串扰,从而引入信号相关的采样误差 [28] 。

如图中所示,当 Ф S 为高电平时,流水线级 Stage-B工作于放大状态,产生余量输出信号,流水线级 Stage-A 则工作于采样状态,此时任何的干扰信号,如前级电路的建立信号或是前级比较器电路的回踢噪声信号,通过寄生电容 C p1 会出现在运放的求和节点,从而影响 Stage-B 的信号输出,同样地,当 Ф H 为高电平时,流水线级 Stage-A 工作于放大状态,而 Stage-B 则工作于采样状态,此时任何的干扰信号,都会通过寄生电容Cp2出现在运放的求和节点,从而影响 Stage-A 的信号输出。

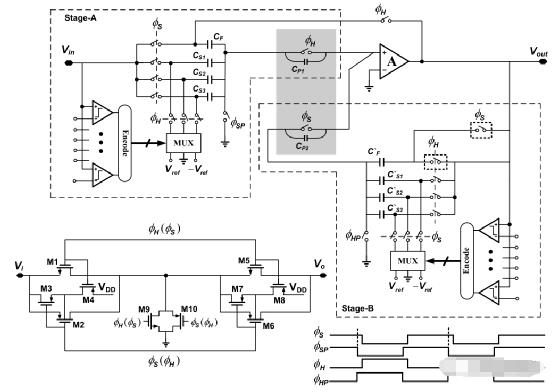

T型开关:改善耦合串扰,提升SNDR为了缓解这一问题,提高共享运放流水线级的建立精度,本文仔细分析了运放共享结构的时序,提出了一种改进的流水线级运放共享电路如图 4 所示。

图 4 改进的流水线级间运放共享电路

对比图 3.11和图 3.12 所给出的电路原理可知,在图 3.12中虚线框中的开关可以省去而不会影响电路的功能。事实上,移除冗余开关的同时,开关本身的导通电阻也被消除了,因而运放的输出建立时间也会加快,有利于高速应用 。所提出运放共享结构的时序关系如下:当 Ф S 为高电平时,运放用于流水线级Stage-B,此时 Stage-B 工作于保持状态,电容 C F `跨接在运放的输入输出端,形成闭合的负反馈环路,采样电容 C S1 `、C S2 `和 C S3 `根据 sub-ADC 的输出分别接在+V ref 、0 和−V ref 端,执行减法和放大的操作,产生余量信号。同时,Stage-A 工作于采样状态,电容 C S1 、C S2 、C S3 和 C F 的底板接在信号输入端。当 Ф H 为高电平时,Stage-A 和 Stage-B 的功能互换,此时运放用于 Stage-A 中。时钟 Ф SP 和 Ф HP相对于时钟 Ф S 和 Ф H 提前关断构成底板采样,以抵消电荷注入与时钟馈通的影响。为了克服寄生电容所引入的耦合通道,在图4 中阴影部分的开关,采用了衬偏效应抵消的 T 型开关电路 。

如图中所示,T 型开关电路由三个 CMOS 传输门(CMOS-TG)构成,其中管子 M1 和 M2 组成传输门 T1,管子 M5 和 M6 组成传输门 T2,管子 M9 和 M10 组成传输门 T3。Ф H 和 Ф S 是非交叠的时钟相。T1 和 T2由相同的时钟相控制,而T3由相反的时钟相控制,增加管子M3、M4、M7和M8是为了抵消 pMOS 的衬偏效应。当 Ф S 为高电平时,T1 和 T2 导通,T3 关断,输入与输出端相连通,当 Ф H 为高电平时,T1 和 T2 关断,T3 导通,此时,T3 为输入相关的馈入干扰信号提供了一条连接至地的通路,有效降低了馈通信号对运放求和节点的影响,可以获得更为精确的余量输出信号。仿真结果表明,相较于传统的运放共享结构,改进的运放共享方案在 SNDR 上约有 3.42dB 的提高。

记忆效应1:OP高增益可缓解记忆效应在共享运放的流水线级中,运放始终处于工作状态,运放输入端的虚地节点不能复位,这会引入所谓记忆效应(Memory Effects)的问题。共享于毗邻流水线级间的运算放大器在输入求和节点处存在寄生电容 C p ,由于输入端的虚地节点不能复位,存储在虚地节点寄生电容中的电荷就会影响余量输出信号,这称为记忆效应。

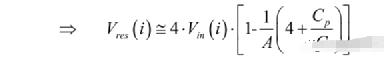

由上式可以看出,记忆效应的确在输出中引入了误差量(上式第二项)。同时也可以看出,采用高增益的运放可以有效缓解这一误差量的影响。

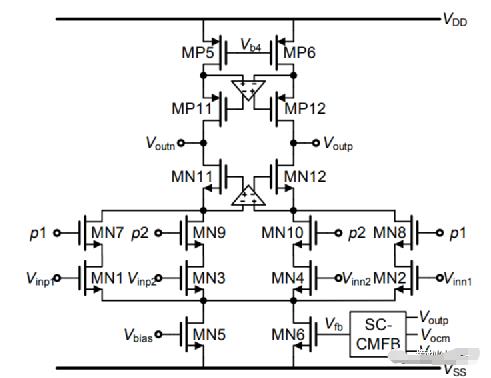

记忆效应2:改进型OP结构可避免记忆效应一种双输入内建开关型OP可以解决记忆效应问题。如下图所示。P1有效时,MN1/MN2作为输入对;P2有效时,MN3/MN4作为输入对。每个MDAC连接到各自的输入对以避免记忆效应。

Figure 4. Dual-input op-amp

-

什么是流水线 Jenkins的流水线详解2023-05-17 1782

-

CPU流水线的问题2022-09-22 3160

-

嵌入式_流水线2021-10-20 1268

-

各种流水线特点及常见流水线设计方式2021-07-05 10100

-

求一种高性能低功耗流水线ADC设计方法2021-04-22 1723

-

FPGA中的流水线设计2020-10-26 3266

-

FPGA之为什么要进行流水线的设计2019-11-28 4416

-

一种系统化流水线控制方法_章其富2017-03-19 772

-

一种改进运放共享结构的11位流水线ADC设计2017-01-07 752

-

流水线ADC的行为级仿真2012-04-05 1017

-

流水线技术在高速数字电路设计中的应用2010-07-17 956

-

什么是流水线技术2010-02-04 4408

-

一种流水线结构AD转换器的速度分析方法2008-12-03 880

全部0条评论

快来发表一下你的评论吧 !