抑制电磁干扰(EMI)的实用电路技术

EMC/EMI设计

描述

【导读】本系列文章的第 1 部分至第 4 部分详细介绍了开关电源稳压器引起的传导发射和辐射发射,包括噪声产生机制、测量要求、频率范围、适用的测试限值、传播模式和寄生效应。在第 5 部分中,我将基于这一理论基础介绍抑制电磁干扰 (EMI) 的实用电路技术。

一般来说,电路原理图和印刷电路板 (PCB) 对于实现出色的 EMI 性能至关重要。第 3 部分重点强调通过谨慎的元器件选型和 PCB 布局尽量减小“功率回路”寄生电感的重要性。电源转换器集成电路 (IC) 的封装技术及其提供的 EMI 特定功能对此产生了巨大的影响。如第 2 部分所述,必须使用差模 (DM) 滤波方可将输入纹波电流的幅值充分降低至满足 EMI 合规性要求的水平。与此同时,如果需要抑制约 10MHz 以上的发射,通常使用共模 (CM) 滤波。在高频条件下,使用屏蔽也可以获得优异的结果。 本文主要介绍这些方面的内容,专门聚焦于带有集成功率 MOSFET 和控制器的转换器解决方案,提供抑制 EMI 的实例和应用指导。一般来说,转换器应在合理范围内超出传导 EMI 一定的裕度,为达到辐射限值预留空间。幸运的是,多数减少传导发射的步骤对于抑制辐射 EMI 同样有效。

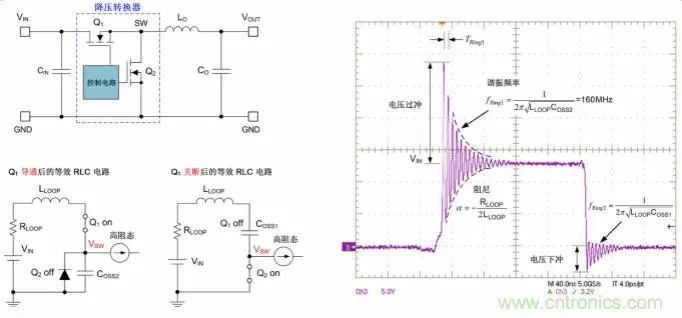

了解 EMI 的相关挑战 DC/DC 转换器中的 EMI 主要由其快速开关的电压和电流特性所致。与转换器的不连续输入或输出电流相关的 EMI 相对容易处理,但更大的问题是开关电压 dv/dt 和电流 di/dt 中的谐波成分,以及与开关波形相关的振铃。 图 1 所示为存在噪声的同步降压转换器的开关 (SW) 电压波形。振铃频率范围为 50MHz 至 200MHz,具体取决于寄生效应。此类高频成分可以通过近场耦合传播到输入电源线、周边元器件或输出总线(如 USB 电缆)。体二极管反向恢复存在类似的问题,随着恢复电流流入寄生回路电感,振铃电压升高。

图 1:同步降压转换器在 MOSFET 导通和关断开关转换期间的开关节点电压波形和等效电路 图 2 的原理图标识了降压转换器电路的两条重要回路。最大限度缩减电源回路的面积至关重要,原因是该参数与寄生电感和相关 H 场传播成正比。主要设计目标是通过减小寄生电感最大程度提升寄生 LC 谐振电路的谐振频率。此举可以降低存储的无功能量总值,减少开关电压峰值过冲。

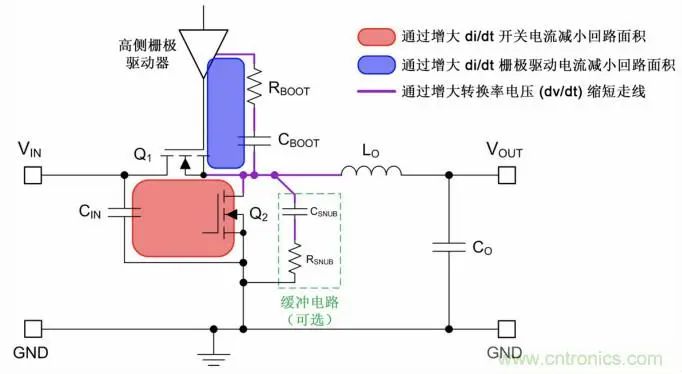

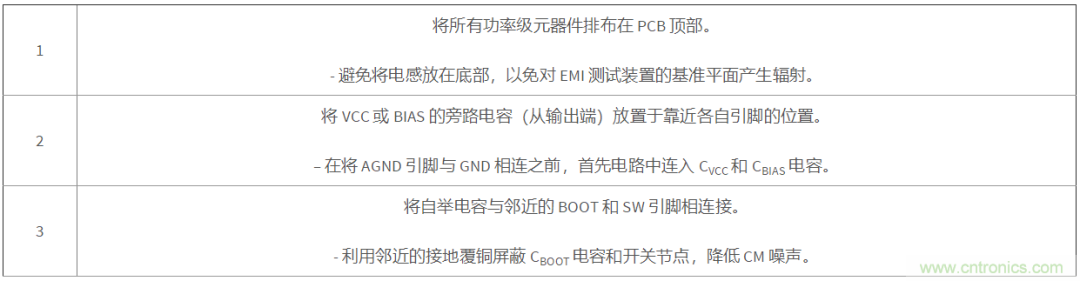

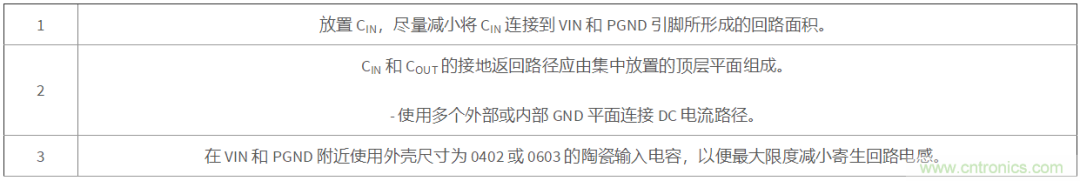

图 2:简化的同步降压转换器原理图(针对 EMI 标出了关键回路和走线) 在图 2 所示的自举电容回路中,高侧 MOSFET 的导通速度由一个标记为 RBOOT 的可选串联自举电阻进行控制。自举电阻会改变驱动电流瞬变率,降低 MOSFET 导通期间的开关电压和电流转换率。另一种方法是在 SW 和 GND 之间添加一个缓冲电路。同理,该缓冲电路应根据每次开关转换时的瞬态电流尖峰,占用最小的回路面积。当然,缓冲电路和栅极电阻会增加开关功率损耗,需要在效率和 EMI 之间进行权衡。如果效率和散热性能同样非常重要,则需要使用其他技术解决 EMI 相关的挑战。 转换器的 PCB 布局 表 1 至表 5 总结了通过优化 PCB 布局及元器件排布削弱 DC/DC 转换器 EMI 信号的基本准则。我将在本文的后续部分提供一项 PCB 布局案例研究,探讨如何优化降压转换器的 EMI 特性。 表 1:布线及元器件排布。

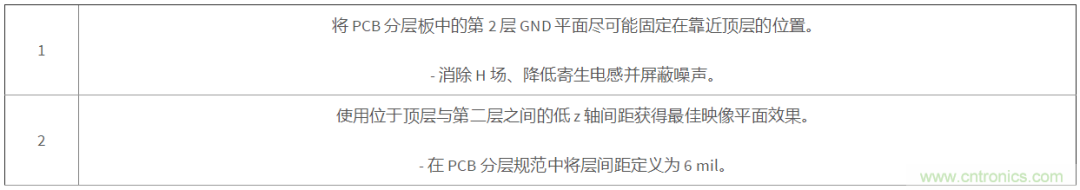

表 2:GND 平面设计。

表 3:输入和输出电容。

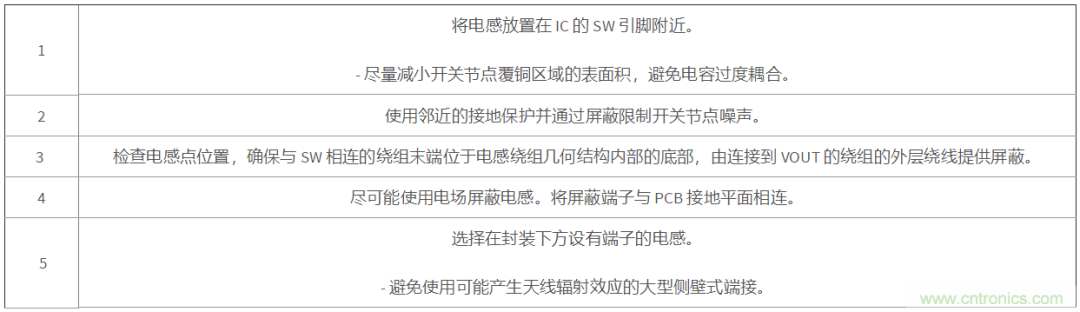

表 4.电感和开关节点布局。

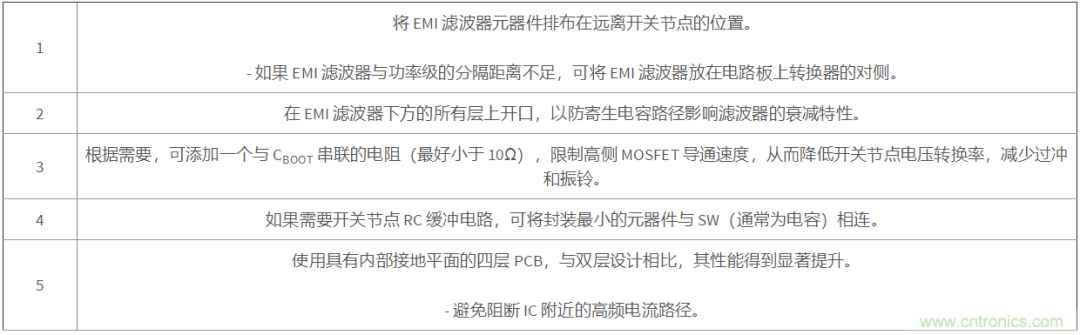

表 5.EMI 管理。

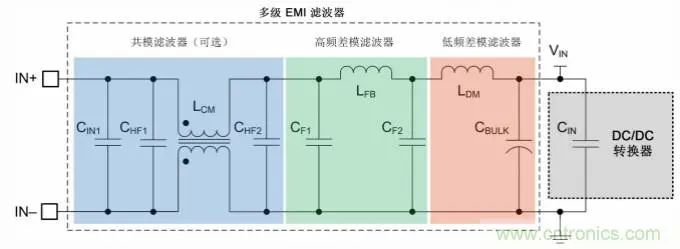

EMI 输入滤波器 图 3 所示为典型的多级 EMI 输入滤波器。低频和高频部分可提供 DM 噪声衰减,也可选择 p 级,通过 CM 扼流器提供 CM 衰减。标记为 CBULK 的电解电容具有固有的串联电阻 (ESR),可用于设置所需阻尼,降低转换器输入的有效品质因子,保持输入滤波器的稳定性。 DM 电感的自谐振频率 (SRF) 限制滤波器第一级可实现的高频 DM 衰减。滤波器第二级通常至关重要,其使用铁氧体磁珠在高频条件下提供附加的 DM 衰减,此时额定阻抗通常为 100MHz。标记为 CF1 和 CF2 的陶瓷电容可将噪声分流到接地端。

图 3:具有 DM 和 CM 级的三级 EMI 输入滤波器 DM 滤波器的电感一般设置为削弱基波和低频谐波的值。应使用尽可能小的电感来满足低频滤波要求,因为匝数较多的大电感具有较高的等效并联电容 (EPC),导致其 SRF 较高,影响其在高频下的性能。 标记为 LCM 的 CM 扼流器针对 CM 电流提供较高的阻抗,其泄漏电感也可提供 DM 衰减。然而,在部分要求接地连接必须保持完好的应用中,该元器件不适用,这些应用需要更安静的转换器设计,CM 扼流器不再是首选。 为了演示 CM 扼流器的效果,图 4 展示了德州仪器 (TI) LM53603,这是一款采用双层 PCB 的 36V、3A DC/DC 转换器解决方案 [7]。该器件的功率级位于顶层,EMI 输入滤波器则放置于底部。如图 4 中的布局所示,滤波器附近的接地平面覆铜区可借助过孔缝合提供屏蔽效果。此外,在滤波器级以下的所有层中插入敷铜层切口,可避免 VIN 和 GND 走线之间产生寄生电容,从而为噪声电流提供绕过 CM 扼流器的路径并让步于滤波器的阻抗特性。

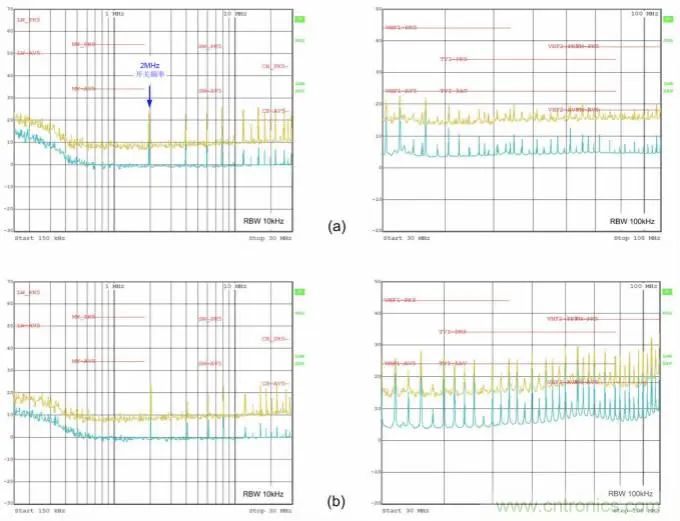

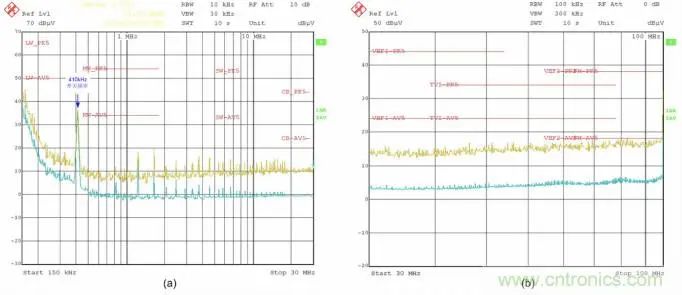

图 4:DC/DC 转换器原理图和 PCB 布局实施方案 图 5 所示为国际无线电干扰特别委员会 (CISPR) 25 针对图 4 的转换器设计在 150kHz 至 108MHz 之间进行的传导发射测量。我们提供了使用与不使用 CM 扼流器两种情况下的测量结果。使用 Rohde & Schwarz 的频谱分析仪,所得检测器扫描结果的峰值和平均值分别以黄色和蓝色表示。红色限值图象为 5 类峰值和平均值限值(峰值限值通常比平均值限值高出 20dB)。

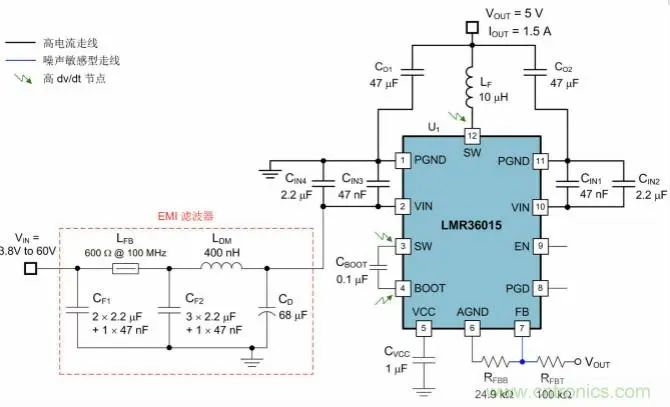

图 5:CISPR 25 在使用 CM 扼流器 (a) 与不使用 CM 扼流器 (b) 情况下进行的传导 EMI 测量 金属外壳屏蔽 另一种优化高频 EMI 性能的有效方式是添加金属外壳屏蔽层,从而阻挡辐射电场。外壳通常由铝制成,采用框架(敞开式)或封闭式设计实施方案。屏蔽外壳可覆盖除 EMI 滤波器之外的所有功率级元器件,外壳与 PCB 上的 GND 相连,基本形成了一个带有 PCB 接地平面的法拉第笼。 这使得从开关单元到 EMI 滤波器或长输入线连接(也用作天线)的辐射噪声耦合显著减少。当然,这会产生额外的元器件和装配成本,导致散热管理和散热测试的难度增加。铝电解电容的外壳也可以提供电场屏蔽,为实现此目的,可在电路板上针对性地放置该电容。 DC/DC 转换器案例研究 图 6 为 60V、1.5A 单片式集成同步降压转换器电路的原理图,该电路通过多项功能实现最佳 EMI 性能。该原理图还显示了一个两级 EMI 输入滤波器级,旨在满足汽车或噪声敏感型工业应用的 EMI 规范。为了帮助实现最佳的 PCB 布局,原理图中将高电流走线(VIN、PGND、SW 连接)、噪声敏感型网络 (FB) 和高 dv/dt 电路节点(SW、BOOT)突出显示。

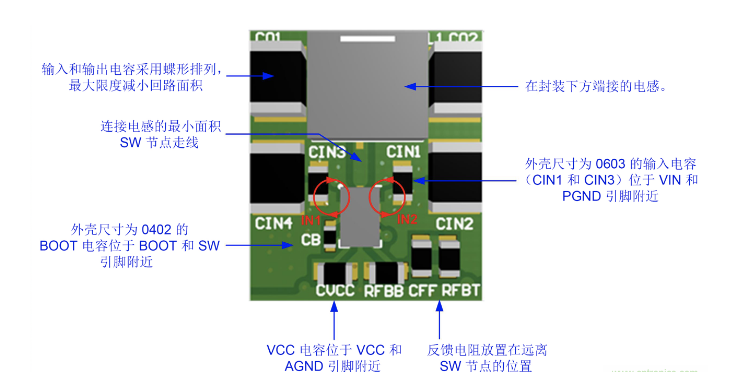

图 6:采用 EMI 优化型封装和引脚布局的 DC/DC 转换器。内置一个两级 EMI 输入滤波器 a. 引脚布局设计 图 6 所示的转换器 IC 优势在于,其 VIN 和 PGND 采用对称且均衡的引脚排布。该转换器利用两个并联的输入回路使寄生回路电感成功减半。上述回路在 PCB 布局中标记为“IN1”和“IN2”,如图 7 所示。两个外壳尺寸为 0402 或 0603 的小型电容(在图 6 中分别标记为 CIN1 和 CIN3)放置在尽可能靠近 IC 的位置,最大限度减小输入回路面积。两个回路中的环流产生相反的磁矩,消除 H 场并降低有效电感。为了进一步降低寄生电感,PCB 第 2 层(紧靠顶层电源电路的下方)的 IN1 和 IN2 回路下方设有返回电流的连续接地平面,可使场效应自行消除。 在电感两侧各使用一个陶瓷输出电容(COUT1 和 COUT2)同样能够优化输出电流回路。在输出端引出两个并联的接地返回路径可以将返回电流分成两部分,有助于减弱“地弹反射”效应。

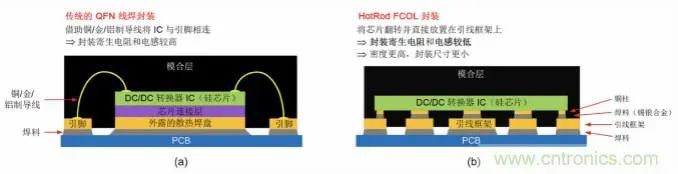

图 7:仅部署在 PCB 顶层的功率级布局 SW 引脚位于 IC 中心,因此辐射电场会由 IC 两侧相邻的 VIN 和 PGND 引脚屏蔽。GND 平面覆铜区可对将 IC 的 SW 引脚连接到电感端子的多边形覆层施加屏蔽。SW 和 BOOT 的单层布局意味着 PCB 的底侧不会有 dv/dt 较高的过孔。这样可以避免在 EMI 测试期间,电场与基准接地平面耦合。 b. 封装设计 与优化的引脚排布类似,电源转换器 IC 封装设计也是改善 EMI 信号的关键属性。例如,德州仪器 (TI) 的 HotRodÔ 封装技术采用引线框上倒装芯片 (FCOL) 的方式,规避了功率器件线焊导致封装寄生电感过高的情况。如图 8 所示,IC 以上下翻转的形式放置,IC 上的铜柱(也称为凸点或支柱)直接焊接到引线框架。这种构造方法能够提升密度并较薄的外型,因为每个引脚都与引线框架直接相连。从 EMI 角度来看,最重要的一点是,与传统线焊封装相比,HotRod 封装降低了封装的寄生电感。

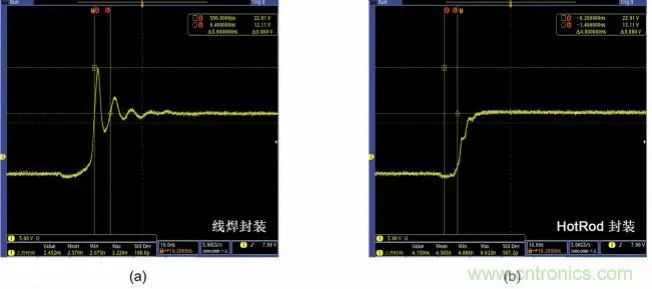

图 8:QFN 线焊封装 (a) 和 HotRod FCOL (b) 封装的结构对比 HotRod 封装不仅可以在开关换向(50MHz 至 200MHz 频率范围)期间减少振铃,还可以降低导通和开关损耗。图 9 所示为开关节点电压振铃随之得到改善的情况。图 8 所示为图 6 中的转换器在 150kHz 至 108MHz 下测得的传导发射。测量结果符合 CISPR 25 5 类要求。

图 9:使用传统线焊封装的转换器 (a) 和 HotRod FCOL 转换器 (b) 时的开关节点电压波形

图 10:CISPR 25 传导发射测量结果,(a) 频率范围为 150kHz 至 30MHz,(b) 频率范围为 30MHz 至 108MHz 总结 在本文中,我讨论了使用电源转换器 IC 的 DC/DC 稳压器电路可以采用的 EMI 抑制技术。减弱 EMI 的 PCB 布局步骤包括尽量减小布局中的电流“热回路”面积、避免阻断电流路径、采用具有内部接地平面的四层 PCB 结构实现屏蔽(屏蔽效果远超双层 PCB),以及通过尽量减小开关节点覆铜区域面积来降低电场辐射耦合。 转换器封装类型是一项重要的选择标准,新一代器件的开关节点振铃和引脚设计得到显著提升,有助于实现最优的电容放置方案。从输入滤波的角度而言,抑制低频噪声(通常小于 10MHz)相对容易,使用传统的 LC 滤波器级即可实现。然而,抑制高频噪声(10MHz 以上)通常需要额外使用 CM 扼流器和/或铁氧体磁珠滤波器级。焊接到 PCB 接地平面的金属外壳屏蔽层也能有效减轻高频发射。 在本系列文章的下一部分中,我将探讨使用控制器驱动分立式功率 MOSFET 的 DC/DC 稳压器电路适用的 EMI 抑制技术。根据 EMI 进行分析,这些技术更具挑战性。

————本文内容选自电子元件技术网站,欢迎关注

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

EMC寄语:随着时代的发展,越来越多的电子、电气设备或系统产品都需要进行检验检测,其中EMC测试是必备的检验检测指标之一。但EMC测试项目费用较贵,EMC实验室造价昂贵,绝大部分测量设备又需要采用进口设备,导致很少检验检测机构有能力建造EMC实验室。产品的EMC性能是设计阶段赋予的,一般电子产品设计时如果不考虑EMC因素,就会很容易导致EMC测试失败,以致不能通过相关EMC法规的测试或认证。例如,产品设计研发工程师们根据需求,设计出效果良好的滤波电路,置入产品I/O(输入/输出)接口的前级,可使因传导而进入系统的干扰噪声消除在电路系统的入口处;设计出隔离电路(如变压器隔离和光电隔离等)解决通过电源线、信号线和地线进入电路的传导干扰,同时阻止因公共阻抗、长线传输而引起的干扰;设计出能量吸收回路,从而减少电路、器件吸收的噪声能量;通过选择元器件和合理安排的电路系统,使干扰的影响减少。

EMC技能:整改小技巧

1、150kHz-1MHz,以差模为主,1MHz-5MHz,差模和共模共同起作用,5MHz 以后基本上是共模。差模干扰的分容性藕合和感性藕合。一般1MHz以上的干扰是共模,低频段是差摸干扰。用一个电阻串个电容后再并到Y电容的引脚上,用示波器测电阻两引脚的电压可以估测共模干扰。2、保险过后加差模电感或电阻。3、小功率电源可采用PI型滤波器处理(建议靠近变压器的电解电容可选用较大些)。4、前端的π型EMI零件中差模电感只负责低频EMI,体积别选太大(DR8太大,能用电阻型式或DR6更好)否则幅射不好过,必要时可串磁珠,因为高频会直接飞到前端不会跟着线走。5、传导冷机时在0.15MHz-1MHz超标,热机时就有7dB余量。主要原因是初级BULk电容DF值过大造成的,冷机时ESR比较大,热机时ESR比较小,开关电流在ESR上形成开关电压,它会压在一个电流LN线间流动,这就是差模干扰。解决办法是用ESR低的电解电容或者在两个电解电容之间加一个差模电感。6、测试150kHz总超标的解决方案:加大X电容看一下能不能下来,如果下来了说明是差模干扰。如果没有太大作用那么是共模干扰,或者把电源线在一个大磁环上绕几圈, 下来了说明是共模干扰。如果干扰曲线后面很好,就减小Y电容,看一下布板是否有问题,或者就在前面加磁环。7、可以加大PFC输入部分的单绕组电感的电感量。8、PWM线路中的元件将主频调到60kHz左右。9、用一块铜皮紧贴在变压器磁芯上。10、共模电感的两边感量不对称,有一边匝数少一匝也可引起传导150kHz-3MHz超标。11、一般传导的产生有两个主要的点:200kHz和20MHz左右,这几个点也体现了电路的性能;200kHz左右主要是漏感产生的尖刺;20MHz左右主要是电路开关的噪声。处理不好变压器会增加大量的辐射,加屏蔽都没用,辐射过不了。

12、将输入BUCk电容改为低内阻的电容。13、对于无Y-CAP电源,绕制变压器时先绕初级,再绕辅助绕组并将辅助绕组密绕靠一边,后绕次级。14、将共模电感上并联一个几k到几十k电阻。15、将共模电感用铜箔屏蔽后接到大电容的地。16、在PCB设计时应将共模电感和变压器隔开一点以免互相干扰。17、保险套磁珠。18、三线输入的将两根进线接地的Y电容容量从2.2nF减小到471。19、对于有两级滤波的可将后级0.22uFX电容去掉(有时前后X电容会引起震荡) 。20、对于π型滤波电路有一个BUCk电容躺倒放在PCB上且靠近变压器此电容对传导150kHz-2MHz的L通道有干扰,改良方法是将此电容用铜泊包起来屏蔽接到地,或者用一块小的PCB将此电容与变压器和PCB隔开。或者将此电容立起来, 也可以用一个小电容代替。21、对于π型滤波电路有一个BUCk电容躺倒放在PCB上且靠近变压器此电容对传导150kHz-2MHz的L通道有干扰,改良方法是将此电容用一个1uF/400V或者说0.1uF/400V电容代替, 将另外一个电容加大。22、将共模电感前加一个小的几百uH差模电感。23、将开关管和散热器用一段铜箔包绕起来,并且铜箔两端短接在一起,再用一根铜线连接到地。24、将共模电感用一块铜皮包起来再连接到地。25、将开关管用金属套起来连接到地。26、加大X2电容只能解决150kHz左右的频段,不能解决20MHz以上的频段,只有在电源输入加以一级镍锌铁氧体黑色磁环,电感量约50uH-1mH。27、在输入端加大X电容。28、加大输入端共模电感。29、将辅助绕组供电二极管反接到地。30、将辅助绕组供电滤波电容改用瘦长型电解电容或者加大容量。31、加大输入端滤波电容。32、150kHz-300kHz和20MHz-30MHz这两处传导都不过,可在共模电路前加一个差模电路。也可以看看接地是否有问题,该接地的地方一定要加强接牢,主板上的地线一定要理顺,不同的地线之间走线一定要顺畅不要互相交错的。33、在整流桥上并电容,当考虑共模成分时,应该邻角并电容,当考虑差模成分时,应该对角并电容。34、加大输入端差模电感。

2、产品电磁兼容骚扰源有:

1、设备开关电源的开关回路:骚扰源主频几十kHz到百余kHz,高次谐波可延伸到数十MHz。 2、设备直流电源的整流回路:工频线性电源工频整流噪声频率上限可延伸到数百kHz;开关电源高频整流噪声频率上限可延伸到数十MHz。 3、电动设备直流电机的电刷噪声:噪声频率上限可延伸到数百MHz。 4、电动设备交流电机的运行噪声:高次谐波可延伸到数十MHz。 5、变频调速电路的骚扰发射:开关调速回路骚扰源频率从几十kHz到几十MHz。 6、设备运行状态切换的开关噪声:由机械或电子开关动作产生的噪声频率上限可延伸到数百MHz。7、智能控制设备的晶振及数字电路电磁骚扰:骚扰源主频几十kHz到几十MHz,高次谐波可延伸到数百MHz。8、微波设备的微波泄漏:骚扰源主频数GHz。 9、电磁感应加热设备的电磁骚扰发射:骚扰源主频几十kHz,高次谐波可延伸到数十MHz。 10电视电声接收设备的高频调谐回路的本振及其谐波:骚扰源主频数十MHz到数百MHz,高次谐波可延伸到数GHz。11、信息技术设备及各类自动控制设备的数字处理电路:骚扰源主频数十MHz到数百MHz(经内部倍频主频可达数GHz),高次谐波可延伸到十几GHz。

编辑:黄飞

-

开关电源电磁干扰的抑制方法2026-03-12 664

-

变频器电磁干扰抑制措施2026-02-07 390

-

开关电源的共模干扰抑制技术-开关电源共模电磁干扰(EMI)对策详解2025-03-27 796

-

电磁干扰的防护技术 EMI电磁干扰对通信设备的影响2024-11-20 3985

-

如何抑制MEI电磁干扰传导?如何选择EMI滤波器?2023-11-29 1696

-

采用集成FET设计抑制电磁干扰EMI的实用电路技术2023-03-29 3500

-

抑制传导和辐射电磁干扰 (EMI) 的实用指南和示例2022-11-09 683

-

抑制电磁干扰 (EMI) 的实用电路技术2021-12-29 3454

-

抑制电磁干扰 (EMI) 的实用电路技术资料下载2021-04-04 1167

-

抑制电磁干扰的实用电路技术2021-03-01 1420

-

采用频率抖动技术减小EMI 为抑制开关电源电磁干扰新思路2017-09-14 1063

-

电磁干扰(EMI)滤波器电路2009-10-12 9193

-

开关电源电磁干扰(EMI)机理及新的抑制方法2009-07-15 2140

-

电磁干扰抑制技术概述2006-04-16 1642

全部0条评论

快来发表一下你的评论吧 !