内联重布线层(IRDL)及其主要功能简介

描述

随着移动设备和可穿戴设备的日益普及,移动存储器的需求也在稳步提升。对于移动设备来说,便携性是最重要的考量因素,低功耗和超薄封装(PKG)技术也由此成为半导体行业不可或缺的要素。

内联重布线层(Inline Re-distribution Layer,简称 IRDL)技术是一种先进的FAB技术,使用由绝缘层和铝组成的额外金属层来形成布线,使IO焊盘能够在必要时自由地重新放置到封装(PKG)引线键合位置。这项技术使得芯片间的键合更薄、工艺更简单。此外,内联重布线层(IRDL)技术是重布线层(RDL)技术之一。顾名思义,这项技术的命名是因为其整个过程都在FAB内部进行,这与封装重布线层技术(PKG RDL)有所不同。

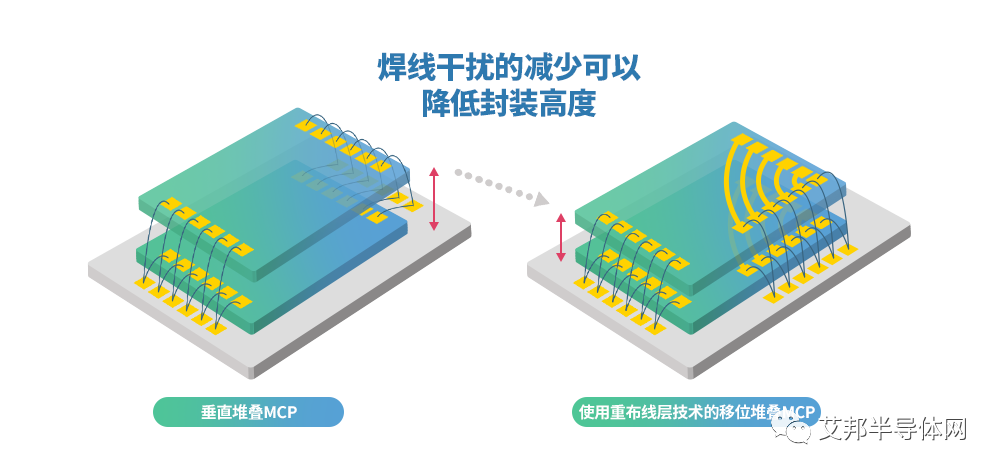

图1. 垂直堆叠MCP与移位堆叠MCP

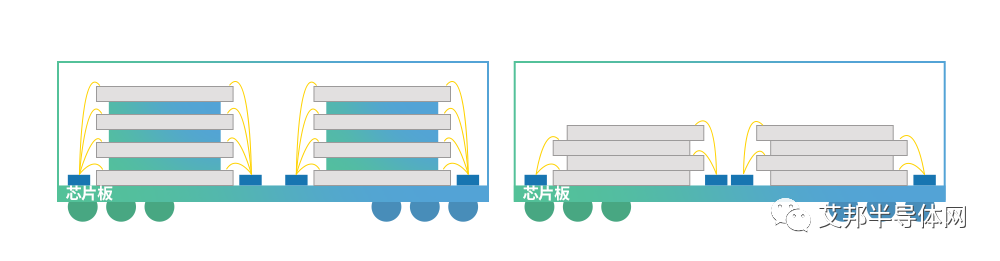

图2. 图1的横断面视图

上图展示了芯片的两种多芯片封装(MCP)1*方法。左侧是目前通用的“垂直堆叠MCP”方法,其中上部芯片垂直堆叠在下部芯片的焊盘上;右侧是“使用重布线层(RDL)技术的移位堆叠MCP”方法,可以避开焊盘。垂直堆叠MCP方法往往会导致导线干扰问题和导线与芯片之间短路问题,而新的移位堆叠MCP方法可以很好地避免这些问题。这种新的堆叠方法可以减小上层芯片和下层芯片之间的间隙,更容易满足客户对厚度的要求。

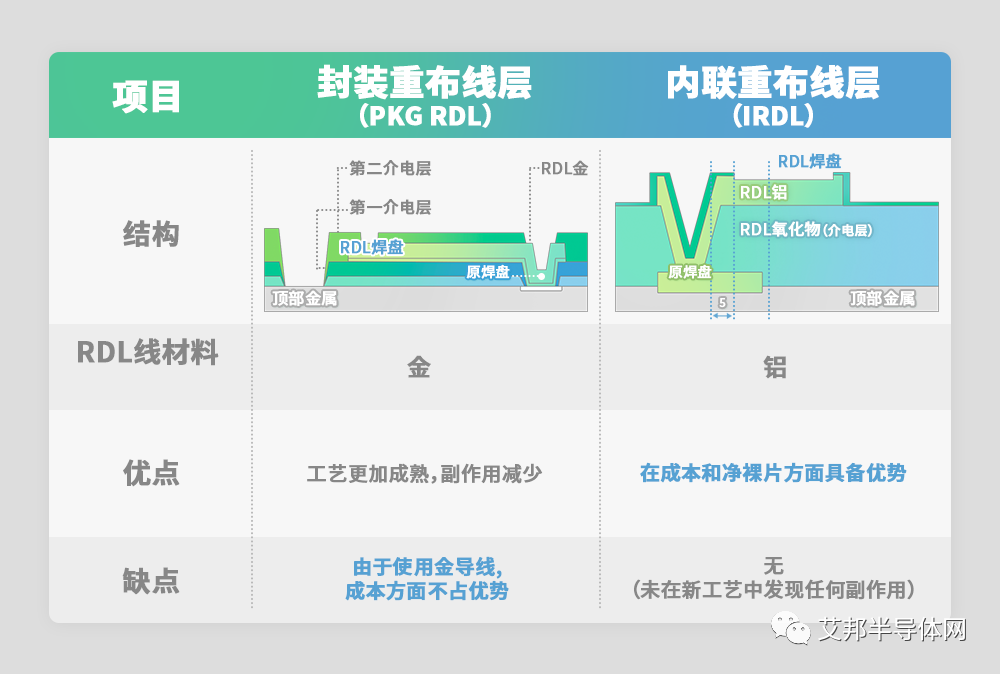

现有封装重布线层(RDL)技术与内联重布线层(IRDL)技术的比较

封装重布线层(PKG RDL)技术和内联重布线层(IRDL)技术之间的主要区别在于结构形成方法,所以接下来,我们需要更加深入地了解内联重布线层(IRDL)技术的优势。

图3.封装重布线层(PKG RDL)技术与内联重布线层(IRDL)技术的比较 封装重布线层(PKG RDL)的结构形成方法大致分为两个过程:FAB输入和FAB输出。

FAB输入过程是在仅打开焊盘的状态下,用绝缘材料覆盖顶部金属。然后,在FAB输出过程中,使用第一介电层将重布线层线与晶圆顶部的绝缘材料分开,并使用金作为导线。之后,使用第二介电层覆盖导线顶部。

另一方面,内联重布线层(IRDL)方法使用绝缘材料覆盖顶部金属并形成过孔(VIA)以打开焊盘。

然后,使用铝作为导线,这就是与封装重布线层(PKG RDL)方法的不同之处。最后,在顶部涂上绝缘材料。

内联重布线层(IRDL)方法与封装重布线层(PKG RDL)方法的目的相同,均旨在重新放置焊盘。但是,随着FAB内部流程的改进,内联重布线层(IRDL)技术在重布线层(RDL)技术的基础上拥有三项优势:

• 首先,由于电路可以放置在焊盘下方,因此净裸片的性能得以改善;

• 其次,使用铝代替金可以将整个工艺的成本降低高达30%;

• 最后,电路设计人员可以借助重布线层(RDL)技术来增强电源网格²*,由此提升芯片性能。

较小的芯片可将电路置于焊盘下方,从而提升净裸片的性能

当使用现行封装重布线层(PKG RDL)结构时,由于顶部的金属过薄(小于1um),因此在探测和键合期间经常会发生许多与焊盘相关的问题。

使用内联重布线层(IRDL)结构时,顶部金属的厚度可以达到近10um的水平,足以承受探测和键合过程中产生的应力,使得电路可以放置在焊盘下方。这样的结构可以缩小芯片尺寸,由此改善净裸片的性能。

使用内联重布线层(IRDL)技术提升配电网络(PDN)性能

使用内联重布线层(IRDL)技术的增强型电源网格可以提升配电网络(power distribution network,简称 PDN)性能,更好地改进芯片性能。

如果不借助内联重布线层(IRDL),则只能使用芯片现有的金属布线来提升配电网络性能,但是这样的做法会导致远离焊盘的区域出现配电网络性能下降的问题。这种方法对于配电网络性能的提升作用非常有限。

另一方面,在使用内联重布线层(IRDL)时,重布线层(RDL)的特性决定着传递的电阻值较低,配电网络性能由此得到大幅提升。因此,可以通过使用内联重布线层(IRDL)技术的方法来提升芯片的性能。

内联重布线层(IRDL)技术:未来设备的先驱

内联重布线(IRDL)层技术能够降低流程成本,可以在不损害现有芯片架构的前提下,将IO焊盘重新放置到封装所需的位置。

内联重布线层(IRDL)技术有助于企业更好地适应移动设备的未来发展方向——更轻更薄的产品。这项元件技术的诞生对于整个行业来说有着至关重要的意义,因为它可以缩小芯片尺寸,增强芯片性能,推动净裸片的发展。

1*MCP:多芯片封装技术是一种将两个以上的半导体芯片堆叠到一个封装中,在增加容量和提升性能的同时,减少占用空间的技术。

这项技术主要用于智能手机和平板电脑等轻薄便携设备。借助内联重布线层(IRDL)技术,企业可以在多芯片封装过程中制造出更轻薄的芯片。

2*电源网格(Power Mesh):由多金属层上的电线组成的网络。

审核编辑:刘清

-

滤波器的主要功能和作用科普2024-01-25 10035

-

电源滤波器的主要功能和作用2023-12-25 2573

-

变压器的主要功能2023-09-04 8583

-

直线导轨的主要功能2023-07-26 2109

-

简述增益模块放大器的主要功能2023-07-06 2318

-

TMF框架是什么?其主要功能有哪些2022-02-23 2236

-

电池管理系统的主要功能包括哪些2021-09-08 4060

-

TIMx简介及主要功能2021-08-18 1884

-

ECC是什么?有什么主要功能?2021-06-21 3632

-

MusrLicManage的主要功能2020-12-16 2564

-

PWM发生器的主要功能2020-12-04 3387

-

请问TIMx有哪些主要功能?2020-11-09 2232

-

mac层的主要功能介绍2018-03-15 88311

-

电话机的主要功能2009-12-31 1390

全部0条评论

快来发表一下你的评论吧 !