т║ћућеугћУ«░|STM32MP1 у│╗тѕЌ MPU уџё DDR жЁЇуй«

ТЈЈУ┐░

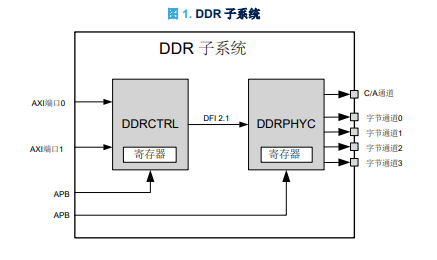

ТюгТќЄТАБТЈЈУ┐░тюе STM32MP1 у│╗тѕЌ MPU С║ДтЊЂСИіжЁЇуй« DDR тГљу│╗у╗Ъ№╝ѕDDRSS№╝ЅТЅђжюђуџёТхЂуеІтњїТГЦжфцсђѓ┬а

┬а

У«Йт«џ DDR ТјДтѕХтЎе№╝ѕDDRCTRL№╝ЅсђЂPHY ТјЦтЈБ№╝ѕDDRPHYC№╝Ѕтњї SDRAM ТеАт╝Јт»ётГўтЎеуџётцџСИфтЈѓТЋ░С╗ЦтЈіУ«Йуй«т«їТѕљ DDRSS жЁЇуй«сђѓ┬а

┬а

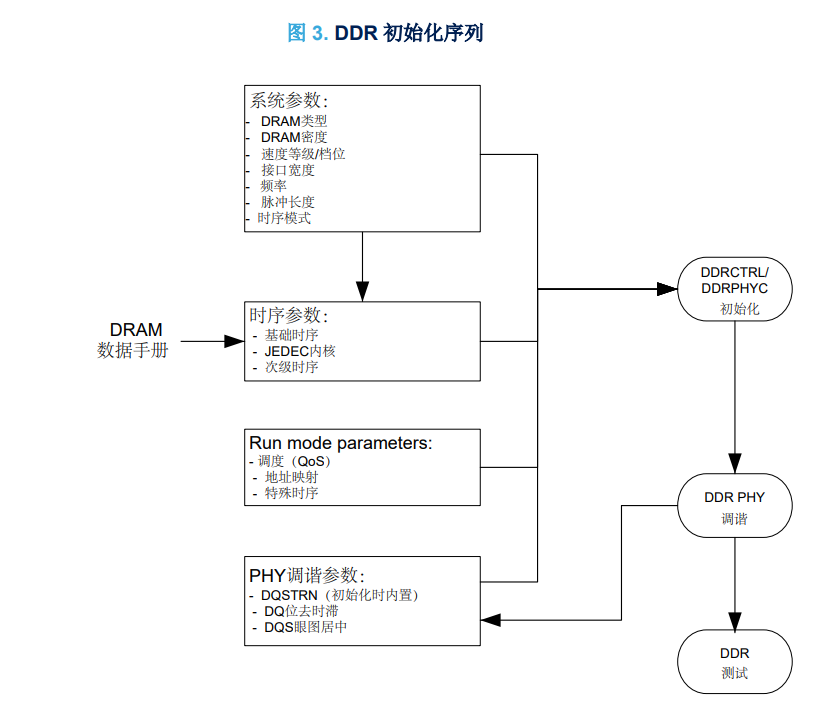

Та╣ТЇ« DDR у▒╗тъІсђЂDDR тцДт░ЈсђЂDRAM ТІЊТЅЉсђЂУ┐љУАїТЌХжЌ┤жбЉујЄтњї SDRAM тЎеС╗ХТЋ░ТЇ«ТЅІтєїтЈѓТЋ░уА«т«џУ┐ЎС║ЏтЈѓТЋ░сђѓТЅђТюЅУ┐ЎС║ЏтЈѓТЋ░т┐ЁжА╗тюетѕЮтДІтїќт║ЈтѕЌТюЪжЌ┤У«Йт«џсђѓ┬а

┬а

STM32CubeMX DDR ТхІУ»ЋтЦЌС╗ХСй┐ућеуЏ┤УДѓуџёжЮбТЮ┐тњїУЈютЇЋжџљУЌЈС║єСИјуА«т«џТГБуА«тЈѓТЋ░тњїтѕЮтДІтїќтљ»тіеуЏИтЁ│уџётцЇТЮѓТђД№╝ѕУ»итЈѓУђЃ[6]№╝ЅсђѓСИ║С║єт┐ФжђЪУ«Йуй«УдЂУ┐љУАїуџё DDRSS№╝їућеТѕитЈфжюђТЈљСЙЏтЙѕт░ЉтЄаСИфУЙЊтЁЦтЈѓТЋ░тЇ│тЈ»т«їТѕљжЁЇуй«сђѓтЈ»С╗ЦСй┐ућеСИђС║ЏжФўу║ДућеТѕиТеАт╝ЈтњїуЅ╣Т«ітіЪУЃй№╝ѕтйЊт«ЃС╗гт»╣С║јт║ћућеУђїУеђтЇЂтѕєжЄЇУдЂТЌХ№╝Ѕсђѓ┬а

┬а

тюеу│╗у╗Ътљ»тіежўХТ«х№╝їСИ║С║єС╝ўтїќТЌХт║ЈУБЋжЄЈ№╝їТћ»ТїЂтцџуДЇ PHY У░ЃУ░љсђѓтЈ»С╗ЦСй┐уће STM32CubeMX тљ»тіеУ┐ЎС║ЏУ░ЃУ░љсђѓPHY У░ЃУ░љу╗ЊТъютЈ»С╗ЦС┐ЮтГўт╣Хтюетљју╗ГтєитцЇСйЇТЌХТЂбтцЇсђѓ┬а

┬а

тюетљ»тіежўХТ«х№╝їућеТѕитЈ»С╗ЦУ┐љУАїтцДжЄЈТхІУ»ЋтЦЌС╗ХсђѓУ┐ЎС║ЏТхІУ»ЋтЈ»С╗ЦСй┐уће STM32CubeMX тљ»тіе№╝їт╣ХућеС║јуА«У«ц DDR жЁЇуй«уџёуе│тЂЦТђДсђѓ

┬а

┬а

┬а

┬а

уЏ«тйЋжбёУДѕ

┬а

┬а

┬а

1 ТдѓУ┐░

2 DDR тГљу│╗у╗ЪтѕЮтДІтїќтњїжЁЇуй«

3 жЁЇуй«тЈѓТЋ░

4 жЁЇуй«т║ЈтѕЌтњїтЈѓТЋ░┬а

5 DDR3/3L жЁЇуй«

6 LPDDR2 жЁЇуй«

7┬аLPDDR3 жЁЇуй«

8┬аSTM32CubeMX уџё DDR ТхІУ»Ћ

9 жФўу║ДућеТѕижЁЇуй«

┬а

┬а

1. ТдѓУ┐░

┬аТюгТќЄТАБжђѓућеС║ј STM32MP1 у│╗тѕЌтЪ║С║ј Armуџё MPUсђѓ

┬а

2.DDR тГљу│╗у╗ЪтѕЮтДІтїќтњїжЁЇуй«

┬аDDR тГљу│╗у╗ЪтїЁТІг DDRCTRL тњї DDRPHYC№╝ѕтЈѓУДЂСИІтЏЙ№╝Ѕсђѓ┬а

┬а

DDRCTRL Тћ»ТїЂтюеТГБтИИТЊЇСйюТюЪжЌ┤жђџУ┐ЄтЉйС╗цтњїтѕиТќ░У░Ѓт║дУ┐ЏУАї DDR тЉйС╗цУ░Ѓт║дсђѓ┬а

┬а

DDRPHYC Тў»СИђуДЇ DDR PHY ТјЦтЈБ№╝їтЁиТюЅУ┐ъТјЦ DDRCTL уџё DFI ТјЦтЈБ[7]тњїтГЌУіѓжђџжЂЊТъХТъё№╝їжђѓтљѕУ┐ъТјЦжбЉујЄСИЇУХЁУ┐Є 533MHz уџё DDR3/3L тњї LPDDR2/3сђѓ┬а

┬а

DDRPHYC т«їтЁеТћ»ТїЂтЁиТюЅтцџСИф PHY У░ЃУ░љжђЅжА╣№╝ѕтєЁуй«№╝Ѕуџё DDR тѕЮтДІтїќсђѓ

┬а

DDRPYC тїЁтљФ BIST т╝ЋТЊј№╝їућеС║јТћ»ТїЂУй»С╗ХжЕ▒тіеуџёУ░ЃУ░љсђѓ

┬а

┬а

┬а

┬а2.1 DDRSS тњї SDRAM тѕЮтДІтїќ

┬а

тЎеС╗ХТа╣ТЇ« SDRAM тљ»тіет║ЈтѕЌт»╣ућхТ║љсђЂТЌХжњЪтњїтцЇСйЇУ┐ЏУАїтєЁжЃеТјњт║Јсђѓ┬а

┬а

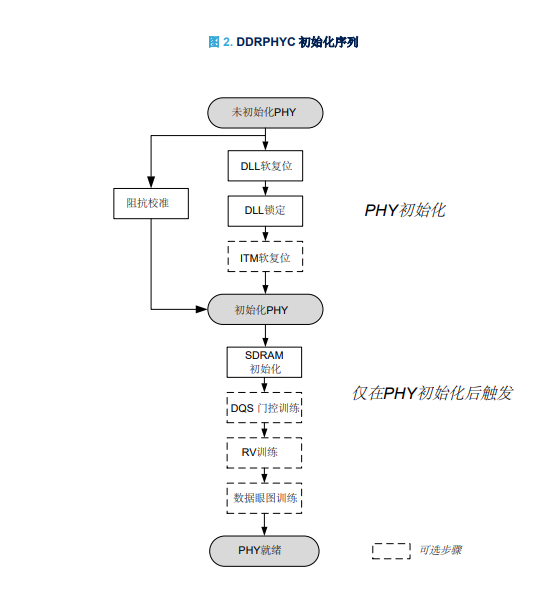

тЏЙ 2 ТЅђуц║уџё PHY тѕЮтДІтїќт║ЈтѕЌућ▒ DDRPHYC уЅЕуљєт«ъућеТеАтЮЌ№╝ѕPUB№╝ЅТјДтѕХсђѓУ┐ЎСИђтЪ║С║ј PUB уџётѕЮтДІтїќт║ЈтѕЌтюеDDRPHYC С╗јтцЇСйЇуіХТђЂжЄіТћЙтљјтљ»тіе№╝їт╣ХТа╣ТЇ« DDRPHYC.PIR т»ётГўтЎеУ┐ЏУАїТјњт║Јсђѓ┬а

┬а

тѕЮтДІтїќт║ЈтѕЌтїЁТІгС╗ЦСИІТГЦжфц№╝џ┬а

1.DDRCTRL тњї DDRPHYC тѕЮтДІтїќтїЁТІгтєЁжЃеТЌХт║ЈТеАтЮЌ№╝ѕITM№╝ЅтцЇСйЇС╗ЦтЈі DLL тцЇСйЇтњїжћЂт«џ┬а

┬а

2. DDRPHYC I/O тѕЮтДІТаАтЄє№╝ѕZCAL№╝Ѕ№╝їСИј DLL жћЂт«џтљїТЌХтљ»тіе┬а

┬а

3. жђџУ┐ЄТеАт╝Јт»ётГўтЎетєЎтЁЦтњїТаАтЄєтЉйС╗цТЅДУАї SDRAM тѕЮтДІтїќ┬а

┬а

4. тєЁуй« DQS жЌеТјДУ«Гу╗Ѓ№╝ѕDQSTRN№╝Ѕ┬а

┬а

ТЈљуц║ №╝џ

Рђб тюе SSTL ТеАт╝ЈСИІСИ║ТЅђТюЅ SDRAM У«Йуй« DDRPHYC I/Oсђѓ┬а

Рђб DQS жЌеТјДУ«Гу╗ЃТў»тЈ»жђЅуџёсђѓСйєТў»№╝їт╗║У««тюеТ»ЈТгАтѕЮтДІтїќТЌХУ┐љУАїтєЁуй« DQS жЌеТјДУ«Гу╗Ѓсђѓ

┬а

┬а

┬а2.2┬аDDRCTRL жЁЇуй«┬а

┬а

тцДтцџТЋ░ DDRCTRL т»ётГўтЎеТў»жЮЎТђЂуџё№╝їт╣Хтюе DDRCTRL С╗јтцЇСйЇуіХТђЂжЄіТћЙтњї AXI уФ»тЈБСй┐УЃйтЅЇтіаУййсђѓУ┐ЎТў»тюе DDR Уй»С╗ХжЕ▒тіетЎеуџёТћ»ТїЂСИІт«ъуј░уџёсђѓ

┬а

тюе DDRPHYC тњї DDCTRL т«їТѕљтѕЮтДІтїќтљј№╝їDDR тГљу│╗у╗Ът░▒у╗ф№╝їСй┐УЃй AXI уФ»тЈБТў»ТюђтљјСИђСИфТГЦжфцсђѓ┬а

┬а

жђџУ┐ЄС╗ј STM32CubeMX DDR жЮбТЮ┐жђЅТІЕуџёУЈютЇЋ/жђЅжА╣ТЈљСЙЏуџёТъЂт░ЉС┐АТЂ»уА«т«џ DDRCTRL тњї DDRPHYC т»ётГўтЎеуџёжЁЇуй«сђѓ┬а

┬а

уёХтљј№╝їDDRSS жЁЇуй«УбФС┐ЮтГўт╣ХТЂбтцЇтѕ░ DDRCTRL тњї DDRPHYC т»ётГўтЎе№╝їућеС║јтљју╗ГуџётцЇСйЇтњїТГБтИИТЊЇСйюсђѓ

┬а

┬а

┬а2.3 DDR жЁЇуй«

┬а

жЁЇуй« DDR ТЅђжюђуџёТГЦжфцтдѓСИІ№╝џ┬а

1.СИ║ DDRCTRL тњї DDRPHYC т»ётГўтЎеуА«т«џт╣ХУ«Йт«џтљѕжђѓтђ╝сђѓ┬а

┬а

2. тљ»тіе DDRCTRL тњї DDRPHYC тѕЮтДІтїќт║ЈтѕЌсђѓ┬а

┬а

3. тљ»тіетЁиТюЅтЈѓТЋ░С┐ЮтГўтњїТЂбтцЇтіЪУЃйуџё DDR У░ЃУ░љ№╝ѕтЈ»жђЅ№╝Ѕсђѓ┬а

┬а

4. тљ»тіе DDR ТхІУ»Ћ№╝ѕтЈ»жђЅ№╝Ѕсђѓт«їТЋ┤жЁЇуй«ТхЂуеІтњїтЈѓТЋ░тдѓСИІтЏЙТЅђуц║

ТїЅуЁДугг 3 Уіѓ жЁЇуй«тЈѓТЋ░СИГуџёу▒╗тъІТЈЈУ┐░жЁЇуй«тЈѓТЋ░сђѓ

┬а

┬а

┬а2.4 DDR PHY У░ЃУ░љ

┬а

жЎцС║єСй┐ућет╝║тѕХ DQS жЌеТјДУ«Гу╗Ѓ№╝ѕDQSTRN№╝ЅуА«т«џУ»╗УёЅтє▓ТюЪжЌ┤ DQS жЌеТјДуџёТюђСй│СйЇуй«№╝їDDRPHYC У┐ўТћ»ТїЂСИцуДЇУ»╗тЈќТЌХт║ЈС╝ўтїќ№╝їтЇ│ PHY У░ЃУ░љсђѓ┬а

┬а

С╗ЦСИІС╗ј STM32CubeMX жЕ▒тіеуџёУй»С╗ХСЙІуеІТћ»ТїЂ PHY У░ЃУ░љ№╝їС╗ЦС╝ўтїќУ»╗ТЌХт║ЈУБЋжЄЈ№╝џ┬а

Рђб DQS жЌеТјДУ«Гу╗Ѓ№╝ѕтЈ»тюе DDR PHY У░ЃУ░љТюЪжЌ┤С╗ЦС║цС║њТќ╣т╝Јтљ»тіеуџёУй»С╗Х№╝Ѕ┬а

Рђб DQ СйЇтј╗ТЌХТ╗ъ№╝їС╗ЦУАЦтЂ┐ DQ СйЇжђџжЂЊУ»╗тЈќт╗ХУ┐Ъ┬а

Рђб DQS ую╝тЏЙт▒ЁСИГ№╝їућеС║јУ░ЃУіѓ DQS/DQS#т╗ХУ┐ЪС╗Цт«ъуј░ТюђСй│ DQ жЄЄТаи

┬а

т╗║У««тюеу│╗у╗ЪтѕЮтљ»жўХТ«хУ┐ЏУАї PHY У░ЃУ░љсђѓСИ║Т»ЈСИфтГЌУіѓжђџжЂЊТЅДУАїУ░ЃУ░љсђѓућ▒С║ј PHY У░ЃУ░љТЌХжЌ┤тЈ»УЃйУЙЃжЋ┐№╝ѕтЄатЇЂуДњ№╝Ѕ№╝їт┐ЁжА╗СИ║тљју╗ГтцЇСйЇтњї PHY тѕЮтДІтїќ№╝ѕСЙІтдѓ№╝їтюетєитцЇСйЇтњїтЙЁТю║жђђтЄ║ТЌХ№╝ЅС┐ЮтГўтњїТЂбтцЇУ░ЃУ░љтЈѓТЋ░сђѓ

┬а

ТЏ┤тцџУ»ду╗єС┐АТЂ»№╝їУ»итЈѓУДЂугг 3.4 Уіѓ PHY У░ЃУ░љсђѓ

┬а

┬а

┬а2.5┬аDDR ТхІУ»Ћ

┬а

тюежЁЇуй« DDR т╣ХСИ║С╝ўтїќТЌХт║ЈУ░ЃУ░љ PHY тљј№╝їт┐ЁжА╗жђџУ┐ЄУ┐љУАїС╗ј STM32CubeMX тљ»тіеуџётцДжЄЈТхІУ»Ћт║ЈтѕЌТБђТЪЦжЁЇуй«уџёуе│тЂЦТђДсђѓ┬а

┬а

тюетѕЮтљ»жўХТ«хСй┐уће DDR С╣ІтЅЇ, т┐ЁжА╗У┐љУАї STM32CubeMx т╗║У««уџёТЅђТюЅТхІУ»Ћтњїу║ДтѕФсђѓугг 8 Уіѓ STM32CubeMX уџё DDR ТхІУ»ЋСИГТЈЈУ┐░С║є DDR ТхІУ»ЋтњїТхІУ»ЋТхЂуеІ№╝їС╗ЦтЈіТЋЁжџюУ»іТќГтњїтцёуљєТјфТќйсђѓ┬а

┬а

DDR тГљу│╗у╗ЪтѕЮтљ»тюе DDR жЁЇуй«сђЂУ░ЃУ░љтњїтјІтіЏТхІУ»ЋТѕљтіЪтљјт«їТѕљсђѓС┐ЮтГўжЁЇуй«тЈѓТЋ░ућеС║јТГБтИИУ┐љУАїТеАт╝ЈтѕЮтДІтїќтњї DDR run ТеАт╝Јсђѓ

┬а

┬а 3.жЁЇуй«тЈѓТЋ░

┬аDDR жЁЇуй«тЈѓТЋ░№╝ѕТЌаУ«║жђѓућеС║ј DDRCTRL У┐ўТў» DDRPHYC№╝ЅтЈ»тѕєСИ║С╗ЦСИІтЄау╗ё№╝џ

Рђб у│╗у╗ЪтЈѓТЋ░№╝џDDR у▒╗тъІ№╝ѕDDR3/LPDDR2/3№╝ЅсђЂТђ╗у║┐т«йт║д№╝ѕ16 СйЇ/32 СйЇ№╝ЅсђЂТЌХжњЪжбЉујЄтњїт»єт║дсђѓУёЅтє▓жЋ┐т║дтњїТЌХт║ЈТеАт╝ЈтЈќтє│С║ју│╗у╗ЪжЁЇуй«т╣Хућ▒ STM32CubeMX У«Йуй«№╝їућеТѕитЈфжюђтюе DDR жЁЇуй«жЮбТЮ┐СИГУЙЊтЁЦтЄаСИфт┐ЁтАФжА╣сђѓ┬а

┬а

Рђб ТЌХт║ЈтЈѓТЋ░№╝їТа╣ТЇ« DDR ТЌХжњЪжбЉујЄтњї SDRAM ТЋ░ТЇ«ТЅІтєїуА«т«џсђѓУ»Цу╗ётїЁТІгС╗ЦСИІтЈѓТЋ░№╝џ┬а

РђЊ тЪ║уАђТЌХт║Ј┬а

РђЊ JEDEC тєЁТаИТЌХт║Ј┬а

РђЊ ТгАу║ДТЌХт║Ј┬а

┬а

Рђб У┐љУАїТеАт╝ЈтњїуЅ╣Т«ітЈѓТЋ░№╝їСИјТђДУЃйУ░Ѓт║дсђЂтѕиТќ░ТЌХт║Јтњїтю░тЮђТўат░ёТюЅтЁ│сђѓС╗јжЁЇуй«жЮбТЮ┐СИіТјеУЇљу╗ЎућеТѕиуџёжбёт«џС╣ЅУ«Йуй«СИГжђЅТІЕУ┐ЎС║ЏтЈѓТЋ░сђѓSTM32CubeMX DDR жЁЇуй«ТЈљуц║С║єСИђС║ЏтЈѓТЋ░тњїжђЅжА╣№╝ѕСЙІтдѓ№╝їУ«Йуй«уЅ╣т«џТеАт╝ЈТѕќТЅЕт▒ЋТИЕт║дТћ»ТїЂ№╝Ѕсђѓ┬а

┬а

Рђб PHY У░ЃУ░љтЈѓТЋ░№╝їСИјтюетѕЮтДІтїќТюЪжЌ┤Сй┐ућеСИђС║Џ PHY тєЁуй«ТеАтЮЌТѕќТЅДУАїуџёУй»С╗Хт║ЈтѕЌуА«т«џуџё PHY ТЌХт║ЈТюЅтЁ│сђѓУ»Цу╗ётїЁТІгС╗ЦСИІтЈѓТЋ░№╝џ┬а

РђЊ DQS жЌеТјДУ«Гу╗Ѓ№╝ѕDQSTRN№╝Ѕ┬а

РђЊ DQ жђџжЂЊСйЇтј╗ТЌХТ╗ъу╗єТГЦжЋ┐т╗ХУ┐Ъ

РђЊ DQS ую╝тЏЙт▒ЁСИГу╗єТГЦжЋ┐т╗ХУ┐ЪPHY У░ЃУ░љу╗ЊТъютЈ»жђџУ┐Є STM32CubeMx У┐ЏУАїС┐ЮтГўтњїТЂбтцЇсђѓ

┬а

ТЏ┤тцџУ»ду╗єС┐АТЂ»№╝їУ»итЈѓУДЂ[1]сђѓ

┬а

ТюгТќЄТАБСИ╗УдЂТЈЈУ┐░тюе STM32MP1 у│╗тѕЌ MPUС║ДтЊЂ┬аСИіжЁЇуй« DDR тГљу│╗у╗Ъ№╝ѕDDRSS№╝ЅТЅђжюђуџёТхЂуеІтњїТГЦжфцсђѓућ▒С║јТќЄуФау»Єт╣ЁТюЅжЎљС╗Ёт▒Ћуц║жЃетѕєС┐АТЂ»№╝їт«їТЋ┤тєЁт«╣У»иуѓ╣тЄ╗РђюжўЁУ»╗тјЪТќЄРђЮСИІУййтјЪТќЄТАБсђѓ

┬а

жЋ┐ТїЅТЅФуаЂтЁ│Т│етЁгС╝ЌтЈи┬а

┬а

ТЏ┤тцџУхёУ«»№╝їт░йтюеSTM32

┬а

Рќйуѓ╣тЄ╗РђюжўЁУ»╗тјЪТќЄРђЮ№╝їтЈ»СИІУййтјЪТќЄТАБ

тјЪТќЄТаЄжбў№╝џт║ћућеугћУ«░|STM32MP1 у│╗тѕЌ MPU уџё DDR жЁЇуй«

ТќЄуФатЄ║тцё№╝џсђљтЙ«С┐АтЁгС╝ЌтЈи№╝џSTM32тЇЋуЅЄТю║сђЉТгбУ┐јТи╗тіатЁ│Т│е№╝ЂТќЄуФаУйгУййУ»иТ│еТўјтЄ║тцёсђѓ

-

тИдSTM32MP157 MPUуџёУ»ёС╝░ТЮ┐2023-10-09 689

-

STM32MP1у│╗тѕЌСй┐ућеСйјтіЪУђЌТеАт╝Ј2023-09-20 571

-

тюеSTM32MP1у│╗тѕЌMPUСИіжЁЇуй«DDRтГљу│╗у╗ЪТЅђжюђуџёТхЂуеІтњїТГЦжфц2023-09-07 604

-

STM32MP1у│╗тѕЌMPUуџёDDRжЁЇуй«2023-07-31 891

-

STM32MP1т║ЈтѕЌС║ДтЊЂУ┐ъТјЦMIPI┬«CSI-2ТЉётЃЈтц┤2023-03-15 8359

-

СИ║С╗ђС╣ѕSTM32MP157FAA1тюеРђюSTM32MP1у│╗тѕЌDDRтєЁтГўтИЃу║┐ТїЄтЇЌуц║СЙІРђЮСИГТ▓АТюЅу╗ѕуФ»ућхжў╗№╝Ъ2023-02-02 509

-

у▒│т░ћтЪ║С║јSTM32MP1уџёу│╗тѕЌТаИт┐ЃТеАтЮЌУ»ЦТђјС╣ѕжђЅ№╝Ъ2022-04-09 27678

-

жЏХтЪ║уАђС╣ЪУЃйт┐ФжђЪСИіТЅІSTM32MP12022-02-10 1313

-

STM32MP157у│╗тѕЌТЋЎуеІУ┐ъУйй-уАгС╗ХУ«ЙУ«Ау»Є2№╝џSTM32MP1тЙ«тцёуљєтЎеС╣ІућхТ║љу»Є2021-11-06 1124

-

STM32MP1у│╗тѕЌDDRтєЁтГўУи»ућ▒ТїЄтЇЌуц║СЙІ2021-01-13 4129

-

DHCOM STM32MP1 DHCOM STM32MP1У»ЦDHCOM STM32MP15xТў»ТѕЉС╗гуџётЈ»ТЈњТІћУ«Ау«ЌТю║ТеАтЮЌу│╗тѕЌ№╝ѕSODIMM-200№╝ЅуџёСИђжЃетѕє т«ЃжЁЇтцЄС║єТќ░уџёSTM32MP1у│╗тѕЌтцёуљєтЎе2020-05-20 873

-

тйЊSTM32жЂЄтѕ░Linux = STM32MP12020-03-01 3174

-

у▒│т░ћуДЉТіђSTM32MP1у│╗тѕЌтцёуљєтЎеС╗Іу╗Ї2019-11-26 3854

тЁежЃе0ТЮАУ»ёУ«║

т┐ФТЮЦтЈЉУАеСИђСИІСйауџёУ»ёУ«║тљД !