RA2快速设计指南 [3] 时钟电路(上)

描述

5. 时钟电路(上)

RA2 MCU具有六个振荡源。其中有五个可以用作主系统时钟源。剩下的一个专用于独立看门狗定时器。在典型系统中,主时钟由外部晶体或时钟驱动。将此输入指向内部选择器和分频器,在此进一步指向主系统时钟(ICLK)、闪存时钟、CPU时钟和外设模块时钟。此外,时钟分配也包括ADC和USB的外设时钟。有关时钟生成电路框图的信息,请参见《硬件手册》中的“时钟生成电路”一章。

每个时钟都有特定的容差和时序值。有关频率和时钟时序规范的信息,请参见《硬件手册》中“电气特性”一章的“交流特性”部分。有关各种时钟频率之间关系的信息,请参见《硬件手册》中的“时钟生成电路”一章。

表5. RA2振荡源

注:1. 仅RA2A1产品支持SDADC时钟。

2. 仅RA2A1产品支持USB时钟。

3. RA2A1产品的闪存时钟(FCLK)是独立于MOSC存在的,也可以通过MOSC、SOSC、HOCO、MOCO或LOCO生成。

4. RA2E2产品不支持。

一些产品如RA2E2不支持选择外部振荡器或外部时钟。此种情况下,主时钟的振荡源仅限于片上振荡器。

5.1 复位条件

复位后,RA2 MCU开始以中速片上振荡器(MOCO)作为主时钟源运行。复位时,默认情况下主振荡器处于关闭状态。HOCO和IWDT可能处于打开或关闭状态,具体取决于选项设置存储器中的设置(请参见后文第4节)。

5.2 时钟频率要求

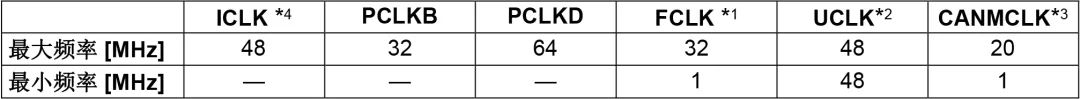

最小和最大频率如下表所示。有关详细信息,请参见《硬件手册》中“时钟生成电路”一章的“概述”部分,其中包括外部和内部时钟源规范。更多详细信息,请参见《硬件手册》中“电气特性”一章的“交流特性”部分。

表6. RA2 MCU内部时钟的频率范围

注1. 仅限RA2A1产品。对ROM或数据闪存进行编程或擦除操作时,FCLK的运行频率必须至少为1 MHz。

2. 仅限支持USB外设功能的产品。

3. 仅限支持CAN外设功能的产品。

4. RA2E1、RA2E2 和 RA2L1对 ROM 或数据闪存进行编程或擦除操作时,ICLK 的运行频率必须至少为1 MHz。

5.2.1 USB通信要求

全速USB 2.0模块(USBFS)需要48 MHz 的 USB 时钟信号(UCLK)。

对于支持USBFS模块的RA2产品,HOCO为UCLK的时钟源。因此当使用USBFS模块时,HOCO必须配置为48 MHz。

5.2.2 ROM或数据闪存的编程和擦除要求

RA2A1产品的FCLK必须至少为1 MHz才能在内部ROM和数据闪存上执行编程和擦除。

其他RA2产品的ICLK必须至少为1 MHz才能在内部ROM和数据闪存上执行编程和擦除。

5.3 降低时钟生成电路(CGC)的功耗

为了帮助节省功耗,请尽可能将所有未使用的时钟的分频器设置为最大可能值。另外,如果不使用时钟,请通过设置适当的寄存器来确保时钟已停止。下表显示了用于控制每个时钟源的寄存器。

表7. 时钟源配置寄存器

注1:RA2E2产品不支持。

5.4 写入系统时钟控制寄存器

写入系统时钟分频控制寄存器(SCKDIVCR)和系统时钟源控制寄存器(SCKSCR)中的各个位域时,应格外小心。

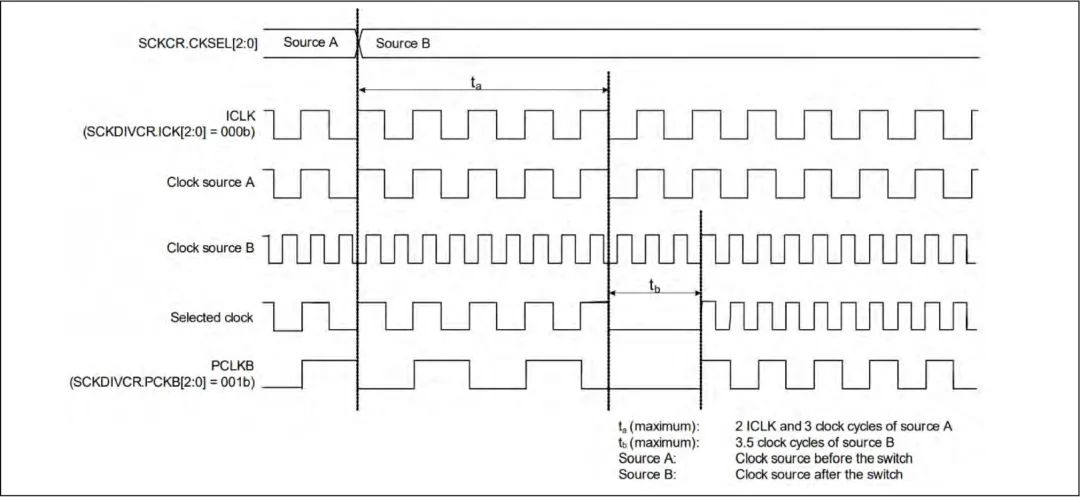

当外围模块时钟的时钟源更改为其他时钟源时,在时钟源切换期间,外围模块时钟周期会变长。详见图8。因此,必须在指令处理中增加延迟,以确保时钟在切换时钟源时仍保持稳定。

为保证时钟频率改变后的处理准确无误,首先写入相关的时钟控制寄存器改变频率,再从寄存器中读取值,最后进行后续处理。

图8. 切换时钟源的时序

5.5 时钟设置示例

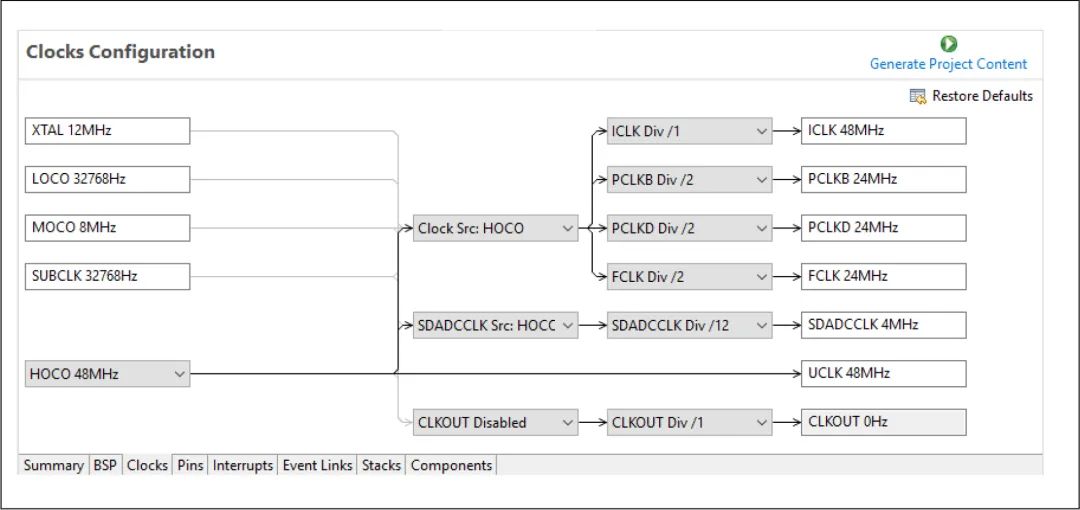

Renesas FSP为RA2A1 MCU提供了一个简单的可视化时钟配置工具,如下所示。此配置器可配置板级支持包中的代码,以根据用户的选择初始化时钟生成电路,并按照MCU硬件手册中的说明进行适当的配置。

图9. 使用 Renesas FSP配置器进行时钟设置

-

RA2快速设计指南 [3] 时钟电路2023-10-24 1499

-

RA2 MCU ADC转换时间测试方法2023-05-24 1092

-

RA2快速设计指南 [11] 外部总线、SDADC24和OPAMP2023-04-19 1930

-

RA2快速设计指南 [6] 存储器2023-04-06 2109

-

RA2快速设计指南 [4] 时钟电路(下)2023-03-29 1637

-

RA2快速设计指南 [2] MCU工作模式和选项设置存储器2023-03-25 2162

-

EK-RA2E2-快速入门指南2023-01-30 532

-

FPB-RA2E2-快速入门指南2023-01-11 490

全部0条评论

快来发表一下你的评论吧 !