IC设计知识点:高扇出的危害、RAM相关

电子说

描述

IC前后端:高扇出的危害

1、什么是高扇出?

高扇出指的是一个逻辑单元驱动的逻辑单元过多。常见于寄存器驱动过多的组合逻辑单元。至于驱动多少逻辑单元算过多,需要根据工艺,后端实现情况以及芯片本身类型来决定。

一般来说如果驱动逻辑大于10K以上,算是比较多的了。

2、高扇出有哪些危害?

危害1:驱动能力下降,时序紧张

扇出过高也就是也就意味了负载电容过大,电路原理基础告诉咱们,负载电容越大,充放电速度越慢,电平跳变所需要的时间增加,即驱动能力下降,时序更加紧张。面对高扇出的情况,后端工具通常会通过插入buffer增加驱动能力,然后插入buff又会增加延时,造成时序紧张。

危害2:不利于布局布线,会增加走线延时

高扇出的情况通常意味着负载end_point分布在block的各个位置。而驱动的start_point需要放置在相对应的中心位置,这就意味到start_point到end_points的走线延时较大,一旦时序紧张,后端工具需要花费很多时间去优化,玩玩结果还不理想。

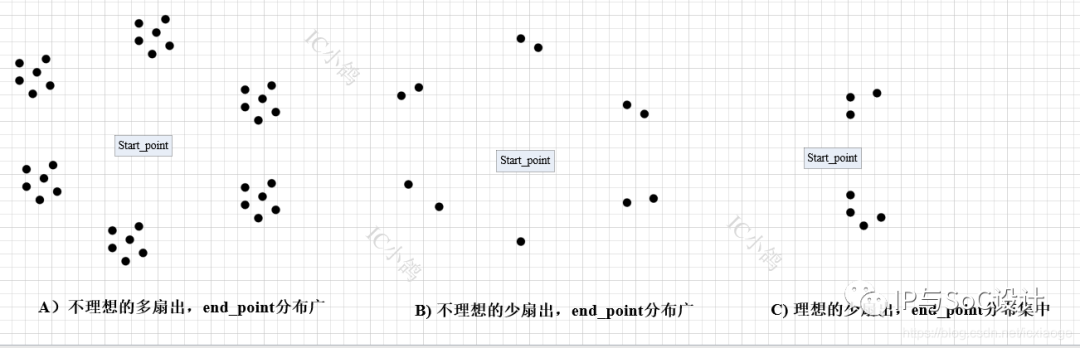

如下图所示:黑色点为end_point

A图所示,扇出高并且end_point很分散,在高扇出情况中很常见,后端工具实现花费时间长,并且很难优化,走线延时比较大,时序比较紧张。

B图所示:扇出不高但是end_point很分散,后端工具实现花费时间教长,优化有难度,走线延时比较大,时序比较紧张。

C图所示, 扇出不高并且end_point集中,是理想情况,后端工具实现简单,走线延时比较小。

IC设计RAM相关:RAM读写冲突返回值

1、RAM读写冲突返回值

在使用底层RAM IP的时候,以1R1W的ram为例,我们需要考虑 某个地址同时发生读写操作的时候(俗称读写冲突),RAM IP输出的data_out是什么值,不同的厂家IP会不一样,同一个厂家的不同ram也有可能不一样。例如:发生读写冲突时,有些ram会输出老值,有些ram会输出新值,有些ram输出不确定的值

2、从设计角度考虑RAM读写冲突返回值

从严谨的设计角度看,应该从方案设计角度避免此问题。在verilog实现中,ram就不允许发生同时读写同一个地址的情况,采用外部逻辑进行读写冲突保护。原因如下:

不同ram IP在读写冲突时,读写冲突返回值不一样,容易出错。

不同项目使用的工艺不一样,从而导致ram ip读写冲突返回值不一致,不利于代码复用。

IC设计RAM相关:ECC校验原理基础

1、ECC校验基础

Ram的ECC校验通常基于海明码编码原理实现,使用海明码编码需要额外的bit位存储校验位,ECC校验仅能纠正1bit的,无法纠正2bit以及以上数据错误,能发现部分多bit位错误的情况。

2、RAM ECC校验实现原理

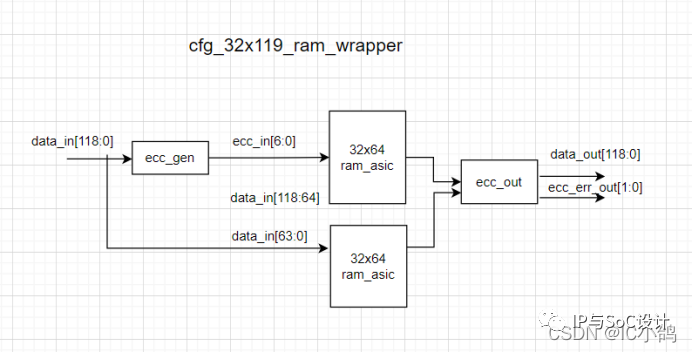

如图所示为1r1w的ram为例,cfg_32x119_ram_wrapper为verilog代码直接调用层次的ram_wrapper,表示了一个深度为32,数据位宽为119bit的ram。ram_asic.v为真实的ram IP。其中119bit的数据位宽紧张ECC计算需要7bit的校验位,因此物理IP最少需要126bit的ram IP。通常memory产生工具会更具时钟频率,深度位宽等因素对ram进行切分,因此本例中,使用了2个32x64的ram ip。

在data_in写入ram_asic模块之前,会经过ecc_gen模块,产生7bit的ecc校验位,随着数据一同写入ram_asic,其中data_in[63:0]写入第一个ram_asic,{2’b0,ecc_in[6:0],data_in[118:64]}写入第二个ram_asic。从ram_asic读出的数据会经过ecc_out模块经过ecc校验,输出校验后的data_out[118:0]和2bit的ecc_err_out告警。

审核编辑:汤梓红

-

接口测试理论、疑问收录与扩展相关知识点2024-11-15 1763

-

电阻的相关知识点2023-09-13 3650

-

STM32 RTOS知识点2023-08-01 762

-

滚珠螺杆的基本知识点2023-07-07 2545

-

数字电路知识点总结2023-05-30 7075

-

一文浅析IC设计的高扇出的危害、RAM相关知识2023-03-22 1775

-

详解射频微波基础知识点2023-01-29 3502

-

电力基础知识点合集2022-03-14 1326

-

STM32相关的知识点2021-08-16 1059

-

嵌入式知识点总结2021-07-30 1952

-

SRAM LIB库相关的知识点介绍2020-12-15 1814

-

PWM知识点详解2017-03-16 1912

-

高一数学知识点总结2016-02-23 1523

-

计算机组成原理考研知识点归纳2010-04-13 2029

全部0条评论

快来发表一下你的评论吧 !