PMOS在开关电路中的应用设计与分析

应用电子电路

965人已加入

描述

背景:在进行电路设计时,经常需要控制电源或者其它信号的通断,除了机械开关外,运用的较多的就是电子开关了。有些BUCK(降压)或者LDO(低压差线性稳压)电源IC自带EN就简单多,可以信号脚接上去或者分压电阻进行控制;而对于一些BOOST(升压)或者无EN脚的就得另寻它法了,活人不能让尿憋死不是。于是乎,你以前听说或者没听说的三极管+mos的开关电路,希望在看过下面的内容后能留下一丢丢印象。

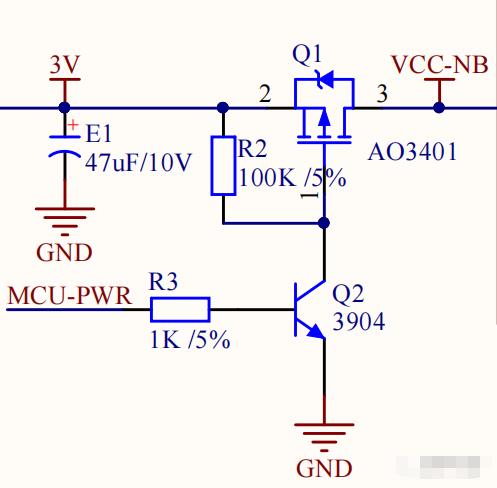

01 NPN+PMOS型高端开关

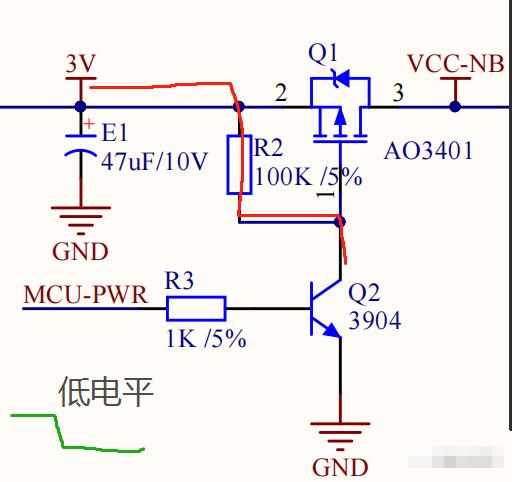

电路关闭状态:MCU-PWR输入低电平 ,VCC-NB电压:0V

电路分析:当R3左端输入低电平,Q2关闭,C极电平与Q1的G极电位相等;此时3V电源输入经E1电解电容滤波后经电阻R2将PMOS的G级1号脚拉高到3V,Vgs电压0v小于1.3v(即2脚S电压至少高于1脚g电压1.3V)的开启阈值,所以Q1关闭VCC-NB端无电压输出。

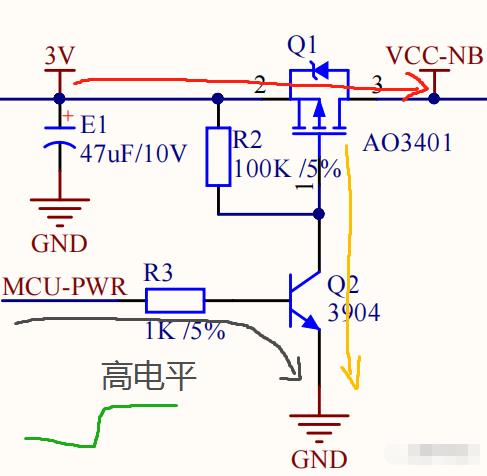

电路开启状态:MCU-PWR输入高电平, VCC-NB电压:约等于3V

电路分析:当R3左端输入高电平,Q2导通,C极电平与Q1的G极电位相等下拉到GND;,Vgs电压约等于3v大于1.3v(即2脚S电压至少高于1脚g电压1.3V)的开启阈值,所以Q1导通VCC-NB端电压输出约等于3V。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pmos开关电路连接方式有哪些2024-10-06 7794

-

NMOS与PMOS经典电源开关电路的深入解析2024-04-10 13231

-

如何设计一个nmos管和一个pmos管的开关电路2023-12-21 10661

-

电源开关电路图讲解:NMOS、PMOS2023-08-14 11839

-

PMOS开关电路分析2023-03-10 12535

-

电源开关电路的设计方案2022-08-08 1930

-

pmos 电源开关电路_如何验证开关电源电路2021-11-10 1400

-

怎样去做一个PMOS的按键开关电路2021-10-28 3239

-

PMOS按键电源开关电路2021-10-21 1737

-

基于PMOS的高速开关电路求教2020-06-08 6580

-

关于NMOS/PMOS在开关电路中应用的问题2019-04-18 8375

-

开关电路拓扑的分析和推演2017-09-11 890

-

四种常用晶体管开关电路(2种NMOS,2种PMOS)2016-08-30 64883

全部0条评论

快来发表一下你的评论吧 !