系统级封装的简史 SiP有啥优势

制造/封装

描述

系统级封装 (SiP) 是一种用于将多个集成电路 (IC) 和无源元件捆绑到一个封装中的方法,它们在该封装下协同工作。这与片上系统 (SoC) 形成对比,而这些芯片上的功能集成到同一芯片中。

图 1:SiP 示例 包含基于各种工艺节点(CMOS、SiGe、BiCMOS)的不同电路的硅芯片可以垂直或并排堆叠在基板上。该封装包含一条内部布线,可将所有管芯连接在一起形成一个功能系统。引线键合或凸块技术通常用于系统级封装解决方案中。 系统级封装类似于片上系统,但集成度较低,并且不是使用单个半导体芯片制造的。一个普通的SiP解决方案可能会采用多种封装技术,例如倒装芯片、引线键合、晶圆级封装等。 封装在系统级封装中的集成电路和其他组件的数量在理论上是无限的,因此,工程师基本上可以将整个系统集成到一个封装中。

系统级封装的简史

在 1980 年代,SiP 以多芯片模块的形式出现。他们不是将芯片放在印刷电路板上,而是可以通过将芯片组合到一个封装中来降低成本或缩短电信号需要传输的距离,而连接在历史上是通过引线键合实现的。 集成是半导体开发和使用背后的主要推动力。从 SSI(小规模集成——单个芯片上的几个晶体管)开始,该行业已转向 MSI(中等规模集成——单个芯片上数百个晶体管)、LSI(大规模集成——单个芯片上数万个晶体管)芯片)、ULSI(超大规模集成——单个芯片上超过一百万个晶体管)、VLSI(超大规模集成——单个芯片上数十亿个晶体管)和最后的 WSI(晶圆级集成——整个晶圆变成单个超级芯片)。 所有这些都是物理集成指标,没有考虑所需的功能集成。因此,出现了几个术语来填补空白,例如 ASIC(专用集成电路)和 SoC(片上系统),它们将重点转移到更多的系统集成上。

图 2:SOC 示例 – 内部视图 至于最初对 SiP 的需求,我们无需再看微处理器。微处理器的开发和生产要求与模拟电路、电源管理设备或存储设备的要求有很大不同。这导致了系统级集成度的明显提高。 尽管 SiP 这个词相对较新,但实际上 SiP 长期以来一直是半导体行业的一部分。 在 1970 年代,它以自由布线、多芯片模块 (MCM) 和混合集成电路 (HIC) 的形式出现。 在 1990 年代,它被用作 Intel 的 Pentium Pro3 集成处理器和缓存的解决方案。如今,SiP 已转变为将多个芯片集成到单个封装中以减少空间和成本的解决方案。

系统级封装的好处

SiP 和 SoC 之间的主要区别在于 SoC 将所需的每个组件都集成在同一芯片上,而 SiP 方法采用异构组件并将它们连接到一个或多个芯片载体封装中。 例如,SoC 会将 CPU、GPU、内存接口、HDD 和 USB 连接、RAM/ROM 和/或它们的控制器集成在单个硅片上,然后将其封装到单个芯片中。相比之下,等效的 SiP 将采用来自不同工艺节点(CMOS、SiGe、高功率)的独立管芯,将它们连接并组合成单个封装到单个基板 (PCB) 上。考虑到这一点,很容易看出与类似的 SoC 相比,SiP 的集成度较低,因此,SiP 的采用速度很慢。 不过最近,2.5D 和 3D IC、倒装芯片技术和封装技术的进步让人们对使用 SiP 提供的可能性有了新的认识。 有几个主要因素推动了当前用 SiP 取代 SoC 的趋势

天线、MEMS 传感器、无源元件(例如:大电感)等外部设备无法装入 SoC。因此,工程师需要使用 SiP 技术为其客户提供完整的解决方案。

交付模块而不是芯片是一种趋势,因为无线应用(例如蓝牙模块)可以帮助客户快速进入市场,而无需从头开始设计。相反,他们使用由整个系统组成的 SiP 模块。

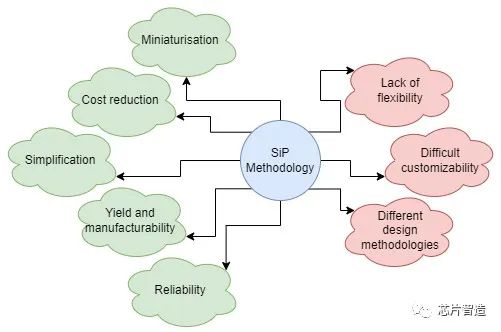

除了上述因素外,SiP 还具有以下优势:

小型化,降低成本,简化设计流程,良率更高,可靠性更好。

不过,为了全面了解,我们必须承认 SiP 也有一些缺点。以下是在选择 SiP 作为设计理念之前需要考虑的一些主要缺点:

缺乏灵活性

难以定制

不同的设计方法

图 4:使用系统级封装的优缺点

编辑:黄飞

-

系统级封装(SiP)技术介绍2024-11-26 3458

-

系统级封装(SIP)简介2023-05-19 6587

-

系统级封装(SIP)有什么用?2023-03-16 4524

-

系统级封装SiP整合设计的优势与挑战2023-01-24 2060

-

最新的系统级封装SiP发展趋势2022-11-24 2965

-

SiP系统级封装设计仿真技术2022-08-29 1263

-

系统级封装SiP在PCB的设计优势2022-08-09 2863

-

系统级封装SiP技术整合设计与制程上的挑战2021-05-31 4273

-

SiP系统级封装对比先进封装HDAP二者有什么异同点?2021-03-15 9706

-

SIP系统封装技术浅析2020-05-28 3686

-

基于LTCC技术实现SIP的优势和特点讨论2019-07-29 2845

-

系统级封装(SiP)的发展前景(上)2018-08-23 4395

-

SIP(封装系统),SIP(封装系统)是什么意思2010-03-26 20899

全部0条评论

快来发表一下你的评论吧 !