I/O端口的ESD保护

描述

本应用笔记描述了ESD如何威胁电子系统、造成的损坏类型、ESD的产生方式、使用的测试方法和波形、用于测试的人体和机器模型、IEC合规性水平、接触和空气放电。本文介绍了保护方法,详细介绍了Maxim的ESD保护方法。给出了选择具有高ESD电阻的IC的指南。RS-232 I/O 端口是专门考虑的。

当有人更换电缆甚至触摸I / O端口时,静电放电(ESD)可能会威胁到电子系统。伴随这些常规事件的放电可能会破坏端口的一个或多个接口 IC,从而禁用端口(图 1)。此类故障也可能代价高昂——它们提高了保修维修的成本,同时降低了产品的感知质量。

图1.ESD保护不足的IC容易发生灾难性故障,包括钝化破裂、电热迁移、铝溅射、触点尖峰和介电故障。

ESD还有另一种造成麻烦的方式。制造商可能很快就会被禁止向欧洲共同体销售产品,除非他们的设备达到最低水平的ESD性能。这两个因素,加上计算机和计算机相关设备之间的电气通信量不断增加,强调了工程师了解ESD的必要性。

要正确理解ESD,不仅需要了解所涉及的电压电平,还需要了解电压和电流波形、IC保护结构、测试方法和应用电路。以下各节将讨论这些事项。

静电放电生成

当两种不同的材料聚集在一起,转移电荷并分开,在它们之间产生电压时,就会出现静电荷。例如,在带有皮革鞋底的地毯上行走会产生高达25kV的电压。感应静电电压的水平取决于地毯和鞋皮之间的相对电荷亲和力、湿度和其他因素。

摩擦电系列(表1)描述了各种材料之间的这种电荷亲和力。当列表中的任何两个项目接触时,就会发生电荷转移。系列中较高的材料获得正电荷,而系列中较低的材料获得负电荷。1对于列表中相距较远的项目,净电荷和产生的静电电压更大。

表 1.摩擦电系列

静电测试方法

测试集成电路的ESD敏感性通常有两种方法。最古老的MIL-STD-883方法3015.7是为了帮助理解封装和处理IC所需的预防措施而开发的。该方法针对其他引脚组测试每个封装引脚,并根据发生故障的最低电压对器件进行分类。

本测试中施加的信号是从称为人体模型(图2)的电路得出的电流波形,该电路模拟人体的典型电容和源阻抗。(电路布局至关重要,因为IC上传输的实际波形还取决于与测试连接和印刷电路板相关的寄生电感和电容。由此产生的电流波形表示人接触物体(例如IC)时发生的ESD。

图2.如图所示,替换不同的组件值会产生称为人体模型、机器模型和 IEC 1000-4-2 模型(人体手持金属物体)的放电电路。

另一种方法与上述方法的区别仅在于R和C的值,由日本电子工业协会(EIAJ)开发。它被称为IC-121,基于称为机器模型(图2)的电路,它施加类似于IC与其处理机械接触时产生的电流波形。通过模拟积聚在运动部件上的电荷引起的ESD事件,波形模拟机器装配过程中看到的静电放电。

这两种方法是互补的,因此您不应该选择其中一种。由于ESD会在制造过程中、印刷电路板组装过程中以及最终产品投入使用后影响IC,因此基于人体模型和机器模型的测试可以充分保证IC对制造和插入的严格要求。

一些IC的引脚通过连接器暴露在外界,即使安装在外壳内的印刷电路板上,也可能遇到ESD。对于连接到电路板电路的其他引脚,ESD暴露的可能性较小。对于这类IC,方法3015.7(测试引脚组合)等测试方法不能充分表示输入/输出(I/O)引脚的ESD敏感性。

两者都根据任何引脚方法的最低电压故障提供额定值,这种方法可能无法满足I/O引脚(某些制造商提供)所需的更高水平的内部ESD保护。例如,器件可能具有可承受 ±15kV 的 I/O 引脚,以及±2kV 时失效的非 I/O 引脚。使用上述方法,器件的ESD额定值将小于±2kV。不过,幸运的是,现在有更好的测试方法可用于评估I/O引脚。

针对 I/O 端口的新 ESD 测试

I/O 端口允许与其他设备通信。IC 的 I/O 端口由逻辑引脚组组成,用于访问包含 IC 的系统外部的设备。当操作员从系统中连接和断开电缆时,这些引脚会受到静电放电和其他滥用。对于RS-232或RS-485接口IC的I/O引脚,ESD敏感性的理想测试方法应:

仅以模拟实际设备中ESD事件暴露的方式测试I/O引脚。

应用模拟人体产生的静电放电的测试波形。不同的电路型号指定不同的幅度、上升/下降时间和传输功率值。

在接通和不通电的情况下测试IC。

定义IC故障以包括闩锁(瞬间失控)以及灾难性或参数故障。闩锁被认为是一种故障机制,因为如果不被发现,可能会导致可靠性问题和系统故障。

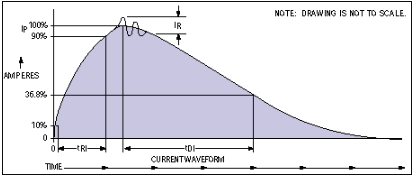

设备制造商越来越多地使用两种方法(均符合所列要求)来测试I/O端口的ESD敏感性。第一个是对方法 3015.7 MIL-STD-883 的修改。它使用与原始方法相同的电路模型和波形,但仅将ESD脉冲应用于器件的I/O引脚。其目的是模拟安装在电路板上并在目标系统中运行的IC看到的故障电流。波形(图3)由图2的测试电路使用与方法3015.7中最初指定的相同元件值生成。

图3.该ESD波形的参数(上升时间、峰值电流、振铃和衰减时间)在MIL-STD-883方法3015.7中指定。

与原始方法3015.7一样,修改后的方法仅定义了ESD波形和故障标准:暴露于波形后,故障IC必须出现闩锁或不符合一个或多个数据手册规格。修改后的方法在测试期间没有规定IC的特定工作模式,但Maxim建议执行所有可能的模式:电源开/关、发送器输出高/低、待机/正常工作等。

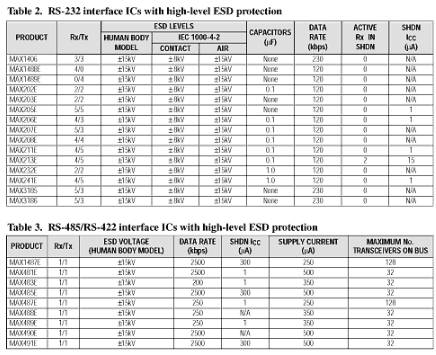

同样,修改后的方法3015.7不会强制产品承受特定水平的ESD;它只定义了保护等级。然而,Maxim的新型收发器通常提供±15kV的保护等级(表2和表3)。此级别允许一些用户消除昂贵的 TransZorbs™;和其他外部保护电路。

IEC 1000-4-2 型号

测试包含I/O引脚的IC的第二种更严格的方法是IEC 1000-4-2。该设备级测试由国际电工委员会开发。最初打算作为在欧洲销售的设备验收条件,它在美国和日本也迅速被接受为标准ESD标准。虽然最初不是作为IC规范,但现在它作为IC的ESD测试具有额外的作用。与对 3015.7 的修改一样,它只测试 I/O 引脚。

IEC 1000-4-2的模型也是图2所示的电路,但元件值不同。电阻R2(330Ω)代表人拿着螺丝刀或其他金属物体,C1(150pF)代表人体电容的另一种估计值。该电路产生的电流波形(图4)的上升时间比方法3015.7产生的电流波形更陡峭。

图4.此ESD波形的参数(上升时间、峰值电流、30ns幅度和60ns幅度)由IEC 1000-4-2规定。

IEC 1000-4-2 规定了通过接触放电和空气放电进行 ESD 测试。实际接触引起的ESD事件更可重复,但不太真实,空气放电更真实,但波形形状差异很大——取决于温度、湿度、气压、IC和电极之间的距离以及接近IC引脚的速率的变化。(这种形状的变化会对测得的ESD容差水平产生重大影响。

IEC 1000-4-2根据I/O引脚承受的最低最大电压定义了四个一致性级别(表4)。该表定义了接触放电和空气放电的这些水平。

表 4.IEC 1000-4-2 合规等级

接触还是空气放电?

根据IEC 1000-4-2测试IC的ESD耐用性需要使用ESD“枪”,该喷枪允许使用接触放电或空气放电进行测试。接触放电要求喷枪和I/O引脚之间有物理接触,然后才能通过喷枪内部的开关施加测试电压。空气放电要求喷枪在接近 I/O 引脚之前(从垂直方向尽快)用测试电压充电。第二种技术在距离测试单元的某个临界距离处产生火花。

空气放电产生的ESD类似于实际的ESD事件。但是,与实际的ESD一样,空气放电的种类并不容易复制。它取决于许多不容易控制的变量。因此,为了证明重复性在测试中的普遍重要性,IEC 1000-4-2建议接触放电,而修改后的3015.7方法仅要求接触放电。在任何一种情况下,测试程序都要求在每个测试级别至少放电 10 次。

刚才讨论的两个ESD标准(改进的3015.7方法和IEC 1000-4-2的空气或接触放电版本)之间的主要区别在于它们在被测器件中产生的峰值电流。不同的元件值会导致这些峰值电流相差大于5的系数(表1000)。由于峰值电流会产生IC必须耗散的不需要的功率,因此IEC 4-2-<>通常是要求更高的ESD测试方法。

表 5.ESD 电流与模型和施加电压的关系

高电流会以多种方式损坏 IC:

局部供暖过度

熔化硅

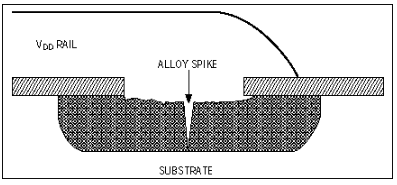

尖峰结,由将铝溶解在硅中的短路引起(图 5)

损坏的金属线

由于电压过高而导致栅极氧化故障

电热迁移导致的晶体管损坏(图 6)

图5.IC中的高ESD电流可以通过将铝触点部分溶解在硅中来“尖峰”结,从而导致下面的层永久短路。

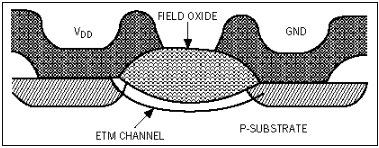

图6.IC中的电热迁移(ETM)可能会在发生ESD事件时为损坏奠定基础。由此产生的高电流和高电压会导致晶体管端子之间的短路或低阻抗路径。

保护方法

为了防止ESD,设计人员可以在外部添加保护,也可以选择内置高保护级别的IC。保护电路包括金属氧化物压敏电阻和硅雪崩抑制器,如TransZorb。这些设备有效但价格昂贵(硅雪崩保护器每条生产线的成本高达0.30美元)。外部ESD保护还会消耗宝贵的电路板面积,并增加I/O线路的电容。

为了克服这些限制,制造商一再提高其IC的ESD保护水平。例如,Maxim现在为RS-15 IC提供±232kV保护,无论是根据IEC 1000-4-2还是人体模型进行测试。

Maxim的ESD保护方法

ESD电流波形的特点是上升时间极快,因此其通过IC的进度受到电路分布寄生阻抗的强烈影响。因此,注意外部布局将确保IC的内部保护网络具有最佳性能。Maxim建议对其接口IC采用以下做法:

遵循标准的模拟布局技术,将所有旁路和电荷泵电容尽可能靠近IC放置。

在印刷电路板上包括一个接地层。

将走线电感和电容降至最低。

将 IC 放置在尽可能靠近 I/O 端口的位置。

为了表征RS-232收发器或其他接口IC在存在ESD时的可靠性,Maxim建议使用改进的3015.7方法和IEC 1000-4-2型号,每种情况下都遵循类似的程序:以200V的增量逐步穿过指定的ESD范围,在每个电平上,每个极性电压对器件进行10次打击, 大约每秒一次。

由于这些测试的目的是评估安装在终端设备中的IC的ESD性能,因此测试设置应使ESD电流沿着与该设备中相同的路径流动。应针对IC的接地引脚进行Zaps。(如IEC 1000-4-2中所述,电路接地通常连接到设备机箱。Maxim推荐使用Schaffner Instruments(瑞士)的NSG 435型ESD喷枪用于IEC 1000-4-2方法,并推荐IMCS(Oryx Technology Corporation,加利福尼亚州弗里蒙特的一个部门)的4000型ESD测试仪用于改进的3015.7方法。

您应该通过在每个 zap 之后监视三个参数来检查故障。首先,电源电流应保持恒定(增加可能表示闩锁或内部损坏)。其次,变送器输出电压应继续满足RS-5传输的最低±232V电平。第三,接收器输入电阻应保持在3kΩ至7kΩ之间(理想情况下,应保持在该范围内的恒定水平)。请务必在所有模式下对设备进行 zap 和测试:正常运行、关机、关机、发射器高/低等。

高抗ESDIC的选择指南

在选择必须承受高水平ESD的IC(特别是RS-232收发器)之前,需要解决以下一些问题:

IC保证承受什么级别的ESD电压,该水平是通过什么测试方法建立的?不同的测试方法产生不同的额定电压。目前,推荐的方法包括IEC 1000-4-2和修改后的3015.7方法。

ESD会导致IC闩锁吗? 闩锁是一个关键问题。如果ESD导致电路闩锁,IC可能会停止工作。由此产生的电源电流(高达1A)可能会损坏IC。

IC的ESD保护是否会影响正常工作?如果设计不当,正常运行可能会导致内部保护结构闩锁。

使用IC时必须遵守特殊预防措施吗?双极IC可能需要昂贵的低ESR电容或具有低交流阻抗的接地层。最好在一开始就了解这些要求。

IC的最大额定压摆率是多少?由于其ESD保护结构而易受闩锁影响的IC,可能会指定异常低的最大压摆率,以避免触发闩锁条件。

IC如何响应覆盖保证电压保护的整个范围的ESD测试?ESD保护结构的触发机制可以在不同的电压范围内启动,使打开的“窗口”没有保护。(例如,这样的设备可以承受±10kV,但在±5kV时失效。Maxim建议ESD测试以200V为增量覆盖整个范围。

审核编辑:郭婷

-

MAX7325 I²C端口扩展器,提供8路推挽式I/O和8个漏极开路I/O技术手册2025-05-22 1202

-

I/O接口与I/O端口的区别2025-02-02 3886

-

RA2快速设计指南 [6] 寄存器写保护和I/O端口配置2023-10-24 1732

-

8051单片机的四组I/O端口2022-08-05 14703

-

AVR中I/O端口寄存器介绍2022-02-16 3869

-

CC2530并行I/O端口应用2021-11-29 1839

-

在I/O电路中ESD保护结构的设计要求2021-04-02 4263

-

I/O端口静电防护,ESD二极管为其护航2020-11-18 2522

-

I/O接口ESD静电防护解决方案2020-10-29 2696

-

I/O接口ESD静电防护方案图2020-09-24 3638

-

esd保护二极管原理2017-11-08 80443

-

新ESD技术减小芯片的I/O尺寸2012-12-11 2672

-

ESD保护I/O端口2009-04-24 1423

-

ESD保护I/O端口-ESD Protection for2009-04-22 3343

全部0条评论

快来发表一下你的评论吧 !