同步时钟和异步时钟详解

描述

当触发器输入端的数据和触发器的时钟不相关时,很容易导致电路时序约束不满足。 本章主要解决模块间可导致时序 violation 的异步问题。

关于异步与同步的定义,许多地方都有介绍,细节上也有所差异。 本章主要的关注点是解决异步问题的方法,而不关心为什么会出现异步时钟,也不关心异步电路的具体结构,仅从异步时钟的时序结果去分析解决问题。

同步时钟

数字设计中,一般认为,频率相同或频率比为整数倍、且相位相同或相位差固定的两个时钟为同步时钟。

或者理解为,时钟同源且频率比为整数倍的两个时钟为同步时钟。 其实,时钟同源,就保证了时钟相位差的固定性。 具体可以分类如下:

同源同频同相位

此类时钟频率和相位均相同,是同步的。 时钟间数据传输只要满足正常的建立时间和保持时间即可,不需要特殊的同步设计。

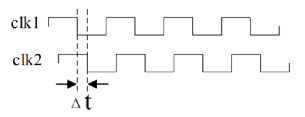

同源同频不同相位

两个时钟同频但不同相位时,只要相位差保持固定,也可以认为是同步的。 因为只要保证在两个时钟间传输的数据信号延迟,固定的控制在合理范围内,就不会导致时序问题。 而且,固定的时钟延迟也可以在版图级网表中修复。

固定的相位差可以理解为同源时钟下两个时钟因路径不同而导致的偏移。

同源不同频但存在整数倍分频比

此类时一个时钟往往是另一个时钟的分频,即便存在相位差也是固定的。

当单 bit 信号从慢时钟域传递到快时钟域时,因为同源,只要满足建立时间和保持时间,快时钟域总会采集到从慢时钟域传递来的信号。

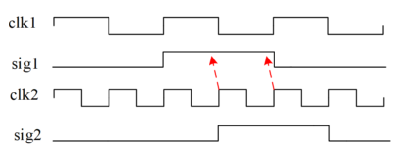

如下图所示,clk2 上升沿总能采集从 clk1 域来的信号 sig1,且采集到的信号 sig2 高电平持续周期也是两个时钟的频率比,即 2 个周期。

如果 clk2 域的信号 sig2 只需要一个持续一个时钟周期,则需要对 sig1 进行上升沿检测。

同步信号间的上升沿检测程序 Verilog 描述如下。

reg [1:0] sig2_r ;

always @(posedge clk2 or negedge rstn) begin

if (!rstn) sig2_r <= 2'b0 ;

else sig2_r <= {sig2_r[0], sig1} ;

end

assign sig2 = sig2_r[0] && !sig2_r[1];

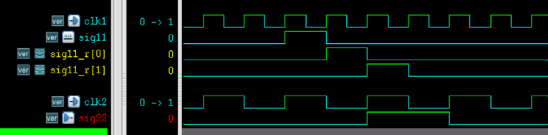

此时,快时钟域的信号 sig2 只会持续一个时钟周期,如下图所示。

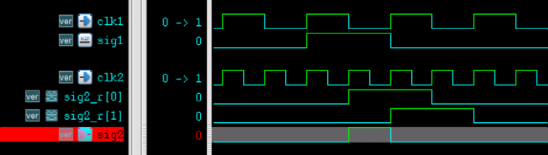

当单 bit 信号从快时钟域传递到慢时钟域时,只要慢时钟域能安全采集到从快时钟域传递来的信号,就不存在异步问题。 因为两个时钟是同源的。 如下图 sig1 到 sig2 的传输。

但是如果快时钟域信号过窄,慢时钟域有可能漏掉,如下图 sig11 到 sig22 的传输。 此时就需要对快时钟域的窄脉冲信号进行展宽。

当两个时钟频率比相对较小时,可以在快时钟域采用对信号延迟的方法进行展宽;

当两个时钟频率比相差较大时,对信号延迟的方法会有些繁琐,可在快时钟域采用计数的方法来延长单 bit 信号有效的时间。

利用延迟来展宽窄脉冲信号的方法 Verilog 描述如下。 因为 clk1 与 clk2 的频率比为 2,只需要延迟 2 拍 clk2 时钟即可。

reg [1:0] sig11_r ;

always @(posedge clk1 or negedge rstn) begin

if (!rstn) sig11_r <= 2'b0 ;

else sig11_r <= {sig11_r[0], sig11} ;

end

reg sig22_r ;

always @(posedge clk2 or negedge rstn) begin

if (!rstn) sig22_r <= 1'b0 ;

else sig22_r <= |sig11_r ;

end

assign sig22 = sig22_r ;

此时,快时钟域的信号被延迟 2 拍,总会被慢时钟域采集到,如下图所示。

总之,同源且频率比为整数倍关系时,可以理解为这两个时钟是同步的,不需要特殊的同步处理。 下面,简单介绍下异步时钟的情况。

异步时钟

工作在异步时钟下的两个模块进行数据交互时,由于时钟相位关系不可控制,很容易导致建立时间和保持时间 violation。 以下 3 种情况下的时钟可以认为是异步的。

不同源

由两个不同的时钟源产生的两个时钟是异步的,这是最常见的异步时钟。 即便两个时钟频率相同,但是也不能保证每次上电后两者的相位或相位差是相同的,所以信号间的传输与时钟关系也是不确定的。

同源但频率比不是整数倍

此时两个时钟间相位差也可能会有多个,例如同源的 7MHz 时钟和 3MHz 时钟,他们之间也会出现多个相位差,时序也不好控制。 一般情况下也需要当异步时钟处理。

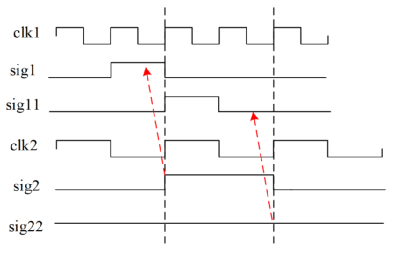

同源虽频率比为整数倍但不满足时序要求

前面介绍同步问题时有说明,当信号从快时钟域传递到慢时钟域时,只要慢时钟域能安全采集到从快时钟域传来的信号,就不存在异步问题。 但如果信号在快时钟域翻转速率过快,慢时钟域可能不会安全的采集到从快时钟域传来的信号,这也可以认为是异步问题。

一般来说,慢时钟域时序约束较为宽松,快时钟域较为严格。

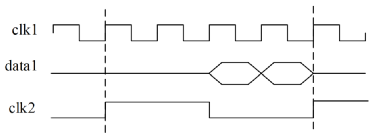

如下图,当快时钟域信号在慢时钟域上升沿前翻转了 2 次。 此时,慢时钟域会漏掉部分数据。 而且,数据的快速变化也可能导致 timing violation。

这里只简单介绍下异步时钟的分类情况,异步问题的解决方法请参考后面的章节。

-

安徽京准:北斗卫星同步时钟的安装与调试详解2025-06-05 1730

-

异步电路中的时钟同步处理方法2024-01-16 2437

-

异步时钟同步疑惑2023-09-12 6349

-

时钟同步的总线电路方案2023-06-23 3086

-

异步时钟的同步处理2023-06-05 3790

-

详解数字设计中的时钟与约束2023-01-28 4521

-

Verilog电路设计之单bit跨时钟域同步和异步FIFO2023-01-01 2001

-

如何将一种异步时钟域转换成同步时钟域2020-12-21 1748

-

多时钟域的同步时序设计和几种处理异步时钟域接口的方法2020-07-24 5489

-

简谈异步电路中的时钟同步处理方法2018-05-21 13787

-

同步和异步时钟之间是如何联系_如何正确的约束时钟2018-05-12 21116

-

异步时钟切换电路2014-05-08 6141

-

异步时钟域的亚稳态问题和同步器2010-07-31 1145

-

FPGA异步时钟设计中的同步策略2009-04-21 6473

全部0条评论

快来发表一下你的评论吧 !