三极管开关电路设计

应用电子电路

描述

[任务] GPIO通常无法提供比较大的拉电流和灌电流,试用三极管设计开关电路,以驱动大功率负载。

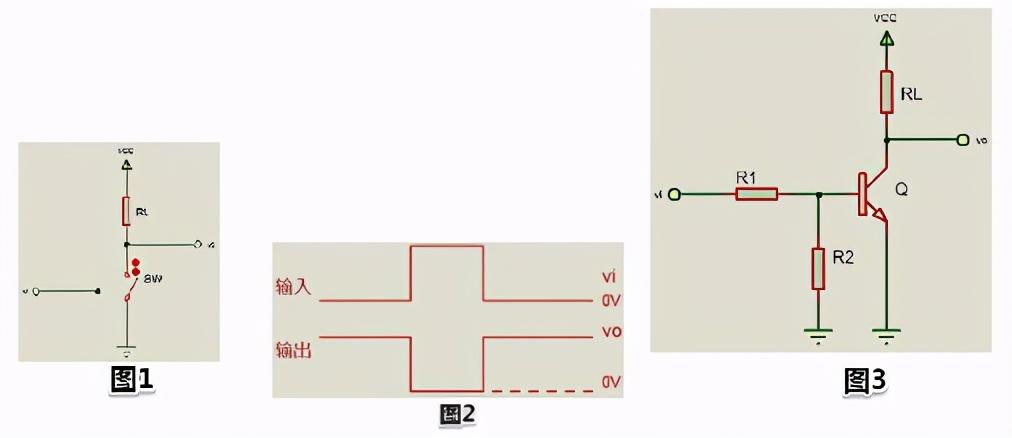

[构思] 以NPN三极管(PNP管设计为NPN情形的对偶类推,即VCC与GND对偶互换;NPN管C极接收灌电流,而PNP管C极输出电流)代替受控开关SW。控制模型如图1,控制波形如图2(类似于非门)。三极管代替开关SW后,基极电流必须限制(否则会烧毁三极管),所以在基极串联电阻R1;当输入控制信号vi浮空(高阻态)时,有可能使三极管误导通,所以在基极接下拉电阻R2,使三极管在控制信号vi为低电平或高阻态时,基极电平“钳制 ”在低电平而不至于因外界干扰而误导通。须知:负载的误动作有时是极其危险,甚至是致命的。构造的三极管开关电路如图3。

[分析] 如图3:当输入信号vi为高电平时,开关闭合,负载RL通电,输出信号vo为低电平;当输入vi为低电平时,开关断开,负载RL断电,输出信号vo为高电平。一般而言,VCC为负载RL的额定电压,为了使负载工作正常,负载的工作电压越接近VCC越好。因此,当三极管导通时,集电极与发射极之间的压降(UCE)越小越好,这意味着三极管工作在饱和状态,接下来的元件参数计算正是基于这种状态。

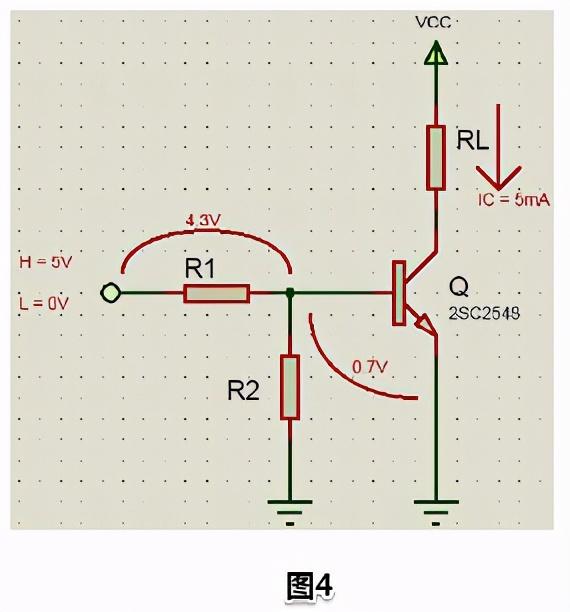

[计算] 假定输入信号为TTL电平(0V,5V),负载RL额定电流IC = 5mA,选用2SC2458三极管:hFE(min) = 70,BV = 50V,ICM = 0.15A, PCM = 0.2W, f = 80MHz。见图4。

下面计算R1,R2的取值:

使基极电流达到集电极电流的1/hFE(IB=IC/hFE),晶体管将处于导通状态。考虑到hFE的分散性及基极电流受温度影响而变化等因素,应使基极电流稍大些(过驱动),通常按所使用的三极管hFE的最低值计算的基极电流的1.5~2倍,即IB=(1.5~2) *IC/hFE(min)。已知:IC=5mA,hFE(min)=70,IB=(1.5~2) IC/hFE(min)=(1.5~2)×5/70 = 0.1~0.14mA,可取0.2mA(一位小数且大于0.14mA)。

由于三极管导通时,基极电位为0.7V,故高电平(5V)在R1上产生的压降为4.3V。前面已算出IB=0.4mA,故R1=4.3/0.2=22kΩ。

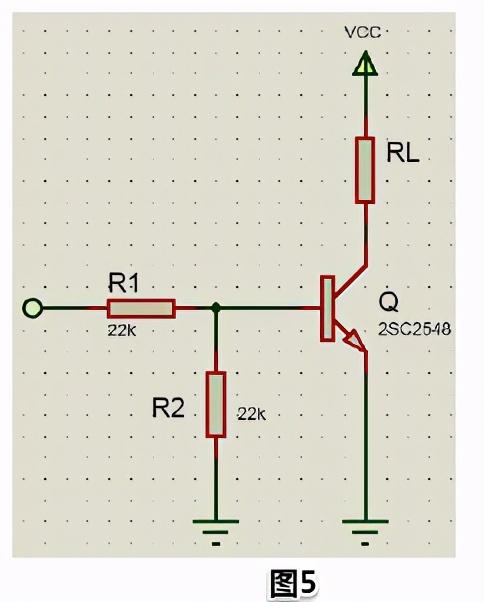

R2下拉确保输入信号为低电平或高阻态时三极管可靠截止,如果R2过大,将很容易受到外界噪声的干扰,过小则会过度分基极电流。这里不妨使R2=R1=22kΩ 。最终设计完成的原理图如图5。

-

三极管开关电路设计图原理2024-03-04 6507

-

三极管开关电路设计(电路结构、参数计算)2023-03-24 6382

-

简析三极管开关电路设计资料下载2021-04-19 1577

-

光耦加三极管开关电路设计是否合理?2019-05-30 3185

-

揭秘:三极管开关电路设计详细过程2019-04-15 3465

-

三极管开关电路设计指南2019-03-22 4146

-

三极管开关电路设计汇总(十一款开关电路设计原理)2018-01-25 214250

-

三极管开关电路设计电路图原理详解2017-12-29 46830

-

三极管开关电路设计的要点2017-11-15 18147

-

三极管开关电路设计详解2017-02-14 1052

-

三极管开关电路设计32016-01-07 498

-

三极管开关电路设计2013-07-28 22797

-

三极管开关电路设计详细过程2012-08-16 34232

全部0条评论

快来发表一下你的评论吧 !