电源layout布局

描述

电源layout布局

1. Layout布局推荐及要求

1.1 布线基本原则

1)输入电源与输出电源需要通过GND隔离,且避免平行走线。

2)功率电路与控制电路需分区域布局,避免重叠。

3)低频信号线需远离高频信号线。

4)高di/dt、dv/dt走线尽可能短。

5)线径间距要求要满足爬电要求、3W、3H;大电流电源线径加粗,保证电源平面更好。

1.2 线宽原则

1)线宽由流过的电流大小决定,大电流走线要提供足够的线宽,优化效率减少发热;特别是LX节点,由条件的情况下可以使用铺铜。

2)控制电路线宽至少20mil,例如Vcc,AGND(SGND);为了减少栅极驱动信号(DH、DL)阻抗,建议使用25mil线宽;其他信号线宽至少10mil。

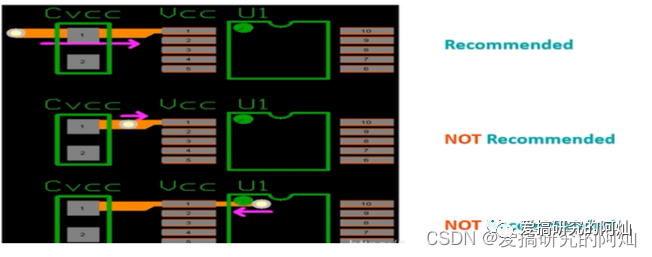

1.3 旁路/去耦电容

1)输入电容、旁路电容应该尽量靠近DC-DC芯片放置。

2)旁路电容必须尽量靠近DC-DC芯片的输入电源引脚,输入电容可以放置在距离DC-DC芯片大约1 inch 范围内。

3)多个电容时,小容值、小封装靠近IC。

注意:根据上述所讲对半径和过孔方式选择。

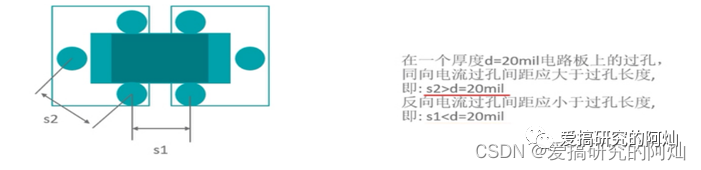

1.4 过孔设计

1)电流方向相同:过孔之间的中心距离应大于过孔的长度。

2)电流方向相反:过孔之间的中心距离应小于过孔的长度。

3)过孔VIa位置选择。

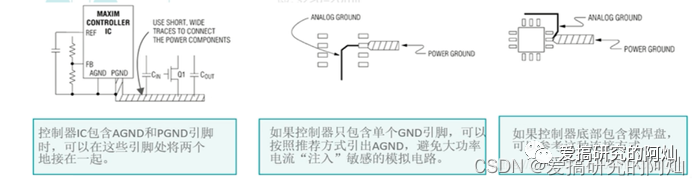

1.5 接地方式

1)单点接地,保持整个地平面。

2)模拟地和数字地需采用单点连接的方法。

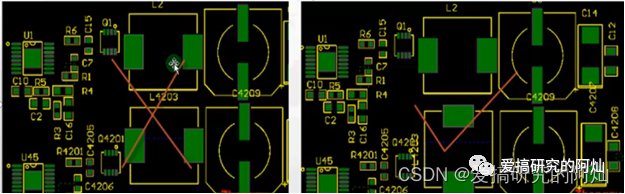

1.6 热设计

1)在MOSFET、电感周围提供足够的铺铜,改善散热;增加过孔,利用裸焊盘改善电路板散热。

1.7 电感设计

1)远离干扰电路(时钟电路、通讯电路、模拟采样电路等)。

2)DC-DC变换器是一个较强的电磁场干扰源,通常其EMI频谱范围自开关频率延伸至100MHz以上。为了减小电容性耦合和磁场环路耦合,必须将DC-DC变换器远离其它电路,尤其是小信号模拟电路。

3)对于输出多路的开关电源尽量使相邻电感之间垂直放置,避免电感磁干扰进行叠加。

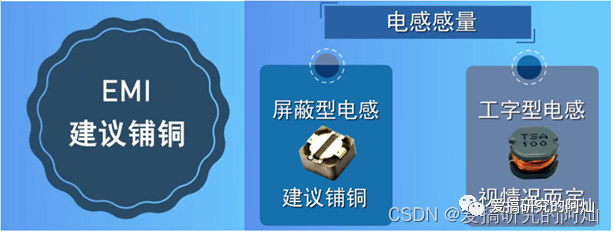

4)功率电感地平面铺铜分析:

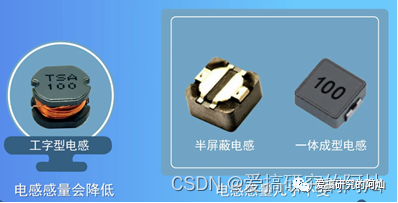

①铺铜影响:1.降低电感感量;2.增加系统损耗;3.增加GND平面噪音。

②铺铜好处:1.有利于EMI;2.因为是屏蔽电感对电感感量影响不大;3.可以帮助电感进行散热。

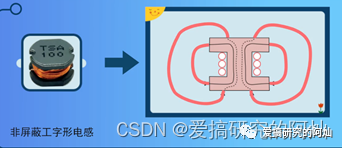

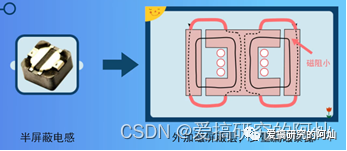

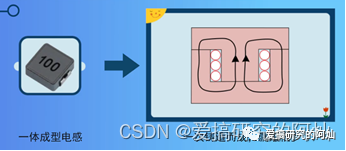

③电感分类:1.非屏蔽工字形电感,磁力线会完全暴露在空气中;2.半屏蔽电感,在非屏蔽工字形电感外围增加磁屏蔽材料,漏磁量有限;3.一体成型电感,在工艺中将绕组和导磁材料一次铸造而成,基本没有磁力线溢出。

④铺铜感量结论:

1.感量变化如下图所示:

2.铺铜EMI结论:

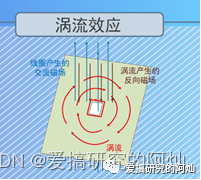

(1)首先讲一下涡流效应,可以更好的想象电感的磁场:交变磁场经过导体表面,根据电磁感应定律,会在导体表面形成感应电流,感应电流产生的磁场方向总是起到削弱原磁场大小的作用,这就是涡流效应。

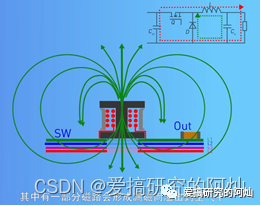

(2) BUCK电路未铺铜原始模型如图所示:没有铺铜时,漏磁会溢出到空气中。

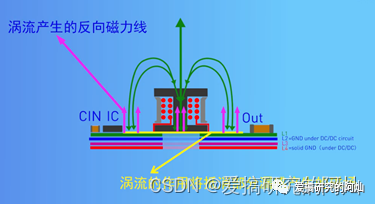

BUCK电路铺铜原始模型如图所示:当电感下面铺铜后会产生涡流效应,涡流的作用时抵消部分漏感产生的磁场,减少对元器件的影响。

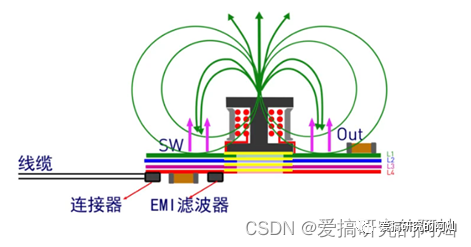

(3)EMI滤波器参考:将EMI滤波器以及连接器置于PCB背面,可以更好切断EMI的传播途径,可以参考下图所示。

⑤铺铜结论:

1.8 噪声优化

1)由于肖特基二极管一端连接DC-DC芯片的SW引脚,该引脚的信号为矩形波,若布线过长,走线的寄生电感就会很容易拾取到噪声,附加在SW信号中,形成噪声尖峰。肖特基二极管的布局基本要点是紧靠IC放置,并采用短且宽的线直接连接DC-DC芯片的SW引脚和GND引脚。

2)反馈采样电阻尽量靠近DC-DC芯片FB引脚。反馈走线要尽可能短,但是要远离噪声源比如电感和二极管,有时为了避开噪声源,走线走得长一些也是必要的。

-

Buck电路中PCB layout布局设计和注意事项2024-08-28 6232

-

电源的PCB布局要点2023-05-22 1842

-

电源系统分析之电源layout布局2023-02-10 6155

-

电源系统分析之电源电路原理2023-02-08 6388

-

DCDC PCB layout布局2022-12-11 9555

-

PCB Layout pcb布局的基本原则2021-07-21 16272

-

不可忽视的电源布局细节,电源 IC 的 PCB layout要点2020-07-16 4565

-

《80小时精通半桥LLC开关电源设计视频教程》已经更新完啦!!!2019-08-21 13849

-

layout中电源和地的处理2016-12-17 868

-

allegro 16.6 高速PCB layout设计电子布局工程视频教程2016-02-28 10226

-

开关电源布局和布线2015-07-21 18142

-

PADS Layout布局布线有什么技巧呢2014-12-31 15801

-

原创PADS 手机layout设计视频教程:BB布局2014-11-03 3801

全部0条评论

快来发表一下你的评论吧 !