Class-D功放TAS5731M上电时序分析

描述

在典型的音频功放应用中,通常使用音频DAC输出I2S信号送到数字音频功放进行音频放大。音频DAC会根据外围不同的配置来确定其作为master还是slave 模式,音频功放通常作为slave接受来自master 的I2S数据。CS5343是一款音频DAC,其通过I2S信号中的SDOUT的电平状态来确定主从模式。在CS5343和TAS5731M结合使用时,两颗芯片精确的上电时序控制是至关重要的,否则会出现偶尔没有声音的问题。具体分析如下。

TAS5731M介绍:

TAS5731M 是一款集成DSP 和支持2.1模式的2*30W高效数字音频D类功放,可以用于驱动立体声桥式扬声器,可接受宽范围额输入数据和传输速率。TAS5731M 只可作为从设备工作,接收外部的所有时钟和数据信号。根据采样率不同,TAS5731M工作时会在384kHz开关速率至352kHz开关速率直接进行PWM调制。

TAS5731M 电源轨介绍:

TAS5731M 存在三个电源轨,PVDD, AVDD以及DVDD。PVDD用于对半桥供电,供电范围支持8V-24V,AVDD及DVDD分别是对内部的模拟器件和数字电路供电,支持3.3V。在实际应用中,会简化电路可将AVDD和DVDD采用一个3.3V电源共同提供。

TAS5731M上电时序分析:

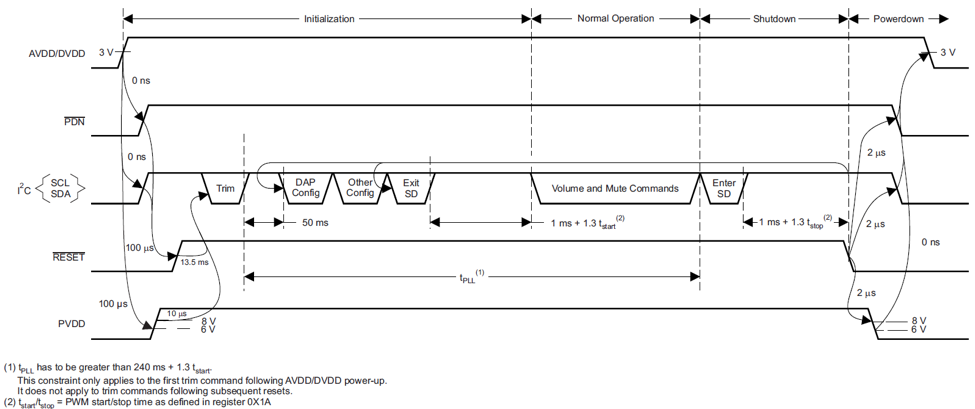

由于TAS5731M内部集成了DSP数字电路以及半桥等模拟电路,上电时序对器件正常工作是至关重要的。如下图1所示为TAS5731M推荐上电时序:

图1 TAS5731M 推荐上电时序

为保证芯片内部逻辑控制正确,须要保证AVDD/DVDD首先上电,确定各个端口保持在稳定电平。在AVDD/DVDD达到稳定电平之前,PDN以及RESET引脚需一直处于低电平,保证芯片处于复位状态。在AVDD/DVDD达到稳定电平之后,所有逻辑电平状态已经确定,再将PDN和RESET以及PVDD拉高和上电,让芯片开始正常工作。

从上图1标注可以看出,能够保证端口电平稳定的AVDD/DVDD的值约为3V,结合到TAS5731M datasheet中提到,当PVDD达到7.6V和AVDD/DVDD达到2.7V时,所有电路才可以正常工作。原因在于TAS5731M内部有1.8VLDO,用于确定端口的电平状态。1.8V LDO 通过AVDD 3.3V供电,由于LDO 存在压降,所以在AVDD上升到2.7V及以上时,LDO开始工作输出稳定1.8V电压,确定各逻辑电平状态。1.8V LDO电压可以通过Pin18 VR-DIG测量。

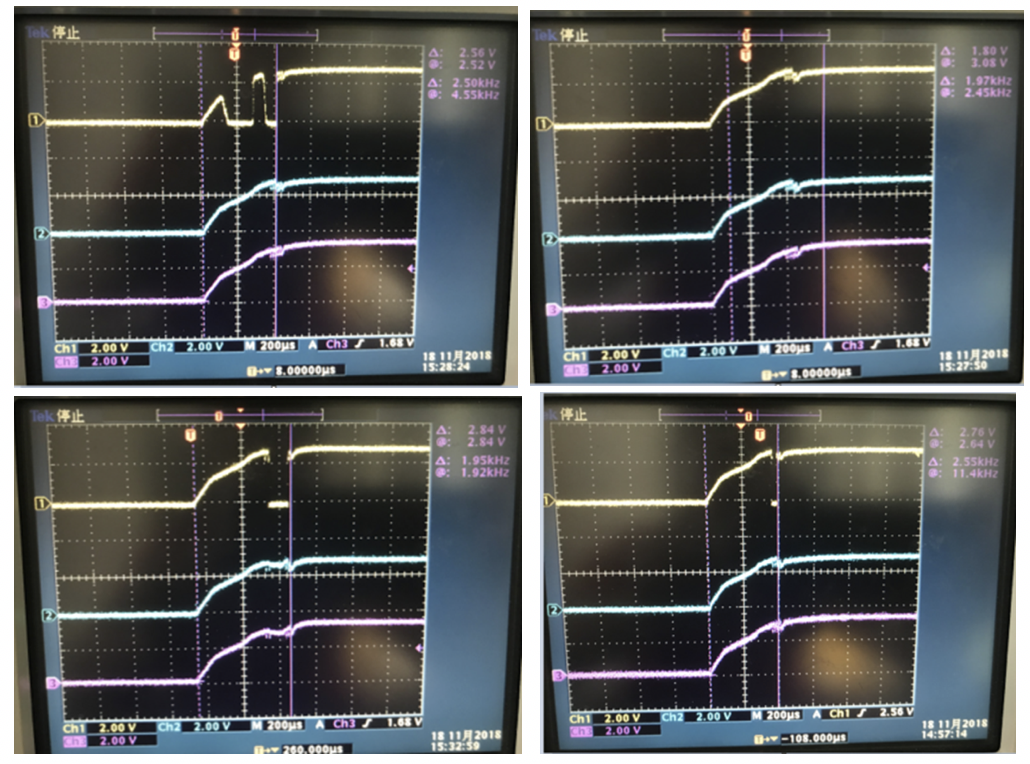

下图2为在相同测试条件下,不同测试时间TAS5731M SDIN(黄色)AVDD(红色)SCLK(蓝色)的波形。SDIN引脚通过上拉电阻拉到AVDD。可以看出,在AVDD未达到2.7V之前,SDIN引脚的会出现不同的高低电平。特别是在AVDD刚好到达2.7V左右时,SDIN的电平会突然进行切换,然后由上拉电阻再提到到3.3V。

图2 TAS5731M SDIN/AVDD/SCLK波形

因此,对于音频DAC CS5343+TAS5731M的应用场景, 音频DAC CS5343上电之后会立刻检测SDOUT,对应TAS6731M 为SDIN引脚的电平状态确定其工作状态,电平为高处于master模式,输出I2S信号;电平为低,处于slave 模式,不输出I2S信号。若CS5343在TAS5731M AVDD电平没有达到2.7V之前去检测SDIN电平状态,就会检测出低电平情况,CS5343被认为作为slave模式工作,导致没有声音输出。

针对这种情况,有两种解决方案:

1. 改变上电时序。由于DAC需要检测SDIN电平状态,可以保证先让TAS5731M供电稳定,然后再给CS5343供电。

2. 采用硬件控制模式的音频DAC,如PCM1808+TAS5731M。PCM1808可通过硬件引脚电平配置确定其主从模式。

审核编辑:郭婷

-

tas5731m没有mclk可以吗?2024-10-30 417

-

TAS5731M开机有冲击声怎么解决?2024-10-28 325

-

TAS5731M内部有主时钟MCLK吗?2024-10-25 465

-

tas5766m和tas5731m哪个音质更好?2024-10-24 428

-

请问TAS5731M的每一路输出都是左右声道混合的音频吗?2024-10-23 504

-

Class-D功放TAS5731M上电时序分析2022-11-09 711

-

Class-D 功放TAS5731M 上电时序分析2022-10-31 935

-

TAS5731M上电时序分析2022-01-19 5907

-

TAS5731M存在哪几个电源轨?分别是什么?2021-07-13 2203

-

数字功放芯片NTP8835和TAS5731M对比测评哪个好?2021-05-28 3765

-

数字功放芯片NTP8835和TAS5731M的对比测评2021-05-04 10298

-

TAS5731M 具有 DSP 和 2.1 MODE 的 20W 立体声数字音频功率放大器2018-11-02 5523

-

TAS5731M如何限制失真2018-08-29 1956

全部0条评论

快来发表一下你的评论吧 !