FPDLINK的电火花干扰优化

描述

随着汽车工业的不断发展其电气化程度越来越深,从而其各种前/后装设备的电气系统稳定性对车辆安全而言也愈加重要。例如根据GB/T 19056-2012和JT-T794-2011标准,车载MDVR等产品就需强制通过电火花干扰测试以确保其稳定可靠工作。

而与此同时,在目前MDVR智能化的趋势下(AI),需要更精确的摄像头视频数据用于AI分析。此时用TI的FPDLINK-III来实现数字视频信号的传输,相较传统的模拟视频信号传输优势明显,但挑战的是:在上述电火花干扰测试方面,FPDLINK更高频的信号传输也更易受到干扰,本文即主要针对该问题进行原理剖析,并整理相应优化方法以应对该挑战。

1. 实验模型及干扰途径

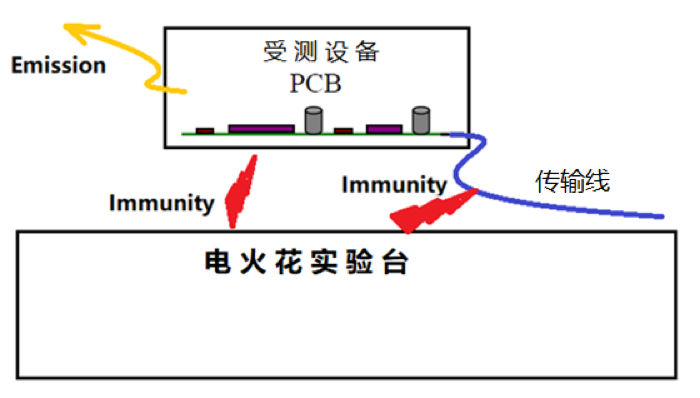

电火花干扰实验模型可参考下图fig.1,同时实验用电火花信号规格如table.1。

Fig.1 电火花干扰实验模型

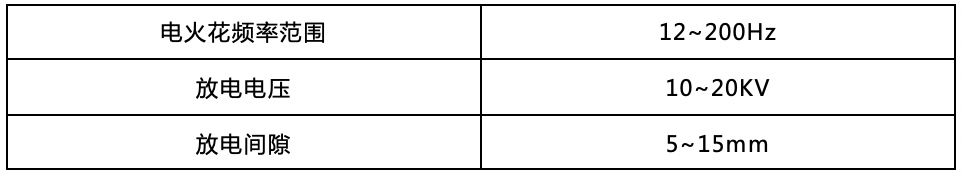

Tabl.1 电火花信号规格

通过上图我们可看出,电火花干扰实验基本等效于存在外界强干扰源情况下的EMC抗扰测试(EMS),此时受测终端设备被电火花所激发电磁场通过辐射的方式所干扰,而主要传递途径包含FPDLINK传输线以及受测设备PCB走线等,后续我们也就分别从这两个方面来简述其原理及优化方式。

2. 干扰原理及优化方式

a. PCB干扰

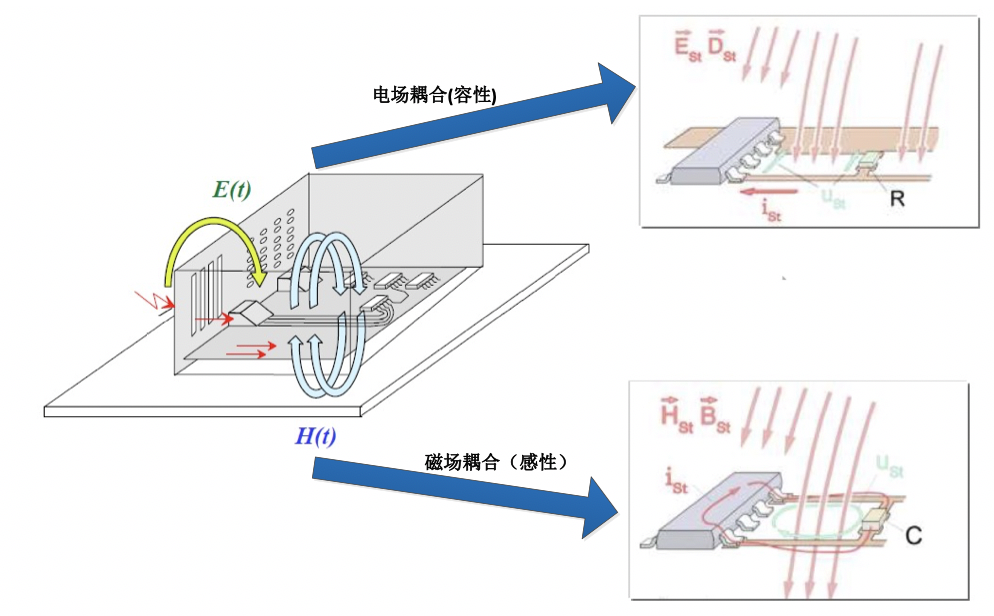

实验台中的电火花会激发强电磁场,此时受测设备也随之处于一个很强的辐射环境下,而其中的PCB会从两个方面被干扰并产生噪声电压/电流,从而影响系统正常工作:

一是PCB不同网络/层间有寄生电容(网络铺铜面积越大寄生电容越大),此时会在该寄生电容上耦合产生电压噪声,从而影响系统正常工作。

另一是PCB上构成回路的走线可等效看成感性线圈,在强磁场的影响下会耦合产生噪声电流,通过板上阻抗最终也可转化为噪声电压从而影响系统正常工作。

下图模型可帮助进一步理解上述两种干扰形成的过程。

Fig.2 干扰耦合方式

基于以上原理,对于电火花干扰,在PCB上我们可做如下优化来提升其抗扰能力:

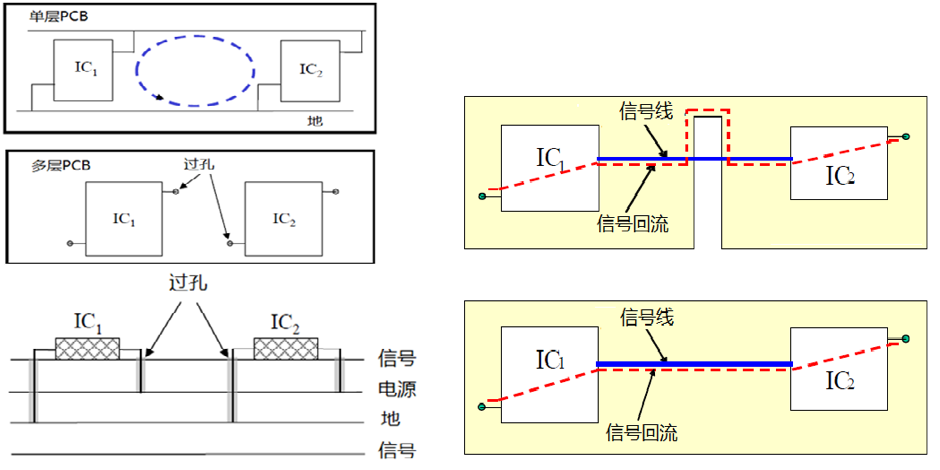

尽量用多层板(单层板往往会导致各电源/信号至地的走线回路更大,从而产生如上更大的感性耦合干扰)

设置单独的电源层和地层

多层板的板层间距尽量大些,从而减小寄生电容随之减少如上的容性耦合干扰

高速信号线需避免回路中有空隙/阻断等

Fig.3 PCB layout 建议

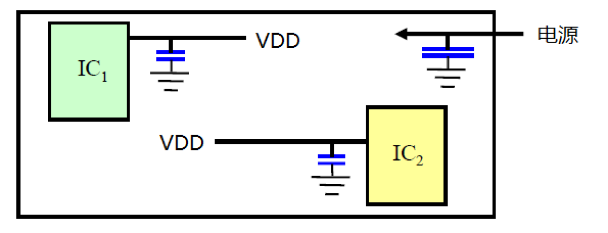

同时原理图设计时,在各芯片VDD或其他管脚上放置单独的退耦电容也是一个消除该干扰的常用方法。(信号管脚需留意退耦电容是否影响正常通信等)

Fig.4 退耦电容

最后,对于这种情况下PCB的辐射干扰,一个完全闭封的导电金属外壳或板上屏蔽罩也有很好的优化作用,但这种方式对产品成本影响较大,建议根据实际产品情况酌情考虑。

b. 传输线干扰

传输线干扰的模型比较简单,此时可将传输线看作一根长的天线,在电火花实验产生的射频干扰环境下会直接产生噪声从而影响正常视频信号质量。

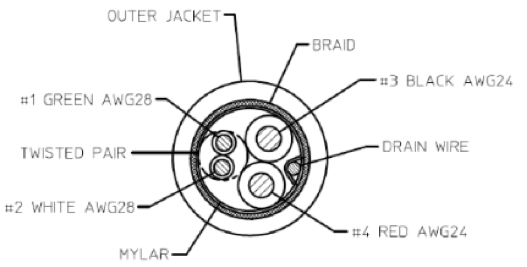

所以在传输线的干扰优化上,一个良好的线缆屏蔽层就非常重要,推荐如下类型的STP与屏蔽同轴线。

fig.5 STP线

fig.6 屏蔽同轴线

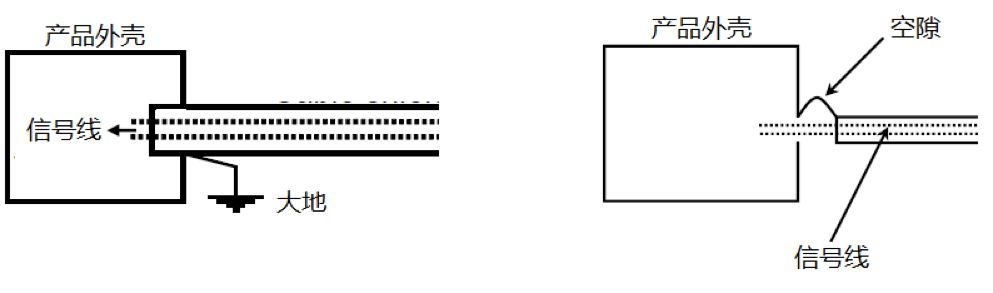

建议将屏蔽线接头拨线部分延伸入金属外壳内部而不要暴露在外面,同时线缆屏蔽层接大地以为干扰信号提供良好的耗散回路。

fig.7 传输线连接处理

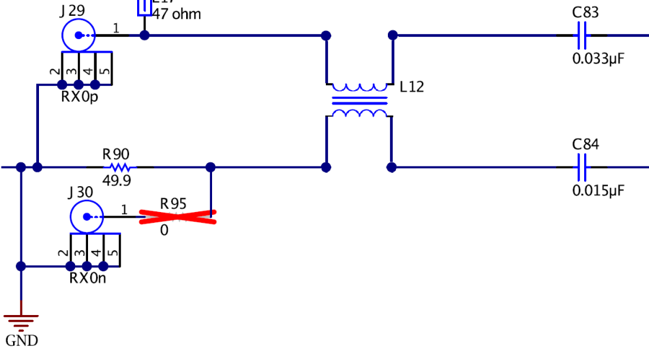

除了线缆屏蔽,另外一个可以对传输线干扰优化的方式是,在线缆的输入端放一个共模电感,可参照TI-FPDLINK芯片的参考设计(如下为DS90UB954 参考设计),这样对已经耦合进传输线的噪声也能起来一定滤除作用。

fig.8 FPDLINK输入共模滤波

审核编辑:郭婷

-

FPDLINK的电火花干扰优化测试2022-11-09 692

-

FPDLINK 的电火花干扰优化2022-10-31 579

-

实验模型及干扰途径2022-01-19 1462

-

电火花加工实验2020-05-21 4569

-

电火花检漏仪的原理是什么?2020-03-20 1704

-

电火花计时器工作原理_电火花计时器工作电压2020-01-08 27810

-

微细电火花加工的组成特点与系统设计2019-10-17 8114

-

电火花加工放电状态2019-10-10 12065

-

电火花检测仪的注意事项2018-11-28 6254

-

单通道电火花震源及其放电实验研究2017-01-05 760

-

电流型电火花加工脉冲电源的研究2014-08-18 2819

-

先进的电火花技术2011-02-23 1606

-

基于单片机控制的电火花加工电源2010-05-31 1167

-

电火花切割用脉冲电源电路2009-02-09 3564

全部0条评论

快来发表一下你的评论吧 !