如何生成Aurora核、仿真上板测

嵌入式技术

描述

由于项目需要,小编使用Aurora核对数据进行光纤传输,这篇文章主要介绍如何生成Aurora核、仿真上板测

试。

一、Aurora IP建立

第一步

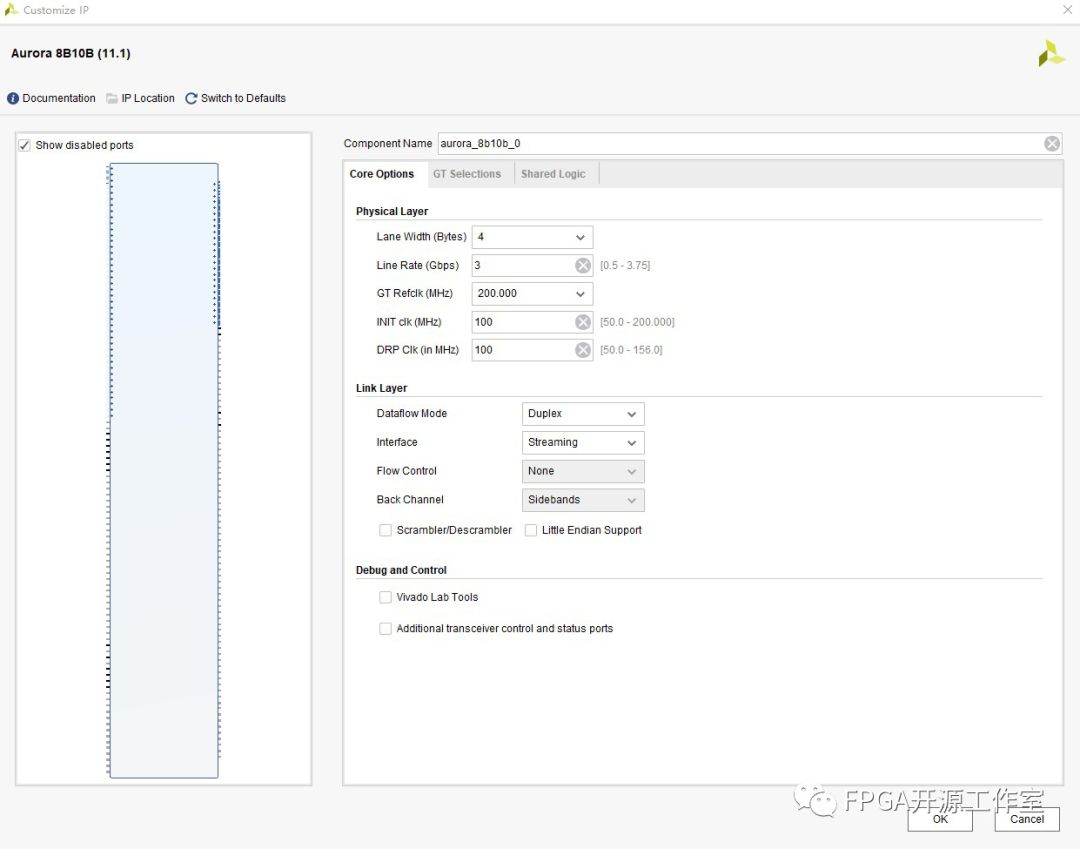

1>lane Width:用户数据接口 4(32bit) 2(16bit)

2>Line Rate:3Gbps 假设图像数据为1280x1024 @60 RGB(24bit),那么 1280 pixels/row x 1024 rows x 8bits/element gray scale x 3 elements/pixel x60 Hz refresh x 1.25 8b/10b x 1.05 (typical FC-AV protocol overhead) is approximately equal to 2.5 Gbps.

3>GT Refclk:200(此处查看板子原理图即可)

4>INIT clk:100MHz

5>DRP clk:100MHz

上述两个时钟在参考范围内设置相同即可,本页其他选项如图设置即可 。

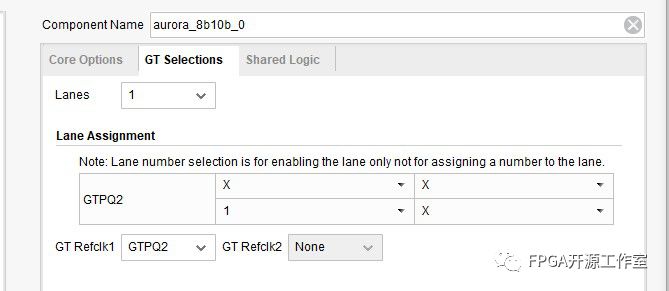

第二步

选择高速串行通道的位置,默认即可 。

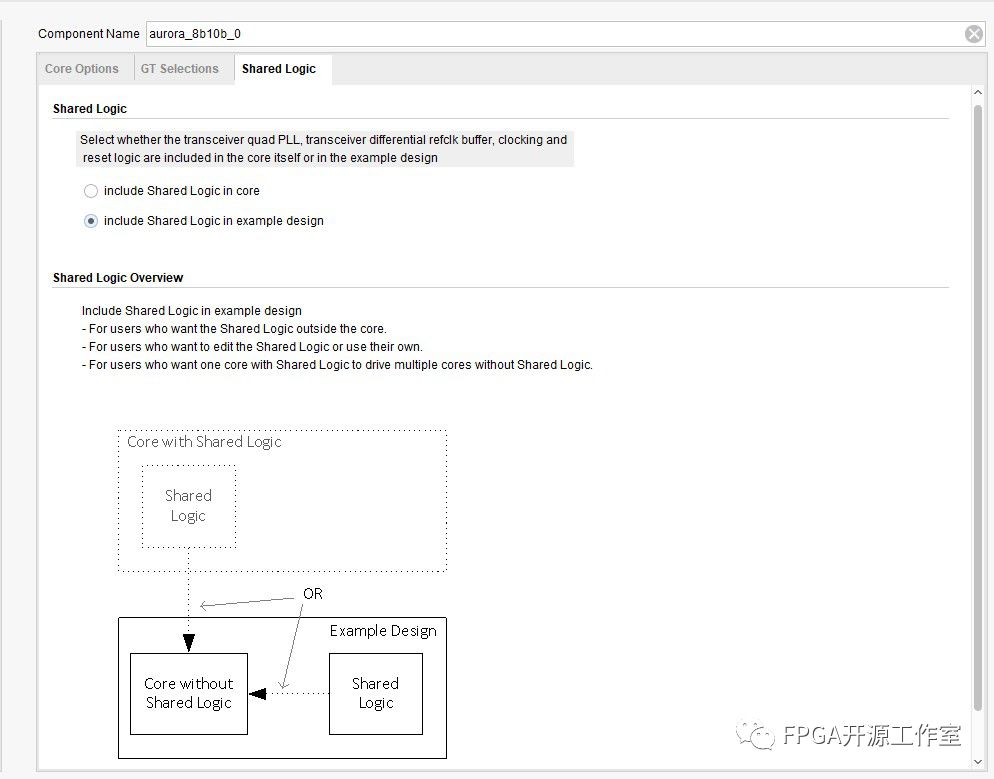

第三步

默认即可。

二、仿真测试

在Vivado软件中,我们生成好IP后可以可以打开带有例子的工程,进行仿真查看LANE_UP和CHANNEL_UP信号拉高后,即可认为光纤通道初始化成功,在对其数据接口进行查看,官方给的例程主要分为三大块,数据产生模块、光纤传输模块、数据检查模块 。

三、上板测试(光纤初始化)

我们需要对INIT_CLK_P、INIT_CLK_N、DRP_CLK、GT_RESET_IN、RESET四个信号进行修改。

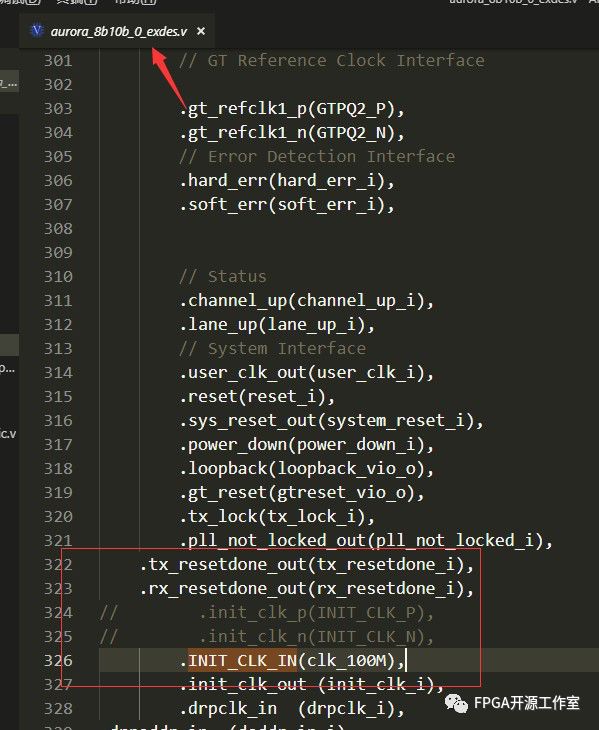

第一步

INIT_CLK_P、INIT_CLK_N:我们利用板子的单端输入时钟27M进行pll倍频出的100M提供给INIT_CLK_IN。

将aurora_8b10b_0_exdes文件做如下修改

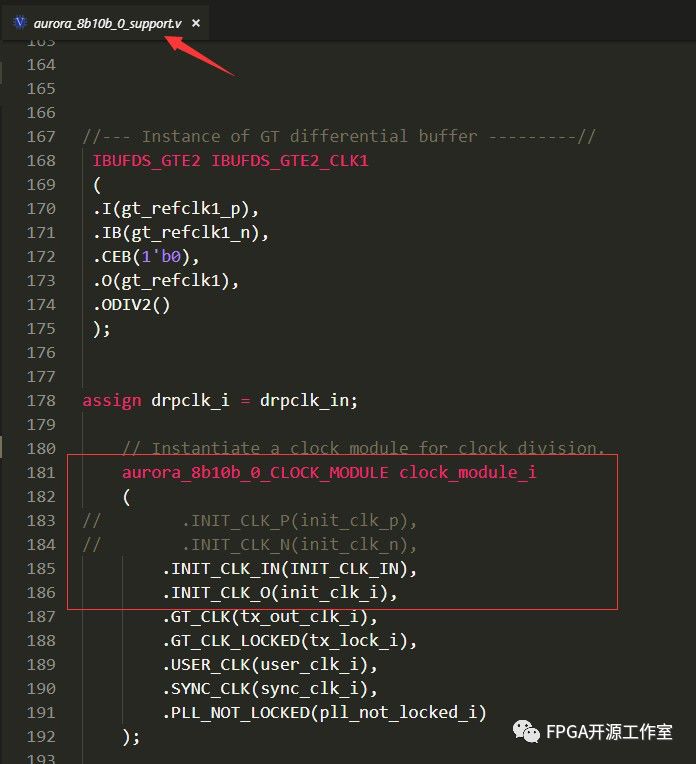

将aurora_8b10b_0_support文件做如下修改

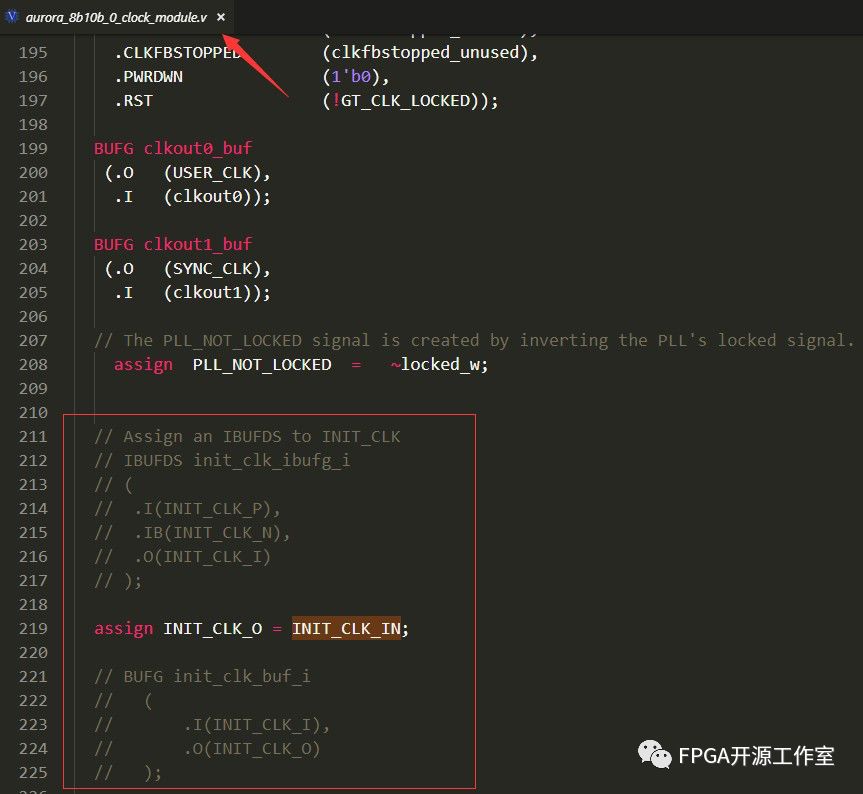

将aurora_8b10b_0_CLOCK_MODULE文件做如下修改

第二步

DRP_CLK:将倍频出的100M时钟输入给DRP_CLK即可。

第三步

GT_RESET_IN、RESET:如果板子上有硬复位(低有效),对其取反赋给其即可,在顶层aurora_8b10b_0_exdes

中修改。

assign RESET = ~sys_rst_n;

assign GT_RESET_IN = ~sys_rst_n;

第四步

如果我们板子上有指示灯,我们可以通过指示灯来查看是否初始化成功。在顶层aurora_8b10b_0_exdes中修改。

assign CHANNEL_UP_led = ~CHANNEL_UP;

assign LANE_UP_led = ~LANE_UP;

我们的指示灯是低电平亮,所以对其取反,上板烧写例程代码后可以看到两个指示灯点亮,我们就可以认为此

时光纤核初始化成功。

学会使用Aurora核之后,那么我们就需要利用相关协议进行传输,小编在本次项目中使用ARINC818协议

对数据进行封装,然后过光纤进行传输,最后回传到sdi芯片进行显示,开发者可根据项目需要选择协议

对数据进行传输。

编辑:黄飞

-

使用aurora核的点对点通信应用设计2018-01-26 13404

-

【米尔-Xilinx XC7A100T FPGA开发板试用】+04.SFP之Aurora测试(zmj)2024-11-14 3289

-

IP核生成文件:XilinxAltera2012-08-12 3386

-

aurora使用问题2015-03-06 5039

-

在做FFT IP核的仿真时遇到问题,居然不能生成FFT的仿真文件,求解答2016-10-07 10928

-

Aurora Core无法正确生成完整的.vho文件2019-03-20 2135

-

QUARTUS 13.1在生成FFT IP核时仿真文件生成不了?2019-04-03 4473

-

Aurora IP 8b10b如何生成bitfile?2020-03-30 2196

-

IP核生成文件2009-07-21 717

-

基于CAN核的四冗余通信板设计与仿真2010-02-03 1497

-

FPGA中IP核的生成2015-11-30 964

-

Vivado软件仿真DDS核的过程中应该注意的问题2018-07-13 10384

-

Zynq UltraScale+ MPSoC在仿真板上的运行展示2018-11-26 4188

-

在FPGA上生成8086指令兼容的软核以及外设并在此基础上跑通pc机上吃豆子PACMAN游戏项目2021-09-16 1122

全部0条评论

快来发表一下你的评论吧 !