单晶硅刻蚀工艺流程

描述

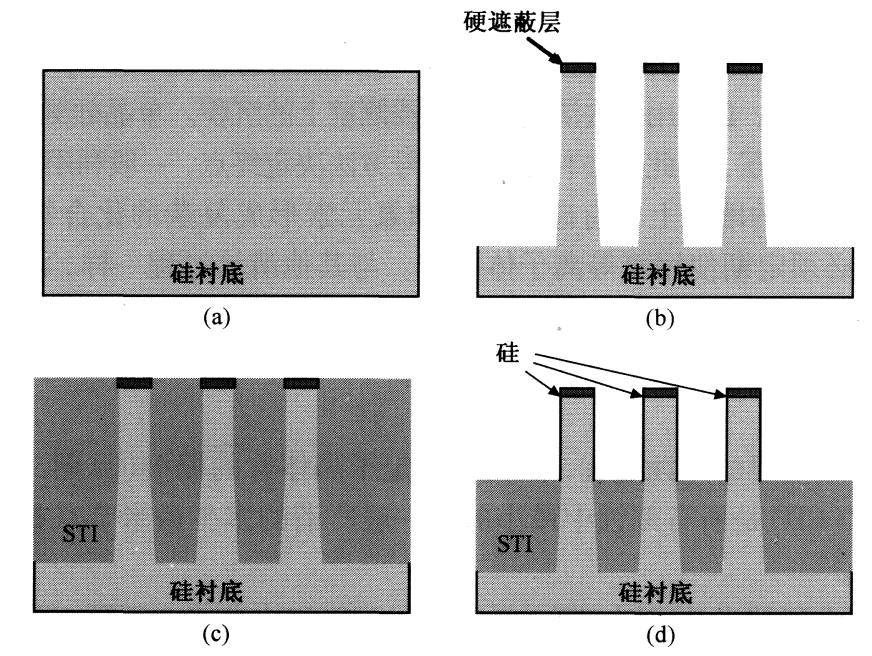

FinFET三维器件也可以用体硅衬底制作,这需要更好地控制单晶硅刻蚀工艺,如CD、深度和轮廓。

硅鳍的高度通过STI氧化层控制(见下图)。CD和硅鳍的高度可以通过原子力显微镜(AFM)和散射技术测量。

单晶硅刻蚀一般釆用二氧化硅或使用二氧化硅和氮化硅的硬式遮蔽层代替光刻胶避免污染,如下图(b)所示。这个过程以HBr为主要刻蚀剂,作为侧壁钝化作用的媒介。

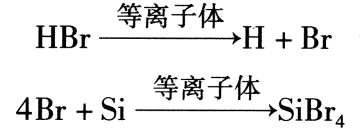

HBr在等离子体中分解释放澳元素自由基,这些自由基和硅反应形成具有挥发性的四溴化硅(Tetrabromide,Si-Br4)o氧会氧化侧壁的硅而形成二氧化硅以保护硅不受溴元素自由基的影响。

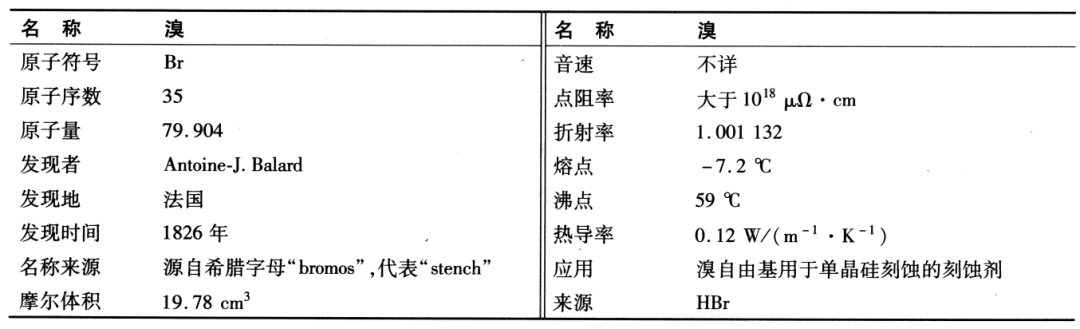

在沟槽底部,离子轰击使氧化物无法生长,因此刻蚀只在垂直方向进行。下表列出了溴元素的相关参数。

单晶硅等离子体刻蚀的主要化学反应为:

氧气一般用来改善氧化物硬式遮蔽层的选择性,同时也可以作为与刻蚀副产品SiBr反应形成沟槽侧壁上的SiBrxOy沉积。由于沟槽底部的SiBrxOy沉积会不断地被离子轰击移除,所以SiBrxOy沉积物就可以保护侧壁并将刻蚀限制在垂直方向。氟元素的来源气体如SiFq和NF3也能改善沟槽侧壁和底部刻蚀轮廓,氟也可以实现bWL DRAM所需的单晶硅和二氧化硅刻蚀率。

单晶硅刻蚀包括两个工艺过程:突破过程和主刻蚀过程。简单的突破过程通过强的离子轰击和氟元素化学作用移除硅表面的薄膜原生氧化层。主刻蚀则通过HBr和O2(一般He稀释为30%)进行刻蚀。当刻蚀完成后,必须用湿法清洗除去晶圆侧壁上的沉积。单晶硅刻蚀和其他等离子体刻蚀最大的差异在于没有底层,因此无法利用光学信号方法决定终点,一般利用计时决定。

单晶硅刻蚀反应室的墙壁上会有硅、溴、氢和氟元素形成复杂的化合物沉积。为了控制粒子污染,这些沉积必须定期使用氟等离子体清洁。与其他清洁过程一样,清洁之后的适应工艺过程是必需的。

多晶硅刻蚀

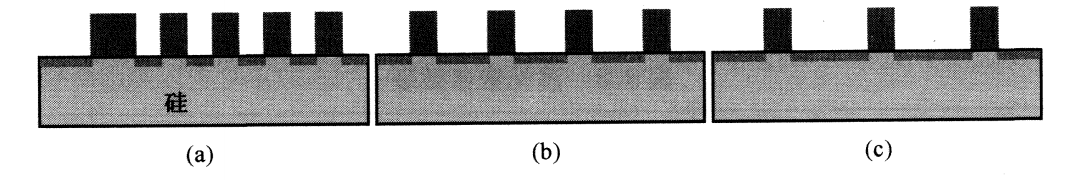

多晶硅刻蚀是最重要的刻蚀过程,因为它决定了晶体管的栅极(见下图)。一般栅的多晶硅刻蚀关键尺寸(CD)是所有刻蚀中最小的。一般所谓的多少微米节点技术,就是指关键尺寸CD是多少微米。

当特征尺寸缩小到纳米技术时,栅的关键尺寸CD和技术节点不再一致。技术节点主要是由栅极图形化间距决定的。技术节点的定义对不同的器件也不同。NAND快闪存储器技术节点是半间距:20nm的NAND闪存储器有40nm的WL间距,而通常20nm的栅极CD有20nm的CD间隙。

DRAM技术节点通常是WL间距的1/3,33nmDRAM有99nmWL间距和约30nm的栅关键尺寸CD。CMOS逻辑器件的技术节点通常被定义为SRAM栅间距的1/4,因为栅极之间有一个接触。例如,在2008年国际电子器件会议(IEDM)上由IBM公司B.S.Haran等人发表的22nmSRAM器件有90nm栅间距和25nm的栅极CD。下图显示了NAND快闪存储器,以及DRAM和SRAM阵列晶体管的截面图。

审核编辑:刘清

-

基于嵌入式技术实现单晶硅测径系统的设计2020-10-04 2765

-

单晶硅片的应用及加工工艺流程2019-06-24 22427

-

全球单晶硅生产商排名2017-12-18 56305

-

单晶硅加工流程及其抛光硅片工艺流程2017-10-20 1825

-

单晶硅的制造方法和设备和分离单晶硅埚底料中石英的工艺2017-09-28 2097

-

单晶硅太阳能电池详细工艺2012-08-06 11575

-

n型高阻单晶硅欧姆接触工艺2011-03-08 3270

-

n型高阻单晶硅 欧姆接触工艺2011-03-02 2173

-

n型单晶硅退火工艺2011-03-01 3363

-

单晶硅电池生产工艺流程(一) (内部资料)2009-11-07 6012

-

单晶硅电池生产工艺流程详细介绍2009-11-04 2208

-

什么是单晶硅2009-04-08 12074

-

单晶硅与多晶硅的区别2009-03-04 5013

全部0条评论

快来发表一下你的评论吧 !