探究计算机存储器结构体系1

电子说

描述

前言

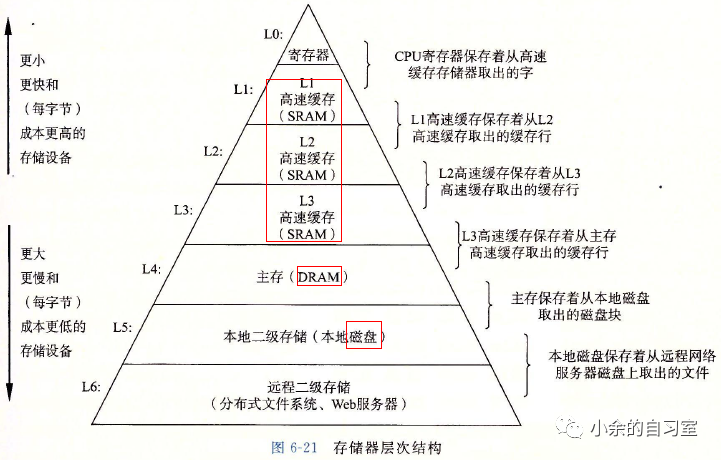

生活中经常听到这句话“一分钱一分货,哪有那么多又便宜又好用”,在计算机存储体系中,也是如此,存储速度越快的,也就越贵,而且是呈指数的贵。计算机存储呈如下金字塔排布。

理想情况下,我们肯定希望拥有无限大的内存容量,这样就可以立刻访问任何一个特定的机器字,但我们不得不认识到有可能需要构建分层结构的存储器,每一层次容量都要大于前一层次,但其访问速度也要更慢一些。

你是不是经常被以下名词弄得晕头转向。ROM/RAM/DRAM/SRAM/SDRAM/DDR SDRAM等等,下面,我尽力以上图为参考,从上到下,说明各个层次存储器的特点和区别,并对它们的工作原理做一些简要的说明

1.寄存器( Register )

寄存器是CPU中的一部分。它是一个高速存贮部件,可以用来暂存指令、数据和地址。每个CPU中有多个寄存器,例如8086CPU中含有14个寄存器。

寄存器是CPU的内部组成单元,是CPU运算时取指令和数据最快的地方。它可以用来暂存指令、数据和地址。在CPU的控制部件中,包含的寄存器有指令寄存器(IR)和程序计数器(PC)。CPU的算术逻辑部件中,包含的寄存器有累加器(ACC)。 下图中蓝色小框里面,全是寄存器。

2.高速缓存(Cache)与主存

2.1 引入cache的目的

计算机在运行程序时,首先将程序从磁盘读取到主存,然后CPU按规则从主存中取出指令,数据并执行指令,但是直接从主存(一般是DRAM)中读写是很慢的,所以引入了高速缓存(Cache)。

在程序运行前首先会试图将指令,数据从主存中读取到Cache中,然后在程序执行时直接访问Cache,如果指令和数据可以从Cache中读取到,那么就说是“命中(hit)”,反之就是“不命中(miss)”,miss情况下需要从主存中读取指令或者数据,这样会直接影响CPU的性能,所以命中率对CPU来说至关重要。

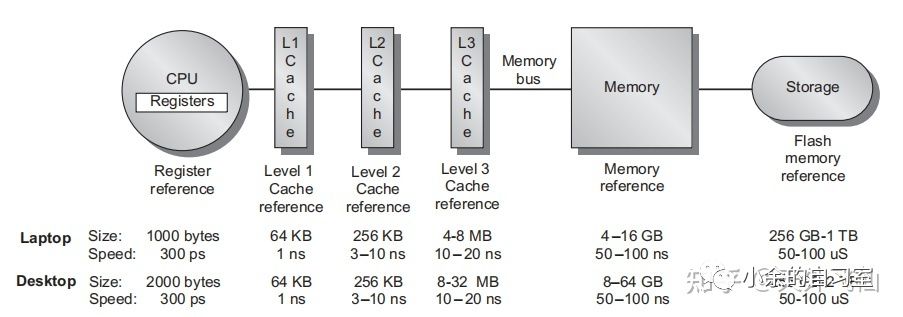

现代处理器一般有三层cache,分别称为L1 cache、L2 cache、L3 cache。L1 cache离CPU核最近,存储信息的 读取速度接近CPU核的工作速度 ,容量较小,一般分成I-cache和D-cache两块,分别存储指令和数据;L2 cache比L1更远,速度慢一些,但是容量更大,不分I-cache和D-cache;L3更慢、更大,现在流行多核处理器,L3一般由多个处理器核共享,而L1、L2是单核私有的。

实际上cache是一个广义的概念,可以认为主存是磁盘的cache,而CPU内cache又是主存的cache,使用cache的目的就是伪造出一个容量有低层次存储器(如磁盘)那么大,而速度又有寄存器(如通用寄存器)那么快的存储器,简单来说就 要让存储单元看起来又大又快 。

2.2 cache的理论基础

cache之所以能work,主要基于两个认识,即程序运行时数据具有时间局部性和 空间局部性 。

时间局部性是指一个数据如果当前被使用到,那么接下去一段时间它很可能被再次用到;空间局部性是指一个数据如果当前被使用到,那么接下去一段时间它周围的数据很可能也会被用到,比如数组。

2.3 Cache的组成方式

cache容量较小,所以 数据需要按照一定的规则从主存映射到cache 。一般把主存和cache分割成一定大小的块,这个块在主存中称为 data block ,在cache中称为cache line。 举个例子,块大小为1024个字节,那么data block和cache line都是1024个字节。当把主存和cache分割好之后,我们就可以把data block放到cache line中,而这个“放”的规则一般有三种,分别是“ 直接映射 ”、“ 组相联 ”和“ 全相联 ”。

直接映射

直接映射采用“ 取模 ”的方式进行一对一映射。举个例子,如果cache中共有8个cache line,那么0、8、16、24…号data block会被映射到0号cache line中,同理1、9、17….号data block会被映射到1号cache line中。

组相联:

直接映射中主存中的每一个data block都有一个确定的cache line进行映射,这是有缺陷的。当程序连续读取0、8、0、8号data block的数据时,因为只有一个cache line供映射,所以当第二次读取0号block时,第一次读到cache中的0号block早被顶替出去了,这时候又会产生miss,miss会极大地影响执行效率。

为了解决上面的问题,提出使用“组相联”的方式。

根据上图我们很容易发现比起直接映射,组相联翻倍了block可以映射的cache line的数量,图上数量为2,我们称每两个cache line为一个cache set。

全相联

全相联是极端的组相联,即cache只有一个cache set。每一个data block都可以存进任何一个cache line。下图是对应关系。

2.4.RAM与ROM

计算机中按存储类型划分为 随机存储器 (Random Access Memory, RAM)和 只读存储器 (Read Only Memory, ROM)

-

(1) 随机存储器 (Random Access Memory, RAM)

RAM是一种可读/写存储器,其特点是存储器的任何一个存储单元的内容都可以随机存取,而且存取时间域存储单元的物理位置无关。

-

(2) 只读存储器 (Read Only Memory, ROM)

顾名思义,ROM只能对其存储的内容读出,不能对其重新写入。因此,通常用它存放固定不变的程序、常数、汉字字库等。存放在ROM设备中的程序通常称为固件(firmware)。比如我们计算机的BIOS,就是存放在ROM中的。 随着半导体技术的发展,出现了可编程只读存储器(Programmable ROM, PROM)、可擦除可编程只读存储器(Erasable Programmable ROM, EPROM)及用电可擦除可编程只读存储器(Electrically Erassable Programmable ROM, EEPROM)。近年来还出现了闪速存储器(Flash Memory),它基于EEPROM。

高速缓存和主存都是RAM(Random-Access Memory,随机访问存储器),它分为静态的(SRAM)和动态的(DRAM),分别对应高速缓存和主存。

-

计算机存储器的分类及其区别2024-09-05 6212

-

探究计算机存储器结构体系22023-03-30 1652

-

计算机数据存储的原理是什么2022-01-25 2215

-

计算机体系结构的相关资料推荐2022-01-07 1169

-

计算机体系结构的硬件存储器简单介绍2021-12-23 1343

-

微型计算机和单片机的基本结构2021-11-22 1950

-

怎样为计算机去设计一个主存储器呢2021-10-22 1264

-

计算机的存储器采用分级存储体系的目的是什么2021-09-17 3854

-

计算机存储器的新技术描述2021-09-09 1632

-

计算机存储器的作用和分类说明2020-12-06 11781

-

计算机存储器的作用及分类2020-12-04 20983

-

计算机存储器的作用是什么?2019-09-17 3676

-

计算机的存储器主要作用_计算机的存储器的分类介绍2018-05-17 12540

全部0条评论

快来发表一下你的评论吧 !