最小化热插拔控制器输出短路时的短路电流幅度和脉冲宽度

描述

当热插拔控制器的输出短路时,内部断路器功能跳闸以断开电路。但在内部断路器响应之前,初始电流可能为几百安培。典型的热插拔控制器断路器延迟时间可能为200–400ns,由于栅极下拉电流有限,栅极关断时间可能为10-50微秒。同时,高短路电流流动。

应用笔记中描述的简单外部电路可以最大限度地减小初始电流尖峰,并在200–500ns内终止短路。

典型热插拔电路

我们来看一个使用MAX12的典型+6V 4272A热插拔控制电路(图1)。检查MAX4272规格,可以看到它包含慢速和快速比较器,跳变门限分别为50mV和200mV(在整个温度范围内容差为43.5–56mV和180–220mV)。应用通常放置在工作电流与跳闸电流比上的 1.5–2.0 乘数,我们选择 R意义= 5mΩ。允许 R 的容差为 5%意义,对于过载条件下,慢速比较器的跳变电流范围为8.28–11.76A,当发生短路时,快速比较器的跳变电流范围为34–46.2A。

图1.典型的热插拔控制器电路。

最小慢比较器跳变点比正常工作电流高38%,快速跳闸门限适合工作电流6-8倍的短路跳闸。

350ns快速比较器延迟意味着初始短路电流尖峰仅受该期间的电路电阻限制。此后,电流缓慢减小,因为 3mA 栅极下拉电流限制了 MOSFET M1 的 3–4nF 栅极电容放电速率,直到短路完全中断。当栅极从15V拉至近地电位时,短路电流在40–19μs内缓慢减小。

峰值短路电流

初始350ns期间的峰值电流取决于:

(a) 源ESR,(b)短路质量,(c)RSENSE的值,(d)M1的RDS(ON),以及(e)M1的ID(ON)。

将近似的最佳情况实用值分配给这些值,我们的总短路电阻为

(源ESR≈4 mΩ)+(短路≈3 mΩ)-(RSENSE,5 mΩ)=(RD(ON)≈4米Ω)≈16米Ω。

这可能会产生短暂的峰值ISC≈750A,这取决于电源的储能容量(750A将使具有2200µF电容器的低ESR背板在1µs内仅放电340mV)。在这种情况下,实际峰值ISC可能会被M1的ID(ON)限制在≈400A。

ID(ON)取决于VGS,因此在此期间检查电路以确定栅极-源极电压是有指导意义的。MAX4272包含一个内部电荷泵,可将工作栅极电压设置在VIN以上约7V。因此,当MOS导通时,VGS为7V。

做空的第二个影响是它实际上增加了VGS。考虑短路使电压阶跃等于M1的漏极-源极两端的全部输入电压的一部分。由于M1的RD(ON)约为估计的总短路电阻的1/3,因此施加≈12V阶跃的1/3作为VDS。通过从漏极到栅极的cdg和从栅极到源极的cgs的分压器作用,该步骤部分地转移到栅极。适当的计算表明,该额外的VGS为300–500mV,但在短路条件下进行的测量表明,其可能高达VGS=+3V。

到目前为止,可能很明显,高质量的短路会导致几百安培的流动几微秒到几十微秒。

我们可能希望在50μs<将峰值Isc限制在1A,但如果不增加一个非常快速的比较器和栅极下拉电路,这是不切实际的。但是,我们可以考虑一些简单的电路修改。

我们可以通过添加一个简单的外部电路来加速栅极放电,同时电流被I限制,从而将短路周期限制在≤1/2μs。D(开)内部快速比较器的前 350ns 响应时间为几百安培,或

我们可以使用稍微复杂的外部电路将峰值Isc限制在100A范围内的某个位置,持续时间≤200ns。

快速栅极下拉电路可限制高短路电流的持续时间

只需添加PNP达林顿晶体管Q1,即可最大限度地缩短大电流短路电流的持续时间,如图2所示。二极管D1允许栅极在导通时正常充电,但控制器的3mA栅极放电电流在关断时重定向到Q1的基极。然后,Q1在≈100ns内对栅极快速放电。因此,短路的高电流部分被限制在仅略高于350ns快速比较器延迟时间。

图2.具有快速栅极下拉功能的热插拔控制器。

快速限流电路

短路电流可限制在≈100A,持续<200ns,电路如图3所示。PNP晶体管Q1a-当电压过R时触发意义达到≈600mV - 驱动NPN晶体管Q1b快速放电M1的栅极电容。

图3.具有快速短路峰值电流限制功能的热插拔控制器。

C2放置在M1栅极至源极两端,以进一步降低短路期间施加到栅极的正瞬态阶跃电压;其值可能在 10nF 到 100nF 之间。

增加齐纳二极管D1以限制V一般事务人员低于MAX7提供的4272V电压。

虽然齐纳二极管在偏置在5mA时额定电压为1.5V,但它会限制V一般事务人员本电路的栅极充电(齐纳偏置)电流仅为≈3.4V,因为MAX100仅提供4272μA栅极充电(齐纳偏置)电流。限量V一般事务人员降低 ID(开)- 以 R 为代价D(开),因为数据手册显示 5.3V 时为 4mΩ,3V 时为 7mΩ,并允许更快地关断 M1。

齐纳D1和电容C2也可以在图1和图2的电路中发挥一些优势,以减少ID(开)在短路期间。

测试方法 - 产生短路

还有什么比制造短路更简单的呢?每辆英国跑车中至少有一个。

但是,具有足够质量和可重复性的短路用于测试则更具挑战性。为该实验评估了几种产生短路的方法。

机械开关总是在几毫秒的时间内产生弹跳触点闭合。旋转多叶开关似乎具有一定的前景,但由于几个大电流闭合产生的电弧,触点被侵蚀,人们想知道可重复性。

大电流继电器触点也会产生弹跳触点闭合,并在闭合过程中表现出可变的接触电阻。

评估的可控硅整流器的电流上升率不太令人满意。

大电流汞置换继电器被认为是最佳方法,但结果并不令人满意。发现具有指定电阻为 60mΩ 的 600A 4V 汞继电器在触点启动时的初始电阻为 40mΩ,随着电流脉冲的进展,在 4μs 的时间内悠闲地松弛至 15mΩ。

手动操作短路连杆可提供随意、间歇且不可重复的接触 - 也许最接近英国跑车的理想!但是,可以实现非常陡峭的电流波前。最后,这是最有效(也是最经济)的方法,尽管接触侵蚀限制了具有可重复结果的闭合次数。

最有前途的实验室质量方法是使用由多个高输出CMOS施密特线驱动器驱动的多个并行布线低RD(ON)NMOS晶体管。由于时间和资源有限,没有采用这条路线。

具有陡峭电流波前的真正的低电阻短路在实验室中通过机械手段难以持续产生。几乎可以肯定的是,在工作电路中会出现意外短路。

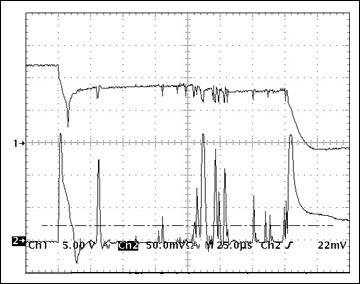

典型的手动短路会产生电容放电电流和电压波形,如图4所示。记录5V/div.短路输出电压的上部曲线显示,电容在大部分时间标度(25μs/div.)内放电不到一半。下方记录25A/div.短路电流的曲线清楚地显示了触点的间歇性。

图4.参差不齐的机械短路波形。

创建ESR低于5mΩ的电源也不容易。然而,为了创建一个4–5mΩ的低ESR电压源,仔细测量显示440A短路期间的压降为100mV,花费了大量精力。该电压源采用一个 5500μF 计算机级电解电容器、一个 3.3μF 多层陶瓷电容器和六个 100μF 特种聚合物铝电解电容器并联,直接安装在由 10A 电源驱动的电路输入端。

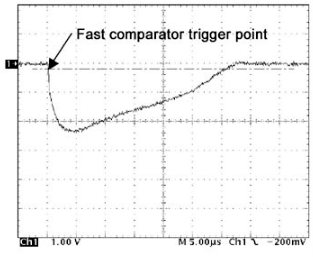

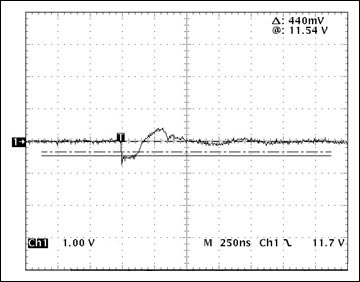

短路电流波形

图1的未改变电路表现出短路电流波形,如图5所示。波形看起来是反转的,因为测量是检流电阻RS两端的电压,示波器在测试电路的+12V输入端接地。RS为6mΩ,电压标度为1V/格,峰值电压为2400mV或400A。当前的波前并不像接触更好的那样陡峭。

图5.400A 未改变电路中的峰值短路电流波形。

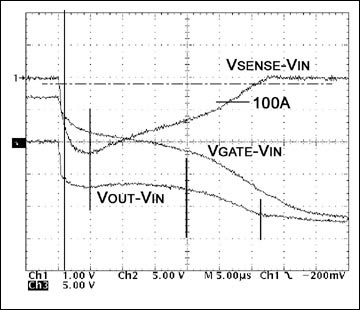

查看图6的电压波形也很有启发性,其中短栅极和M1栅极电压波形的输出电压与RS两端的电压相结合。所有电压均以+12V输入为基准。

图6.未改变电路中的短路电压和电流波形。

VOUT-VIN波形显示,VOUT在短路期间下降7V,表明短路电阻仅略小于总电路电阻的½。较低电阻的短路可能会产生高于400A的峰值电流。相同的波形表明,在最初的300ns期间,短路不是完全有效的;这有助于缓慢下降的VSENSE波形。

VGATE波形显示初始VGS E7V,由于VOUT下降,在1µs时增加到近10V。Vgs在5µs时仅降至9V,在20µs时降至6V,在33µs时跌至4V。栅极的缓慢放电是由于只有3mA的放电电流可用。因此,在短路开始后的27µs下,短路电流仍为100A。

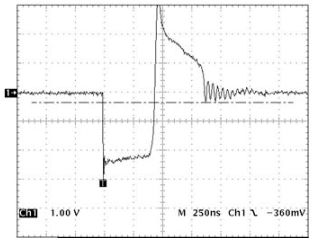

图2的快速栅极下拉电路可能不会降低初始短路电流,但PNP达林顿下拉电路会快速终止电流波形。图7所示的这种配置的短路电流波形仍表现出2400mV或400A的峰值电流,但在快速比较器触发≈50ns后,电流在370ns内终止。另请注意,短路电流波形非常陡峭,表明机械短路引发极佳。

图7.快速下拉电路中的短路电流波形。

当电路电容对输入电容进行再充电时,源电流反转,在+12V输入端产生轻微的正过冲。

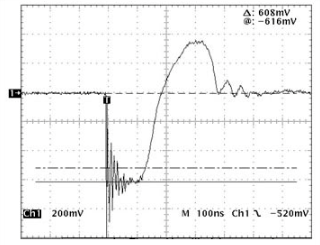

图3所示的快速短路峰值电流限制电路可有效限制峰值电流和短路引起的电流持续时间。图8所示RS两端记录的电压在600mΩ中峰值约为100mV或6A。短路电流终止非常迅速,电流脉冲在 200ns <完全终止。

图8.改进的热插拔控制器电路中的短路电流脉冲。

如图9所示,该技术将背板电源干扰降至最低,其中测试方法部分描述的+500V电源上的峰值电压干扰为< ±12mV。

图9.图3所示电路短路引起的背板干扰。

请注意,陡峭的电流波前再次表明非常高质量的短路引发。不幸的是,要复制这种陡峭的短路波形并不容易。

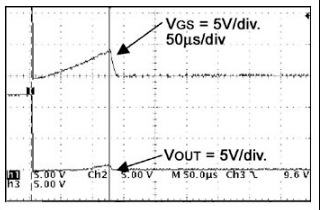

然后会发生什么?

PNP-NPN检测/下拉电路快速中断短路电流(然后断开),以至于MAX4272快速比较器没有足够的时间触发(响应时间350ns)。图10显示了500µs周期(短路启动后450µs)内的VGS波形。由于100µA的栅极充电电流仍然有效,已放电的栅极开始上升。大约130µs后,栅极充分增强(3V),VOUT上升到大约1V,短路电流再次开始流动。充电足够慢,以至于快速比较器在33A(200mV/6mΩ)时触发,IC通过关闭和锁存OFF来执行其工作。

图 10.V 的压缩时间视图一般事务人员在短路条件下。

总结

所讨论的两个电路中的任何一个都将通过最小化热插拔控制电路短路时的能量耗散来保护背板电源。图2中更简单的电路大大缩短了短路电流流向略小于500ns的周期,而图3中稍微复杂的电路将峰值短路电流降低到100A,并将脉冲宽度截断到200ns以下。

这两种技术都可以应用于大多数热插拔控制器电路。

个别测试结果将根据电源的阻抗、短路的阻抗,尤其是短路本身的质量和攻击时间而有所不同。

审核编辑:郭婷

-

脉冲宽度调制(PWM):工程机械控制器的常见技术2024-03-06 2466

-

为什么工程机械控制器需要脉冲宽度调制功能2024-02-23 1335

-

脉冲宽度(PWM)控制器电路原理图2023-12-05 4861

-

最小化热插拔控制器中的短路电流脉冲2023-03-17 1734

-

你知道热插拔时的短路电流危害有多大吗?2019-03-18 114

-

什么是脉冲宽度_脉冲宽度是什么意思2017-11-14 101222

-

脉冲漏极电流IDM及短路保护2016-08-24 6708

-

热插拔控制器构成限流电路2009-11-01 2196

-

低成本脉冲宽度控制器电路图2009-06-26 703

-

可由逻辑控制输出脉冲宽度的单稳态多谐振荡器2009-03-29 625

-

脉冲宽度受起动脉冲宽度控制的脉冲发生器2009-03-23 581

全部0条评论

快来发表一下你的评论吧 !