浅谈芯片低功耗的设计实现

电子说

描述

众所周知,随着芯片越来越大,功能越来越丰富,以及移动市场的切实需求,低功耗的芯片设计,越来越受到推崇。这里,结合多年的低功耗设计经验,把一些理念和方法,分享给各位。

通过一些理论书籍,大家都知道功耗的来源主要分为两种,一种是动态,一种是静态。

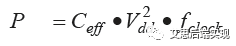

先来看一下,动态功耗的计算公式为,

dynamic power = switching power + internal power

switching power 计算公式为:

由此可知,动态功耗和频率、关断时的负载电容以及电压的平方成正比,换言之,可以通过,改变频率、负载电容以及电压来改变动态功耗。

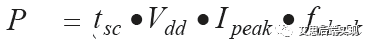

internal power 计算公式为

这里的tsc指的是NMOS/PMOS internal短路的时间。Ipeak指的是整个短路电流和导通电流的总和。

在实际的std-cell library里,工具使用了一个简化的查找表方式来处理internal-power,示例如下

P = func(input_transition, input_pin_condition, output_capacitance)

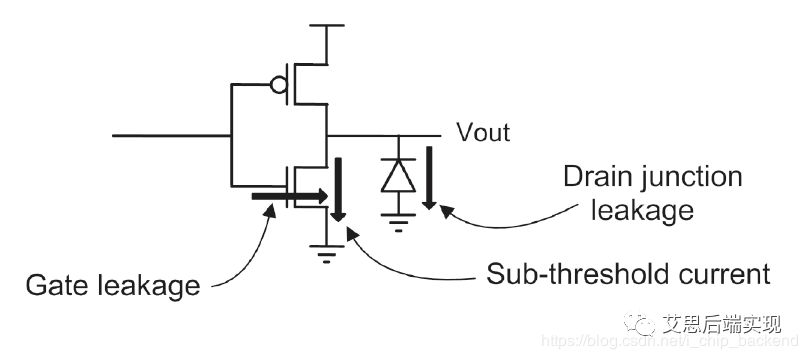

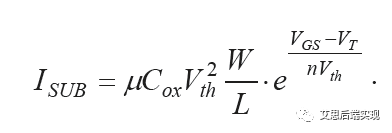

漏电功耗(leakage power)的计算模型

对应的漏电电流计算公式是:

这里的Vth, CoxW/L都是工艺相关,不可以调整,Vgs就是VDD,Vt指的是阈值电压。可以看到,阈值电压越高漏电功耗就越低,但是由于工艺复杂的增加,阈值电压越高的器件,对应的翻转速度就会变慢,导致影响性能

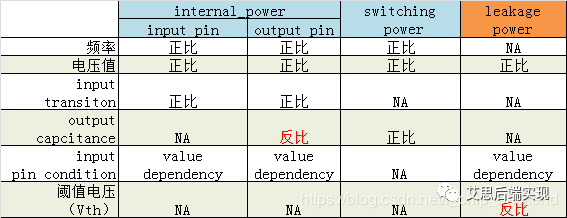

基于以上的理论,可以推导出下表:

下边就一起来看一下,目前的设计领域里边流行的那些降低功耗的技术手段吧。

clock gating

这个是一个在综合器里非常常用,也很通用的手段。总而言之,clock gating不但可以优化动态功耗,同时还可以优化面积(具有漏电功耗提高的可能),这里也有一些别的数据作为参考

… reports an area reduction of 20% and a power savings of 34% to 43% depending on the operating mode

综合工具在自动插入clock gating的时候,把原有的data上的通用逻辑加以整合,挂到了clock 的EN控制端,这样就可以大幅度的节省面积,尤其是在多位宽的总线。反言之,在非常窄的总线上,clock-gating在面积和功耗上不一定会有效果,譬如小于三位的总线。

工艺演进

随着晶体管的尺寸越来越小,三极管导通所需要的电压也就越来越小了,从上边的表哥里边可以看到,降低电压,可以有效改变动态功耗的处境。

从40/28nm的0.99v到现在7nm的0.7v,通过改变工艺都可以有效降低动态功耗。相反,对于相同尺寸的die,工艺的提高预示着可以放置更多的管子。

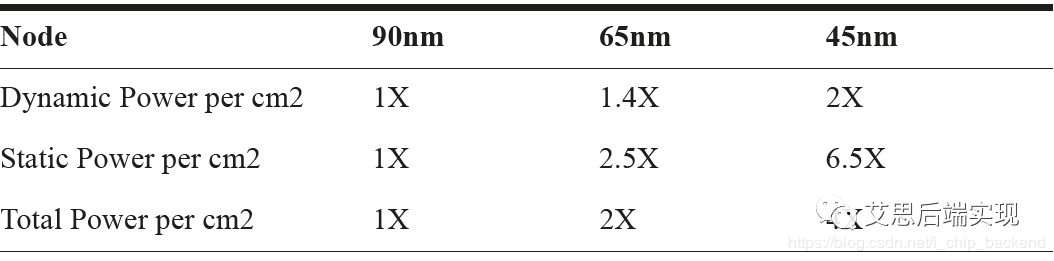

芯片的功耗随着工艺的提高,呈现出整体放大的趋势,尤其是漏电功耗,如下图

先进工艺的性能和速度大幅度提高,追击先进工艺是大势所趋,但是相应的,现代芯片的功耗挑战,会比以往来得更猛烈。

power gating (可关断电源)

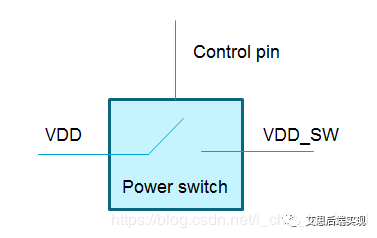

电压降低了,动态功耗确实可以变小,但是Vdd和Vth的差值会变得更小,Vth (阈值电压:MOS导通时所需要的的电压)更不可能一直毫无代价降低,所以,在实际的实现中,使用Switchable Power domain的方式,来整体关断某个或者某个区域、层级的器件,从而来降低整体静态功耗。这个实现电源控制的器件,就叫做power gating。

原理很简单,就是在当前的std-cell的PG rail上面加一个开关,通过外界信号来控制,从而达到可以std-cell电源的目的

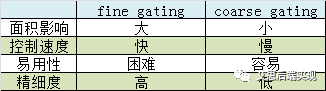

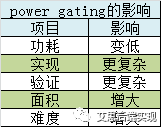

仔细想一下,这种结构可以所在std-cell的内部,也可以做在power rail上,前者通常被叫做fine gating,后者会被称作coarse gating。第一种的设计效果更好,甚至可以具体到某一个std-cell的电源开关控制,但是std-cell面积会变大。第二种,显而易见,如果使用在rail上,精细度会变差,但是,面积会很有优势,具体的实现方法也会简化。具体的比较如下表:

结合实际,在正常的使用中,并非所有的std-cell都需要单独控制,大部分都是一个功能模块的整体调配,所以现在很多设计里边都会使用coarse gating而非fine gating的实现方法(如果真的使用fine gating,不知道后端实现工程师会不会咬人)

模块关断的方法可以大幅度降低leakage,但是也会带来一些新的挑战,主要是后端实现的时候:isolation,power switch 以及PG route都会有很大的变化。

除此之外,前端的low power仿真也需要格外注意,如果某些scenario没有考虑好,核心模块在不期望的时候被关断,那么会引起系统性问题的。具体加下表:

动态电压和频率调节(Dynamic Voltage and Frequency Scaling)和自适应电压调节Adaptive Voltage Scaling (AVS)

在当下,为了节省功耗,各位工程师也是拼了。在后端实现的不断调整和改变的同时,前端的TX们也没有闲着。DVFS就是一个基于设计,功能原理的有效降低功耗的一个典型方案。

在芯片的实际使用中,真实的使用场景会比较复杂,就拿手机而言,譬如

用户待机的时候,只需要网络连接可能就足够了

听歌的时候可能是不需要屏幕的支持

用户在拍照的时候网络的功能需求也不是很强烈

当你玩游戏的时候,CPU可能就要调度所有的硬件来支持游戏的流程运行,

通过不同的场景,芯片基于用户需求来适当的调度各个功能的使用和性能调节

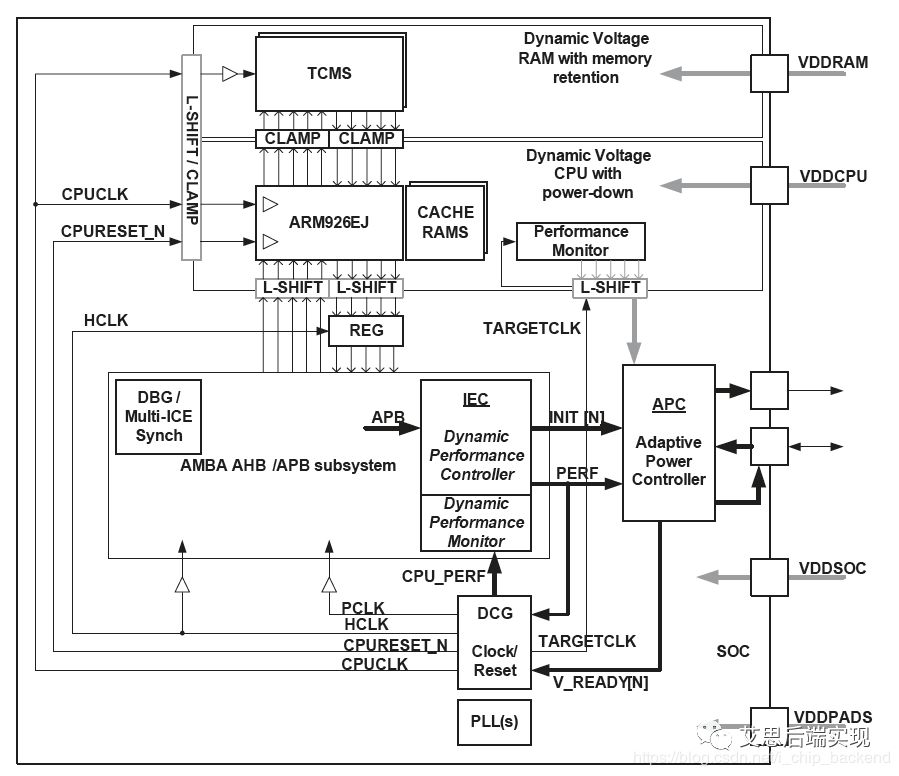

这个示例是一个UART的构造框图,基于这样的一个逻辑架构,规划出不同的使用场景,从而可以展现出不同场景下面所需要的电压和频率。

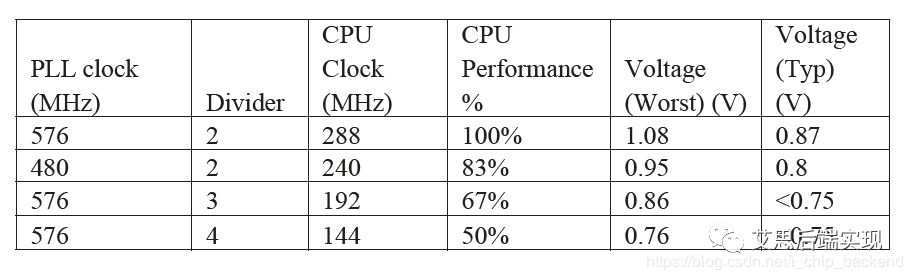

最后可以定义出一个类似上边的一个表格,在系统判断出不同的使用场景后,就会配置出不同的电压和频率值,从而达到不同场景下的功耗优化的可能,这也就是常说的DVFS,类似于一种对于预定义场景的一种查找表的操作。

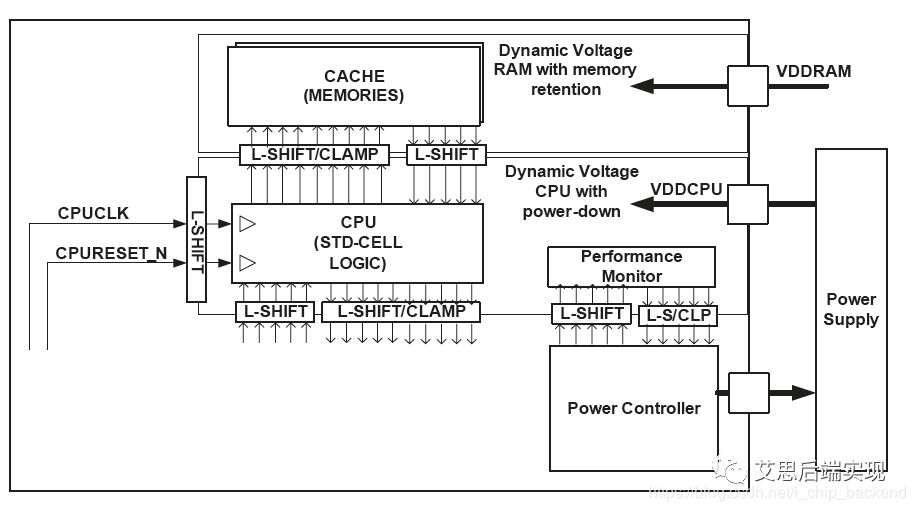

AVS是在DVFS上边更为先进的一种调整方式,框图如下:

和DVFS的简单查找表不同,这里会在系统里边集成一个PM(Performance Monitor),对于系统的运行进行实时监控,通过判断,动态的调整电压和频率,这里可以引入一些自学习的功能,从而根据不同用户的使用习惯,来提供更为细致的自定制服务。可以设想,愈发细致的个性化服务,加之自学习的预判功能,都可以进一步的提高电源功耗的优化。

Vt cell的应用

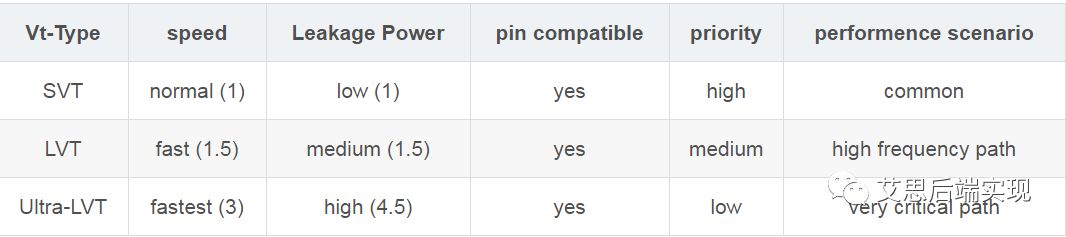

从上一篇文章可以看到,不同Vt下的cell特性是不同的,现在的工艺都会提供不同倾向的Vt库,见下表

可以看到,合理使用不同的Vt cell可以满足不同PPA的需求,在使用过程中,应该优先使用SVT的cell,而后是LVT,最后万不得已的时候再使用ULVT(ULVT的leakage可不是一般的大啊,一般会达到SVT的四到五倍的量级)

工具可以完美支持mix-Vt的设计。工具的策略是,在功耗优化的过程中,根据用户设定的Vt等价置换规则,在不影响timing的情况下,选择leakage小的cell,这样在兼顾性能的时候可以满足power的需求。

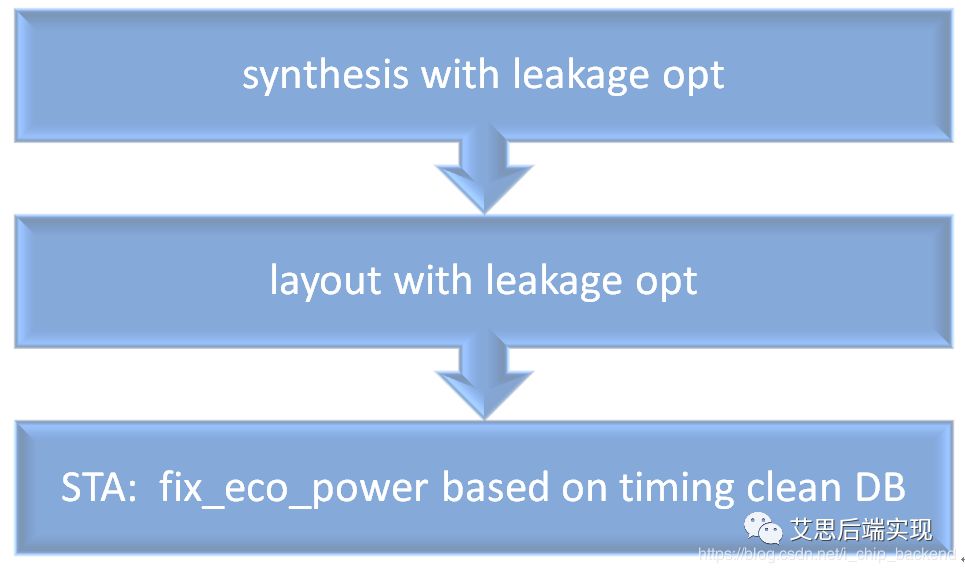

由于,后端实现的时候,通常由三个阶段需要用到这个技术手段,这里给出一个通常的应用场景供大家参考

秘籍:一定要做最后一步,效果会非常显著,可以有效地提高leakage power。

版图优化

在版图实现当中,后端实现的工具是非常灵活的,低功耗的设计当中,经常会使用到power-domain和voltage-area这些技术来优化power,简单的讲,通过UPF,在设计里边定义一些switch-off power和always domain,在某些功能不使用的时候,就把SW domain关掉,这个时候,SW里的power-gating cell的输出会呈现出一个无线接近电源(footer power-gating)或者地(header power-gating)的状态,从而理论上确保了SW domain的leakage是零(但是,这是指理论的,由于power gating cell本身会有漏电的问题,所以零的漏电只是理论上的)。

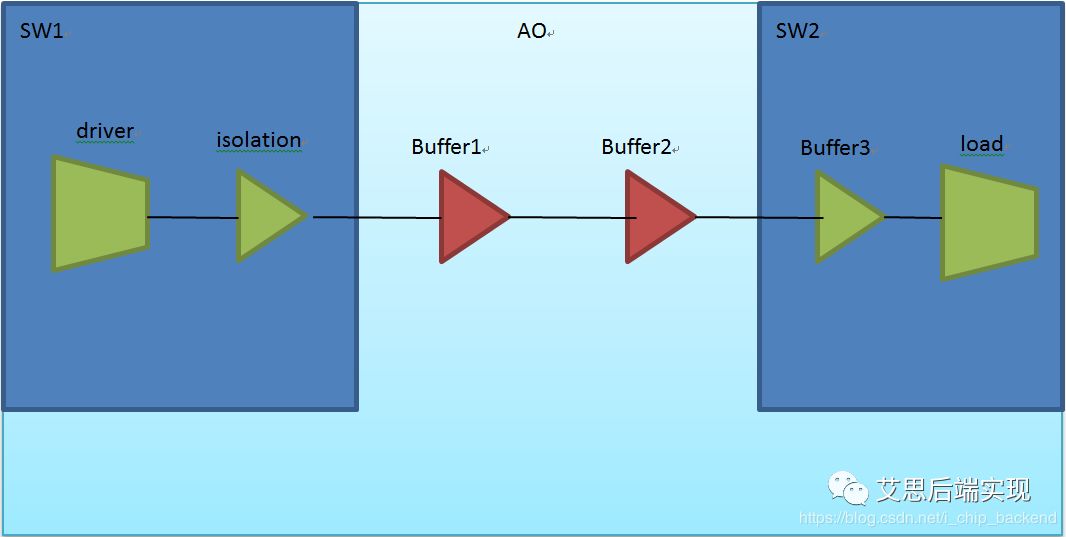

这里可以引申出一系列的思路,版图工程师可以尽可能的让更多的cell放到SW domain,从而在实际使用的情境下,可以拿到更好的功耗。看一下这个例子:

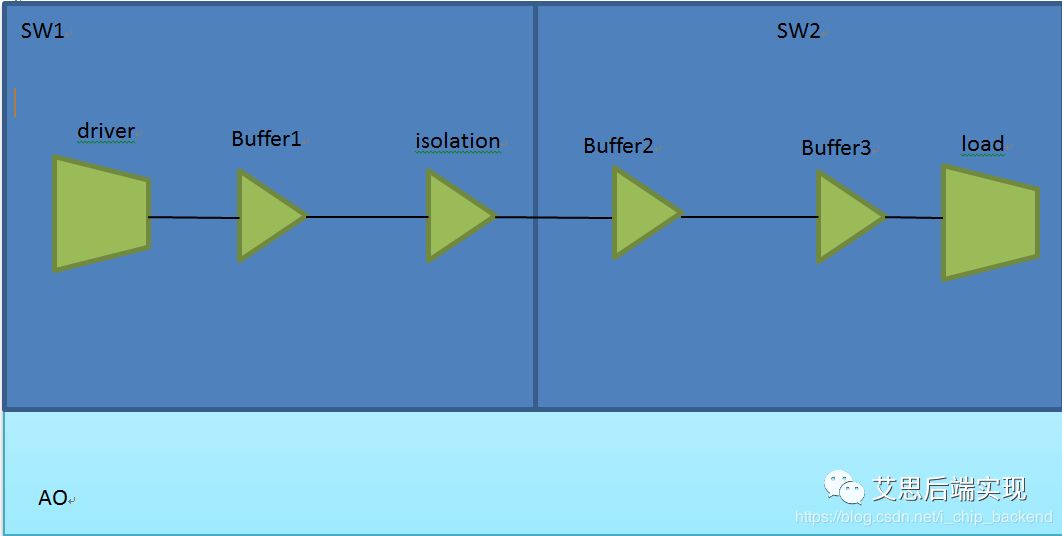

一条路径,从SW1出发到达SW2,中间一共有四级,其中SW里边有一个buffer和一个isolation,AO里边,有两个buffer ,从power上讲,在SW1和SW2同时关断的时候,这两个AO的buffer,不会有任何的动态功耗(dynamic power),这是因为SW1的isolation的输出已经被钳位(clamp)到无效态(一个常值),但是这两个buffer的leakage power是不能省略的,所以下图的floorplan,从power优化上来讲一定是个更好的选择

可以看到,中间的级数没有发生改变,但是之前的buffer1和buffer2,都已经被放置到了SW domain了,这样,在SW关断的时候,这两个buffer的leakage power就是零(理论上)。这里只是一个连接和两个buffer的示例,实际中VA之间的连接非常复杂,通过版图的优化调整,可以让出更多的leakage power。

低功耗设计是一套完整的理论体系,从原理、代码、UPF、综合、版图等等,每个步骤的一点点提高,都会带来不同程度的优化,勿以优化小而不为,点点滴滴的进步就会造就更加节能的芯片实现。

审核编辑:汤梓红

-

超小蓝牙模组,远距离,低功耗#蓝牙芯片 #低功耗蓝牙 #物联网 #硬声创作季fly 2022-08-23

-

浅谈CC2640超低功耗无线MCU2016-03-08 4229

-

无线模块如何实现低功耗2019-12-12 8540

-

怎么实现低功耗单芯片高性能音频CODEC的设计?2021-06-03 1664

-

蓝牙低功耗常见的应用场景及架构2021-06-15 2345

-

怎样实现芯片低功耗的设计?2021-09-28 1533

-

低功耗硬件电路设计中电源芯片选型2021-11-11 2301

-

时钟芯片的低功耗设计研究2011-10-08 2924

-

超低功耗设计技巧与实现2012-01-18 935

-

EPSON低功耗芯片2017-09-20 907

-

基于超低功耗设计技巧与实现2017-10-15 997

-

如何使用Freeze技术实现低功耗设计2021-02-14 2708

-

低功耗蓝牙芯片的应用可显著降低功耗和成本2021-03-05 1874

-

浅谈电源芯片选型之低功耗2021-11-06 1457

-

STM32与FreeRTOS实现低功耗2021-12-07 1204

全部0条评论

快来发表一下你的评论吧 !