Chiplet的通用,遥遥无期

电子说

描述

芯粒(Chiplet)的迷你联盟正在整个行业中兴起,这是由于在紧迫的市场窗口中增加定制化需求以及在硅中得到验证的硬化 IP 组合的推动。

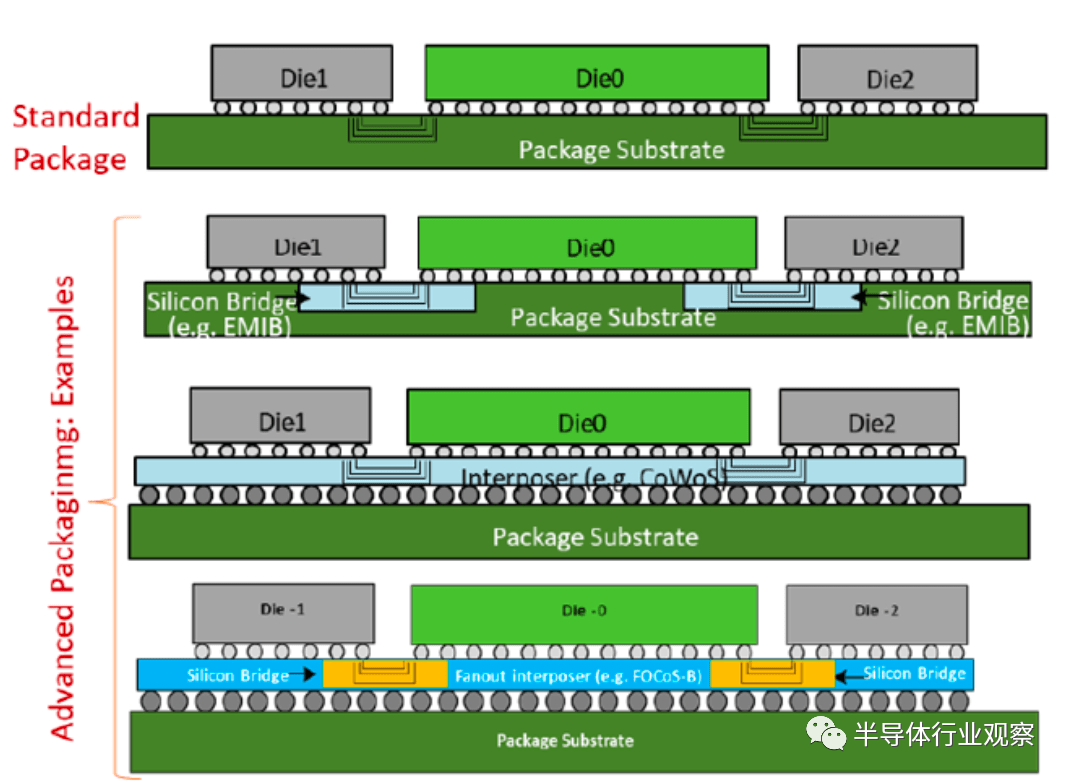

这些松散的合作伙伴关系正在努力为高度特定的应用和终端市场开发类似乐高积木的集成模型。但它们都是从小规模开始的,因为事实证明,很难为可以在各种用例中工作的芯粒创建商业市场。使用标准化方案连接芯粒是一回事,例如通用芯粒互连高速 (UCIe),或使用英特尔或三星开发的桥接器。期望它们在不同计算负载和操作条件下的异构设备中工作是另一回事。

图 1:UCIe 开放芯粒生态系统

了解不同的芯粒如何相互交互,以及它们在不同用例下的行为方式,很难预测。即使使用最好的仿真工具,也没有足够的数据,而且对于许多应用来说可能永远如此。但是,除非这些芯粒在其他组件和不同用例的背景下得到充分表征,否则可能会出现涉及热管理、各种类型的噪声、不同的压力和不一致的老化等问题,所有这些都会影响现场的可靠性。

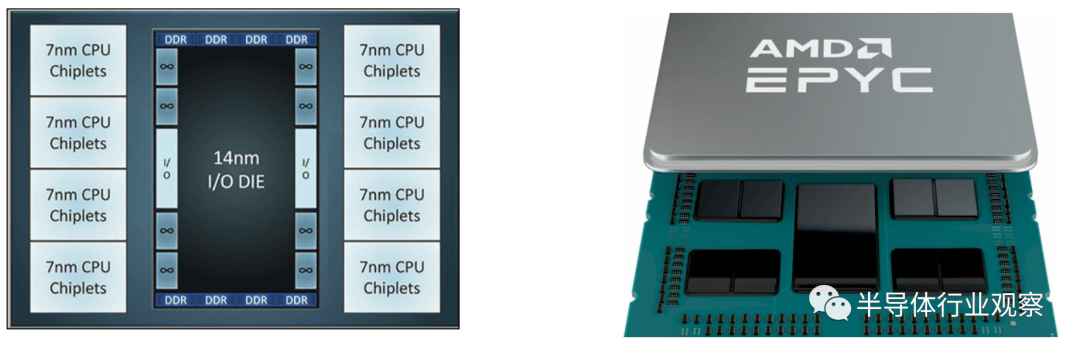

另一方面,芯粒已被证明在受控情况下工作得非常好。十年来,AMD 和 ASE 一直在芯粒和图形子系统方面进行合作。Marvell从 2016 年开始使用芯粒。Intel Foundry Services 正在为基于芯粒的数据中心客户定制系统。

图 2:AMD 的 EPYC 架构集成了不同的工艺技术

然而,所有这些公司都依赖内部采购的芯粒来创建本质上是分解的 SoC,他们可以完全控制系统。现在的挑战是开始开发芯粒和适合芯粒的架构,这些架构可以在任何供应商的设备上进行商业销售。

“在某些方面,我们正处于一个新时代,”日月光集团研究员兼高级技术顾问 Bill Chen 说。“优化是一种选择,允许这些选择对我们来说很重要。我们也处在一个开放共享的时代。芯粒、SiP、异构集成,我们从最困难的领域开始,也就是高性能计算。有两个原因。一是这是最需要它的市场部门。其次,这是开发这些产品的地方,也是解决这些问题的技术所在。然后我们可以转向通信和其他市场,例如可穿戴设备和医疗应用。”

这就是不同供应商开发的商业芯粒将适合的地方。但正如处于这一转变前沿的公司将证明的那样,从不同供应商采购芯粒增加了一系列全新的挑战。即使这个想法在理论上是有意义的,它也从未实现过。

小型组织(Small consortia)是真正进步的最初迹象。晶圆厂、封装厂和大型芯片制造商正在与具有深厚领域专业知识的合作伙伴合作,使用各种安排来确保各种基本组件协同工作并可以根据上下文进行表征。桌面上有许多不同的方法,从少数合作伙伴到基础更广泛的基础设施,例如连接结构或标准加上严格的设计规则。但对于所有相关人员来说,这是一个谨慎的、边学边做的过程。

“三星电子正在构建自己的生态系统,”三星电子知识产权和生态系统营销总监 Kevin Yee 说。“即便如此,我们也学到了很多我们没有想过的事情。从技术角度来看,chiplet 已经存在并得到了验证。但目前,它们都是垂直整合的。因此,芯粒作为一种解决方案存在并且正在发挥作用。现在的挑战是芯粒作为市场或业务。这就是每个人都在努力的方向,并且可能会有一个临时步骤。每个人都将首先开始构建自己的微生态系统,以确保其正常运行。所以一家公司会做一个 I/O 芯片,一个会做互连,一个会做数据芯片。您将确定如何构建它以及如何构建可行的东西。但最重要的是,您可以在 6 个不同的计算芯片或 10 个不同的 I/O 芯片之间进行选择,选择您的内存芯片,然后将它们放在一起。在那之前,我们还有很长的路要走。”

同样,专注于先进封装和芯粒设计的 Palo Alto Electron (PAe) 正在率先成立自己的芯粒联盟,其中包括 Promex Industries(系统集成)、Thrace Systems(功耗分析)、Palo Alto Electron(先进封装和芯粒设计) )、iTest(可靠性和故障分析)、Hyperion(系统级设计、互连和高级封装)和 Anemoi Software(热求解器)。

“这是一个最低限度的可行生态系统,所有这些公司都在美国,”PAe 首席执行官 Jawad Nasrulla 说。“我们说,‘好吧,我们将寻找解决特定技术问题的小型企业和创新型初创公司。’ 例如,Anemoi Software 专注于芯粒的热建模。功率/热能是进行设计的关键支持技术。Palo Alto Electron 拥有构建 IC 的经验,在过去的七年中,我们一直在使用芯粒来做这件事。这些公司中的每一个都是某个领域的专家。现在我们需要学习如何与彼此合作。”

Promex Industries的首席执行官 Dick Otte对此表示赞同。“这些作品中的每一件都是多管齐下的。每个人都有一种能力,但每个人都拥有不到所有可能能力的 100%。所以真正的问题是,当我们有工作在这里滚动时,会有多少?我们需要多长时间去寻找一些支持或附加功能?到目前为止,这还不是问题。”

正在创建的一些芯粒本身就是模块或微型系统,而不是像特定 I/O 这样的独立 IP,至少已经完成了一些集成工作。但随着商业芯粒市场的发展,可能会有更多针对特定工作或功能的芯粒,而不是完整的子系统。这可以让客户在 chiplet 架构中添加可编程性和更多可定制性,而无需更改整体架构,这类似于英特尔和 Marvell 所走的道路。

“如果你看看小型、中型和大型汽车,每一种都需要完全不同数量的电子设备,” Fraunhofer IIS自适应系统部工程高效电子部门负责人 Andy Heinig 说。“芯粒让你变得更加灵活。但在未来,您可能能够将芯粒组合在一起以创建更大的芯粒。你可以用这种方式配置你的电子设备,几乎就像积木一样,以获得你对汽车的确切需求。”

这需要时间来发展。目前,许多 chiplet 制造商正在更高层次上解决这个问题。

“芯粒被分解成相对较大的块,”Promex 的 Otte 说。“这就像芯片设计师设计了单个芯片,然后有人必须将所有这些整合在一起并进行高级设计,不仅要集成芯粒,还要集成您正在使用的任何互连、基板或中介层技术。第三部分是这个组装服务,这是我们的角色。如果这被证明是一个非常成功的模式,并且我们能够为客户提供质量和良好的经济效益,那么它就有可能像滚雪球一样滚雪球并成为一项主要活动,我们将陷入更困难的问题,我们有一个许多项目在不同的州进行。这意味着不同种类的协调。现在的问题是寻找客户。稍后,将是零件的交付。”

01 重新思考老问题

多年来,整个芯片行业的普遍共识是,业务关系将是 chiplet 市场运作的一大障碍。然而,正如这些小型组织的努力所表明的那样,也存在许多技术挑战。虽然这些组织通常会选择一个“总承包商”来监督设计到制造流程的各个方面,但已经涉及很多步骤,随着芯粒变得更有针对性和功能更窄,还会有更多步骤。

“当你做芯粒时,心态必须改变,”Yee 说。“很多人仍然认为这就像构建 SoC。你现在真的在构建一个完整的系统。我怎么跟它说话?如何配置计算芯片?我必须有哪些边带信号?需要考虑固件。您是否设置为使用该固件并启动他们的计算芯片?现在有很多系统级的讨论涉及人们以前没有真正考虑过的问题。”

即使选择正确的封装也是一个挑战。“你有这么多不同的口味,” Synopsys的 IP 产品线高级组总监 Michael Posner 说。“你会想,‘哦,你应该能够将每一个都放在一个盒子里,也许可以想出一个适用于所有这些的单一 IP,但事实并非如此。你有不同的凸点间距、不同的性能和功率、不同的寄生效应和电源完整性问题。因此,不像我们传统上为 IP 做的那样,每个节点都有一个过孔,可能是南北或东西方向,我们最终有一个用于高级,一个用于标准,一个用于 RDL,因为技术的变化。我们需要在整个生态系统中开发的 IP 数量呈爆炸式增长,目前还没有明确的领导者。”

02 一些旧的东西,一些新的东西

当然,并非所有这些都是新的。使用先进封装的 OSAT 和代工厂至少解决了一些挑战,例如如何处理芯粒、如何确保这些芯片是KGD,以及各种互连方案,例如混合键合或微凸块。在 2.5D 实现中,HBM主要用作可与许多不同配置配合使用的芯粒。

“三星的封装技术在为三星代工厂提供完整解决方案方面具有显著优势,”Yee 说。“该团队从其在内存封装方面的领导地位中学到的东西可以应用于代工。HBM 是存储器领导地位的一个很好的例子,封装中的多芯片使代工芯粒成为可能。当我们转向芯粒时,您无法将制程和设计与封装分开。他们将齐头并进。当人们想到芯粒时,他们假设您将能够直接运行一个到另一个的连接。一般来说,这会奏效。实际上,如何路由慢跑或偏移?你有多少保证金?通过我们的测试车辆,我们正在进行测试以确定实际的路由路径,以确保高信号质量。”

还有一些行之有效的连接芯粒的方法,例如 UCIe、线束 (BoW)、硅中介层、桥接器,甚至混合键合。将来,这些方法中的一种以上可能会用于复杂的设计,从而为更多创新打开大门。

例如,Eliyan 是一家开发芯粒互连的初创公司,它专注于通过在芯粒的两侧构建物理互连层 (PHY) 来消除 UCIe 兼容设计中的中介层。“这消除了制造、热管理的任何复杂性,并使我们能够储存我们从旧的 MCM(多芯片模块)时代学到的所有东西,”该公司联合创始人兼业务主管 Patrick Soheili 说。“我们计划以我们的技术为基础构建一堆芯粒。所以我们会在一端使用我们的技术,在另一端使用一些其他东西,并将两个、三个或四个东西连接在一起。也许它们是 HBM 设备,也许它们是其他 I/O 控制器。”

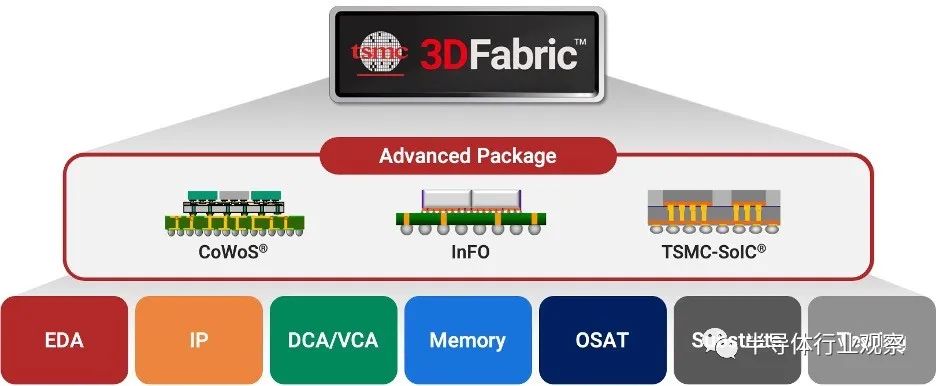

将设备连接在一起的可能方案的数量正在迅速增长。去年秋天,台积电推出了 3D Fabric Alliance,以在 3D 封装中连接不同的层和设备。“我们拥有 EDA、IP 和设计服务,我们还在增加内存合作伙伴、帮助我们组装这些设备的 OSAT 以及在 3D 中变得极其重要的基板,”台积电的总监 Dan Kochpatcharin 说。设计基础设施管理部。“这些设备可以有 10 厘米高,基板可以有 20 层或更多层。所以我们需要确保我们将他们的路线图与我们的路线图对齐,以便我们可以与他们进行交互,也许会有不同的材料一起工作。然后你必须考虑测试整个系统,这并不容易。所以我们正在与 Advantest 和 Teradyne 合作,以及 EDA 供应商。IP 在测试中很重要,因为我们需要针对可靠性进行设计。”

图 3:TSMC 的 3DFabric 生态系统模型

而这只是出现的一些通用集成方案的开始。在这个市场被整理出来之前还会有更多的东西,并且会有越来越多的证据表明什么有效,什么无效,以及一些从未被考虑过的新问题。例如,芯粒的不均匀老化会导致各种以前从未解决过的可靠性问题,特别是在预计设备可以多年保持功能的市场中。因此,随着芯粒和封装经济的发展,一个领域的成本节省可能会被另一个领域的成本增加所抵消,而随着芯粒模型的发展,客户今天支付的成本可能会变得不那么有吸引力。

Amkor Technology高级工程师 Nathan Whitchurch 表示:“我们看到越来越多的客户决定接受 TIM(热界面材料,只是为了让他们的设备能够正常工作)的成本。”那是行不通的。过去奇特的东西变得越来越不那么奇特了,比如烧结银类别,你最终会在盖子和芯片之间形成非常坚硬、高导热性的银合金基体。另一种会更软”

03 结论

芯粒是合乎逻辑的下一步,因为对于大多数芯片制造商来说,将所有东西缩小并塞进单个 SoC 的成本变得不经济。这让业界很多人都在考虑下一步,并且能够至少标准化软件包中的某些组件以创建定制解决方案是实现大规模定制的合乎逻辑的方法。

如果这种方法成功,它可能会改变设备进入市场的方式,同时允许以低得多的价格进行更多定制。因此,新架构的巨大性能提升将在更多的利基市场中出现,而无需从头开发 ASIC 或 SoC 的沉重代价。如果可以将一些自定义芯粒添加到架构中,那么适用于 80% 市场的产品可能仍会对其他 20% 的市场产生巨大好处。但是有很多细节需要先解决,芯片行业正在弄清楚这些细节。这些小型联盟是找出问题所在、可以标准化的内容以及领域专业知识将在此过程中扮演什么角色的第一步。

审核编辑 :李倩

全部0条评论

快来发表一下你的评论吧 !