RISC-V 体系结构特点和指令集介绍

嵌入式技术

描述

曾在苹果、特斯拉、Intel、AMD等多家公司担任高管的芯片大神Jim Keller在 2022 年的一次演讲中,宣称处理器的未来是属于 RISC-V 的。他认为,RISC-V未来将会超越现在的市场霸主 x86 与 ARM 。

当年 AMD 能先于 Intel 推出划时代的 64 位 x86 处理器,就是Jim Keller的功劳。Jim Keller后来把硅谷的大厂转了个遍,每到一处必推出震动业界的处理器产品。

能被芯片大神看好的RISC-V ,究竟是何方神圣?

01

RISC-V的缘起

此事要从计算机科学的圣地——加州大学伯克利分校说起。2010 年时,加州大学伯克利分校的 Krste Asanovic 教授、Andrew Waterman 和 Yunsup Lee 共同设计发明。RISC-V 也得到了图灵奖获得者 David A. Patterson 的支持,他可是计算机体系结构的权威大佬。 他们做这件事的初衷是便于开展教学工作。业界虽有成熟的 x86 与 ARM 架构,但二者的架构过于复杂,并且存在高昂的授权费用。不过这能难倒加州大学伯克利分校计算机系吗? 于是一个简洁、开放、免费的处理器体系结构 RISC-V 诞生了。RISC 是精简指令集计算机(Reduced Instruction Set Compute)的缩写,V 是罗马数字 5,是第五代指令集体系结构 的意思。所以它正确的读法应该是“risk five”。 RISC-V 在教学上便利的特点,其实也迎合了业界的强烈呼唤,所以短短几年内它就从学术走向了工业级应用。尤其是在 2022 年,RISC-V 概念引爆市场,这一年也称为 RISC-V 的元年。

展望未来,RISC-V 攻城略地的本钱是什么?我们从它的体系结构来管窥一二。

02

后来者居上:RISC-V 体系结构特点

RISC-V 体系结构最基础的特点有三个——开源、精简、模块化。这三个特点为何如此受到业界青睐?通过与 x86 、ARM 的对比最容易说清楚问题。

开源

RISC-V 采用 BSD 开源协议,既不会受到单一商业体的控制,也不会有商业上的纠纷,有利于大规模推广。这要感谢加州大学伯克利分校对计算机科学事业的慷慨贡献。 x86则是全封闭体系结构 ,只有 Intel 和 AMD 独享;使用 ARM 则要支付昂贵的授权费,也只有实力强大的厂商才玩得起。

精简

RISC-V 指令集和体系结构 设计说明文档只有几百页,而有些商业芯片则有数万页的文档。这说明RISC-V有着更强的可扩展性,这也是后发者的优势,可以摒弃掉很多繁杂冗余的设计,保留最实用的部分。

模块化

不同于 x86 与 ARM 这样的通用体系结构 ,RISC-V的用户可根据业务需求(例如弱计算、低功耗场景,或者智能化、高性能计算场景等)进行定制。

纵观 IT 历史发展,最初市场由“Wintel”联盟(Windows + Intel)双巨头主导。Intel 发布一款新处理器,微软就会升级软件把芯片的性能吃掉,行业大部分利润也就被如此收割。 随后移动互联网的崛起,主导者变为了“AAA”(ARM、Android、Apple)。以谷歌为代表的互联网公司兴起,依托于 Linux 这样的开源软件,他们摆脱了微软的控制。ARM 的授权生产模式,又孕育出了不少像高通这样成功的芯片制造企业。市场进一步开放,不再是寡头的时代。 现在如今,我们正在进入人工智能(AI)+ 物联网(IoT)的 AIoT 时代,市场将会百花齐放,那么主导者会是谁?我想那一定是尽早在 RISC-V 体系结构上进行布局的远见者们。 如果你不想错失这个未来最大的市场,要稳稳地站在风口上,就从《RISC-V 体系结构编程与实践》这本书开始学习吧。它包含了 RISC-V 体系结构、指令集、内存管理、实验环境搭建等内容,涵盖从理论到实践的完整过程。 点击封面,即可购书

我们先从 RISC-V 最具特色的指令集体系结构说起。

03

理解 RISC-V 的语言:指令集介绍

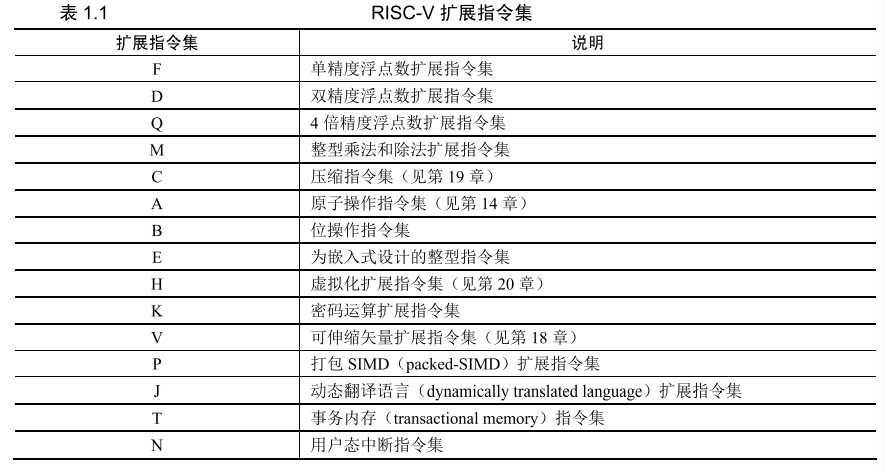

对于一台计算机来说,最基础的组成是什么?硬件是芯片,软件是操作系统。而对于处理器架构来说,最核心的部分是指令集体系结构(Instruction Set Architecture,ISA)。 指令集是计算机硬件与软件真正的交界处。它以指令的形式,定义了 CPU 可对外提供的操作,就像是 CPU 的语言;而 CPU 的执行又依赖外界向它输入的指令。再庞大的软件也是由文本形式的源代码,编译成一条条二进制指令,交由 CPU 来执行,从而构成我们今天的信息世界。 当前业界比较流行的指令集设计采用的是增量式方法,即增加新指令时,要做到保持向后二进制兼容。这看起来似乎没什么问题,但已经被弃用甚至是存在错误的旧有指令也要一并保留下来,这就会造成指令集无谓的庞大,变得臃肿、冗杂。 作为后发者的 RISC-V,自然就在设计之初,避免了增量式带来的问题,采用了模块化的设计方法。 模块化设计方法,就是设计一个最小集合和最基础的指令集。最小指令集可以完整地实现一个软件栈,其他特殊功能的指令集可以在最小指令集的基础上,通过模块化的方式叠加实现。 这也就是为什么 RISC-V 可以根据应用场景,实现差异化的定制。它在设计原则上就避开了摊大饼式的增量陷阱,而采用了搭乐高式的灵活拼装方式。 RISC-V 针对 32 位处理器的最小指令集是 RV32I,针对64 位的是RV64I。在 RV32I 和 RV64I 的基础上,RISC-V 还定义了一级扩展指令集。芯片设计者可以根据业务需求选择扩展指令集。具体描述如下表所示:

04

轻松上手:搭建实验环境

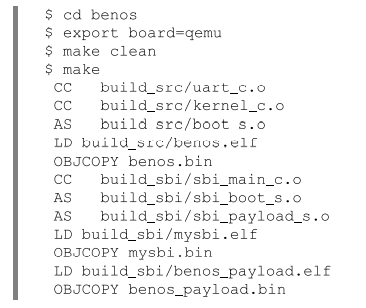

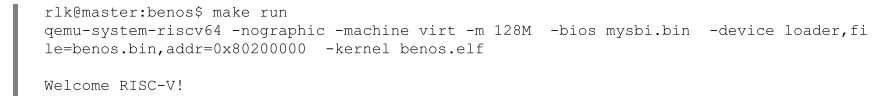

要想从入门到不放弃,动手实际体验是必不可少的。可能你会产生一个疑问,学习 RISC-V 是不是还要先买块开发板?那编译、开发、调试是不是门槛很高? 其实这不是必需的。《RISC-V 体系结构编程与实践》一书中给出了基于 QEMU 或者 NEMU 模拟器上进行实验的方法,而且作者团队奔跑吧 Linux 社区还提供了他们自研、开源的小型操作系统 BenOS。本书对初学者相当友好,可以说是“傻瓜式”的开局。 QEMU 是使用最广泛的开源虚拟机软件,也是做系统底层开发和嵌入式开发的必备神器。NEMU 则是由南京大学实现,用于教学的计算机指令集体系结构模拟器。由中科院牵头研发出的香山高性能 RISC-V 处理器,就使用了 NEMU 进行前期指令集和体系结构的模拟。 我们来看一下如何在 QEMU 上实现 RISC-V 版的“hello, world”吧。

准备工作

· 安装了 Linux 操作系统的主机。

· 从 GitHub 下载 BenOS 源码。

https://github.com/runninglinuxkernel/BenOS

· 在 Linux 上安装下列工具:qemu-system-misc、libncurses5-dev、gcc-riscv64-linux-gnu、build-essential、git、bison、flex、libssl-dev。

编译BenOS

运行

大功告成!就这么简单。

05

结语

目前市面上主流的技术架构是终端使用ARM 芯片,服务端使用 x86 的 CPU。但这样设计架构,企业就需要维护两套技术体系的研发,从资源使用角度来说相当不经济。 RISC-V 让全平台底层技术栈的统一有了希望。只需要一套技术体系,即可适应从处理器到操作系统、基础软件库、上层应用的研发工作。这也是芯片公司、互联网公司如此青睐 RISC-V 的重要原因。 目前我国在 RISC-V 体系结构上保持领先水平。香山处理器团队也参与了《RISC-V 体系结构编程与实践》的审校工作,为本书提供了更加权威、深度的技术细节内容。

编辑:黄飞

-

【RISC-V开放架构设计之道|阅读体验】RV64指令集设计的思考以及与流水线设计的逻辑2024-01-29 2149

-

【RISC-V开放架构设计之道|阅读体验】RISC-V基础整数指令集2024-01-31 857

-

RISC-V指令集的特点总结2024-08-30 1193

-

名单公布!【书籍评测活动NO.45】RISC-V体系结构编程与实践(第二版)2024-09-25 4457

-

RISC-V和arm指令集的对比分析2024-09-28 1707

-

【「RISC-V体系结构编程与实践」阅读体验】-- 前言与开篇2024-11-23 1423

-

【「RISC-V体系结构编程与实践」阅读体验】-- SBI及NEMU环境2024-11-26 1073

-

RISC-V指令集概述2024-11-30 1137

-

ARM的指令集文章集合2020-09-07 1978

-

什么是RISC-V? RISC-V指令具有哪些特点应用?2021-10-14 3125

-

Microarchitecture指令集体系结构2021-12-14 1964

-

已结束-【书籍评测活动NO.3】一本书带你了解谷歌、苹果等科技巨头都看好的RISC-V体系结构2023-02-20 56342

-

初探RISC-V—《RISC-V体系结构编程与实践》2023-03-28 1620

-

《RISC-V体系结构编程与实践》试读2023-04-03 1329

-

简单讲讲RISC-V指令集CPU的参数2022-08-07 5012

全部0条评论

快来发表一下你的评论吧 !