时序约束的相关知识(一)

描述

本章节主要介绍一些简单的时序约束的概念,主要包括:

四种时序路径

时序路径的约束语句

输入转换时间与电容输出负载模型

时序约束文件的简单编写

关键词:create_clock、 set_clock_uncertainty、 set_clock_latency、 set_clock_transition、 set_input_delay、 set_ouput_delay、 remove_input_delay、 report_clock、set_load、 set_input_ transition、 set_driving_cell

该章节在 DC 综合流程中的位置如下。

4 种时序路径

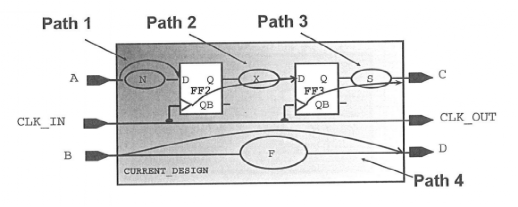

DC 进行时序分析时,都是基于同步时钟下的设计。 假设数据都在时钟上升沿到来 (launch) 或输出,则 DC 会将设计分割成 4 种时序路径,如下图所示:

Path1 指输入到寄存器的时序路径 (Input-to-Reg Path)

Path2 指寄存器到寄存器的时序路径 (Reg-to-Reg Path)

Path3 指寄存器到输出的时序路径 (Reg-to-Output Path)

Path4 指输入到输出的时序路径 (Input-to-Output Path)

这些路径的起点和终点必须是固定的类型,说明如下:

起点必须是非时钟的输入端 (input port other than a clock port),或触发器 (寄存器) 的时钟端。

终点必须是非时钟的输出端 (output port other than a clock port),或时序元件的非时钟输入端 (例如触发器的 D 端)。

正常的静态时序分析 (Static Timing Analysis, STA) 主要包括 3 个步骤:

1> 将设计分割成多个时序路径

2> 计算每条时序路径的延时

3> 时序路径和数据到达时间 (arrival times) 做对比,判断时序约束是否满足 (meet)

Reg-to-Reg Path 约束

时序约束时,时钟的下降沿只有在双边沿时钟设计中才会起作用。 所以一般设计的时序约束都与时钟上升沿相关。

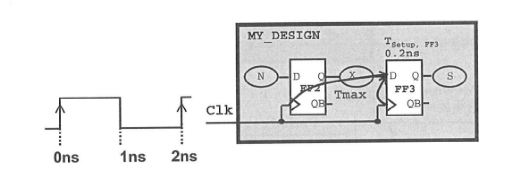

假设一个含有 Reg-to-Reg Path 的设计示意图如下:

此设计中,时钟周期 2ns,setup 为 0.2ns,则 FF2 的 clock 端到 FF3 的 D 端的最大延迟为:

Tmax = 2ns-0.2ns = 1.8ns

那么最简单的时钟约束可以编写为:

create_clock [get_ports Clk] -name sys_clk \\

-period 2 -waveform "0 1"

create_clock : DC Memory 中创建 clock 的命令 ;

[get_ports Clk] : 为创建的 clock 指定对应设计中的源 clock,源 clock 不一定是顶层模块中的 clock ,也可以是子模块中的 clock ;

-name sys_clk : 将创建的 clock 命名为 sys_clk,可以省略 ;

-period 2 : 指定创建的 clock 周期为 2ns ;

-waveform "0 1" : 表示时钟上升沿时刻为 0ns、下降沿时刻为 1ns,以此循环,间接指定了占空比。 此选项也可以省略,则创建的时钟默认占空比为 50% 。

clock 模型

关于时钟的基本概念,欢迎参考《Verilog 教程高级篇》中《5.2 时钟简介》一节。

时钟树综合 (Clock Tree Synthesis, CTS) 一般发生在 DC 之后的布局布线阶段。 DC 阶段不进行时钟树综合,不允许插入缓冲单元 (buffer)。 此时时钟网络认为是理想的,且具有无限驱动能力。

例如上述创建的 clock 模型中,时钟特性如下:

上升沿、下降沿转换时间为 0

时钟偏移为 0

时钟延迟为 0

但是还是建议在 DC 阶段对 clock 进行建模,估算时钟的各种特性,也为布局布线时的时钟树综合留有时间裕量。 时钟特性的建模主要包括:时钟偏移、时钟延迟与时钟转换时间的估算模拟。

时钟偏移建模

时钟偏移模型通过设置时钟的不确定度来描述。 时钟的不确定度参数,也包含了时钟抖动 (jitter)、裕量 (margin) 等参数信息。

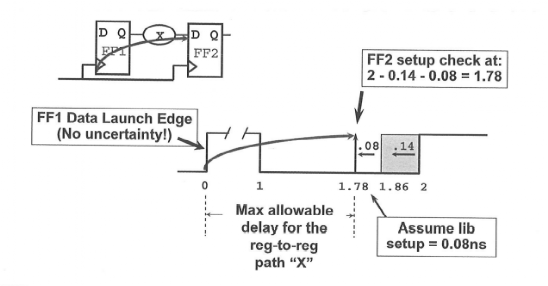

假设某个设计示意图如下,时钟偏移量为 0.14ns,建立时间为 0.08ns,则时钟不确定度的设置描述如下:

create_clock [get_ports Clk] -name sys_clk -period 2

# -setup 0.14 表示时钟偏移设置为 0.14

set_clock_uncertainty -setup 0.14 [get_clocks sys_clk]

FF1 到 FF2 的最大延迟,即 FF2 的建立时间的检查时刻为:

2 - 0.14 - 0.08 = 1.78ns

设置时钟不确定度时,也可以指定不同的时钟域 (clock domain) :

set_clock_uncertainty -setup 0.14 \\

-from [get_clocks clk1] -to [get_clock clk2]

时钟延迟建模

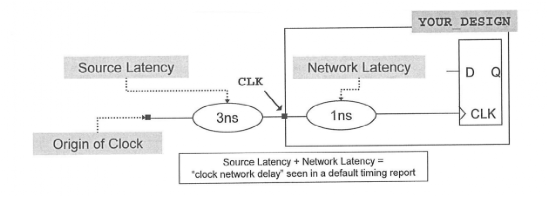

时钟延迟模型分为 2 种:时钟网络延迟 (network latency) 与时钟源延迟 (source latency)。

时钟网路延迟模型定义了从 clock port 或 pin 端 (create_clock 时指定的点) 到寄存器 clock 端的延迟。 时钟源延迟定义了实际时钟原点 (clock origin) 到 clock port 或 pin 端的延迟。 示意图如下:

如上图所示,假设时钟周期为 10ns,source latency 为 3ns,network latency 为 1ns,则时钟延迟的设置描述如下:

create_clock -period 10 [get_ports CLK]

# -source 指设定 source latency,不指定时设置 network latency

set_clock_latency -source -max 3 [get_clocks CLK]

set_clock_latency -max 1 [get_clocks CLK]

set_clock_latency 命令表示设置时钟的 latency 属性,指定 -source 选项时表示设置 source latency,不指定时表示设置 network latency。 -max 表示指定延迟最大值,当然也可以使用 -min 表示指定时钟延迟最小值。

布局布线阶段,时钟树综合之后的具有一定实际延迟的时钟称为 propagated clock。 DC 阶段不进行 CTS,所以需要设置 network latency 。 布局布线阶段的 CTS 之后,时钟树具有实际的 latency,此时设置 network latency 的语句要改成:

# 布局布线时,network latency 需要设置实际的 propagated clock

# set_clock_latency -max 1 [get_clocks CLK]

set_propagated_clock [get_ports CLK]

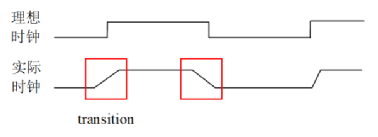

时钟转换时间建模

时钟从上升沿跳变到下降沿,或者从下降沿跳变到上升沿时,并不是"直上直下" 的完成电平跳变,而是 "斜坡式" 需要一个过渡时间完成电平跳变。 这个过渡时间称之为时钟的转换时间 (transition),示意图如下。

假设某一设计中时钟的转换时间最大值为 0.1ns,则 clock transition 的设置语句描述如下:

set_clock_transition -max 0.1 [get_clocks CLK]

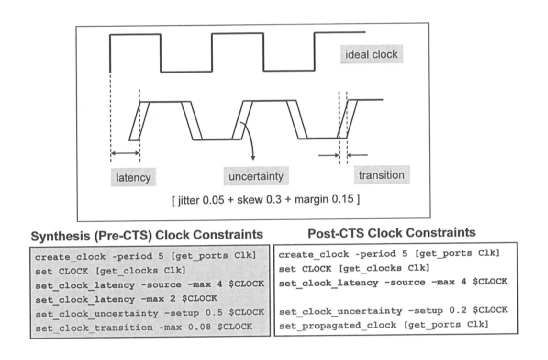

时钟模型小结

下图显示了时钟不确定度、时钟延迟、时钟转换时间的示意图,以及在 DC 和布局布线阶段的设置差异性。

uncertainty、latency 以及 transition 等时钟特性影响的是时序路径的长度。 latency 作用于所有的时序路径,所以时序分析时会产生一种“抵消”的效果,不影响时序分析结果 (下一节介绍)。

工程设计时,往往使用 uncertainty 与 margin (时间裕量) 来进行时钟建模,避免繁琐的设置,也能为布局布线时的 CTS 留有一定的时长调节范围。

例如,带有 margin 和 uncertainty 的时钟模型描述如下:

set UNCERTAINTY 0.3

# 留有 30% 的裕量,作用在时钟周期上

set MARGIN 0.3

set PERIOD 10

create_clock [get_ports CLK] -period [expr $PERIOD*(1-$MARGIN)]

# 时钟模型只设置不确定度参数

set_clock_uncertainty -setup $UNCERTAINTY [get_clocks CLK]

-

一文详解Vivado时序约束2025-03-24 5117

-

FPGA I/O口时序约束讲解2023-08-14 3242

-

浅谈时序设计和时序约束2023-07-04 2689

-

如何在Vivado中添加时序约束2023-06-23 4443

-

FPGA时序约束之衍生时钟约束和时钟分组约束2023-06-12 4500

-

FPGA时序约束的基础知识2023-06-06 2074

-

时序约束的相关知识(二)2023-03-31 3537

-

FPGA的IO口时序约束分析2022-09-27 2536

-

FPGA设计之时序约束2022-03-18 2358

-

VIVADO时序约束及STA基础2022-03-11 11446

-

XDC约束及物理约束的介绍2019-01-07 7407

-

FPGA时序约束方法2015-12-14 1006

-

时序约束用户指南2010-11-02 757

-

时序约束与时序分析 ppt教程2010-05-17 947

全部0条评论

快来发表一下你的评论吧 !