旁路电容0.1uF是怎么来的?

描述

旁路电容在数字电路系统中所起的基本且重要作用,即储能与为高频噪声电流提供低阻抗路径,尽管还并未给旁路电容的这些功能概括一个“高大上”的名字,然而旁路电容所起的终极作用就是为了电源完整性(Power Integrity, PI),它与信号完整性(Signal Integrity, SI)均为高速数字PCB设计中的重要组成部分,后续有机会我们将会进行详细讲解。

事实上,旁路电容的这两个基本功能在某种意义上来讲是完全统一的:你可以认为旁路电容的储能为高频开关切换(充电)提供瞬间电荷,从而避免开关产生的高频噪声向距离芯片更远的方向扩散,因为开关切换需要的能量已经在靠近芯片的旁路电容中获取到了,你也可以认为旁路电容提供了高频噪声电流的低阻抗路径,从而避免了高频开关时需要向更远的电源索取瞬间电荷能量。

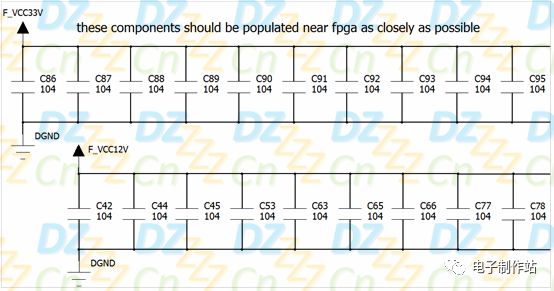

有一定经验的工程师都会发现:旁路电容的容值大多数为0.1uF(100nF),这也是数字电路中最常见的,如下图所示为FPGA芯片的旁路电容:

那这个值是怎么来的呢?这一节我们就来讨论一下这个问题。

前面已经提到过,实际的电容器都有自谐振频率,考虑到这个因素,作为数字电路旁路电容的容量一般不超过 1uF,当然,容量太小也不行,因为储存的电荷无法满足开关切换时瞬间要求的电荷,那旁路电容的容量到底应该至少需要多大呢?我们用最简单的反相器逻辑芯片(74HC04)实例计算一下就知道了。

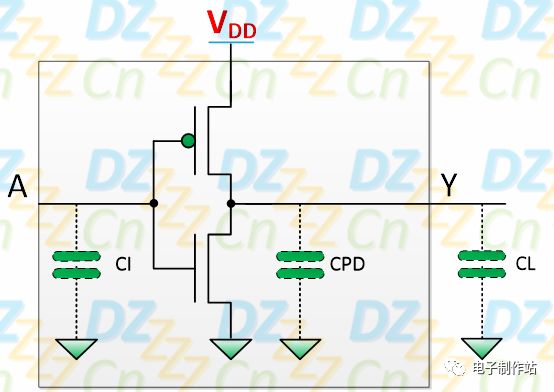

实际芯片的每个逻辑门基本结构如下图所示(以下均来自Philips 74HC04数据手册)

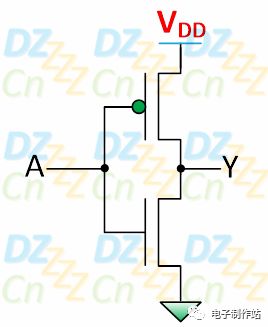

而每个CMOS反相器的基本结构如下图所示(具体参考文章【逻辑门(1)】):

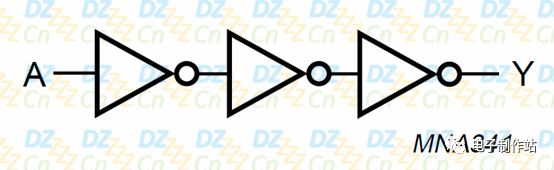

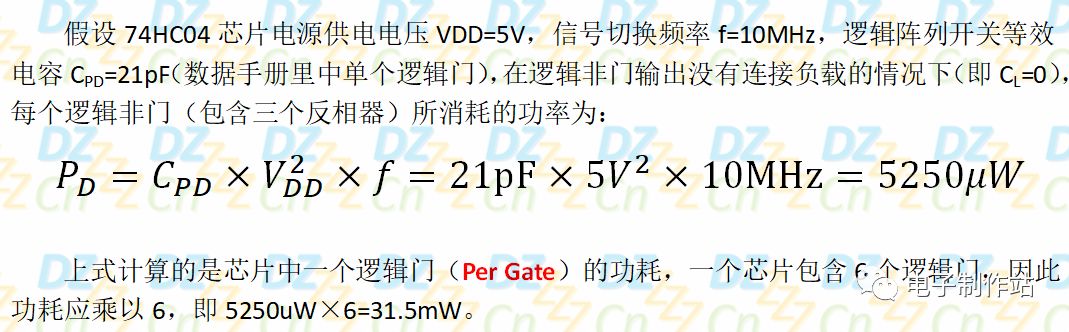

每个逻辑非门(Gate)由三个反相器串联组成,如下图所示(芯片为什么会这样设计可参考文章“逻辑门”):

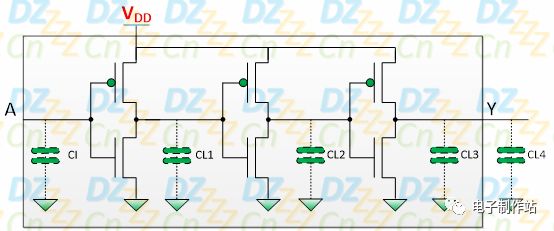

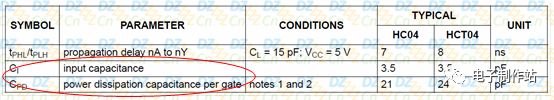

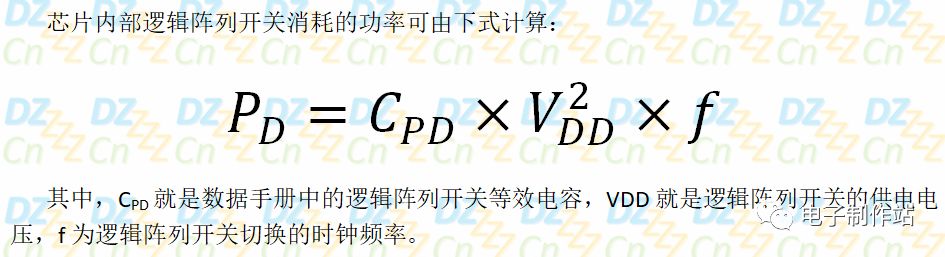

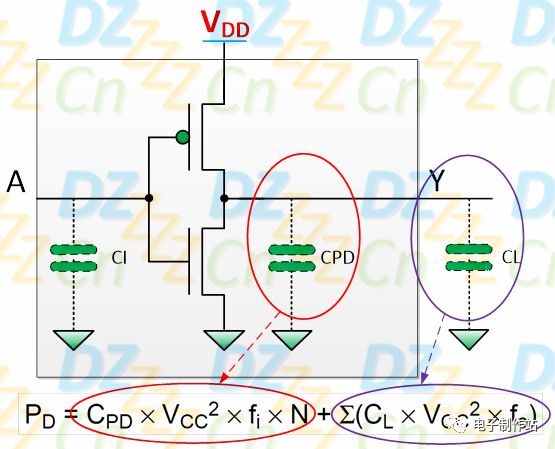

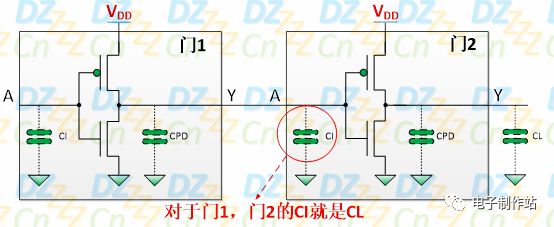

上图中,CI表示芯片信号引脚的输入电容(Input capacitance),CL表示输出负载电容(OutputLoad capacitance)。对于每一级反相器,后一级反相器的输入电容CI即作为前一级开关的输出负载电容,当然,反相器开关本身也会有一定的输出寄生电容,它们也包含在CL内,一个逻辑非门(包含三个反相器)的所有等效负载电容就是内部逻辑阵列开关在切换时需要向电源VDD索取能量的来源(换言之,开关切换时需要对这个等效负载电容进行充放电操作),这个逻辑阵列开关等效电容在数据手册中通常用CPD(power dissipation capacitance per gate)表示,如下图所示 :

注意:在这个数据手册中,CPD是一个逻辑非门(Per Gate)的开关等效电容。

在74HC04芯片中,CPD就相当于是CL1、CL2、CL3的等效电容(不一定是简单的相加),而CL4取决于芯片外接负载,因此,我们也可以将电路等效如下图所示:

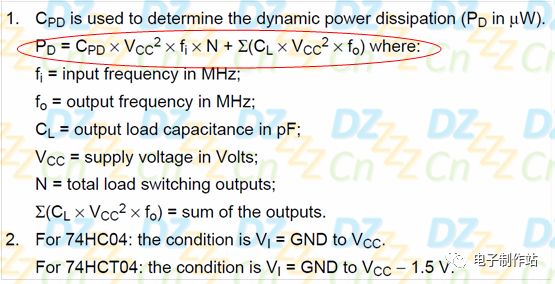

有人问:这个公式怎么来的?权威么?我书读得少,不要骗我!数据手册中有呀,如下图所示:

上图中的公式分成了两个部分,但结构是一模一样的,前面一部分与我们给出的公式是相同的,表示芯片内部逻辑阵列开关等效负载电容CPD的功耗,而后一部分与芯片外接负载CL有关(也称之为等效IO开关电容),输出引脚IO连接有多少个负载,就将相应负载电容CL的功耗全部计算起来,如下图所示:

有人问:输入电容CI就不计算进去吗?乖乖,对于芯片输出引脚连接的负载而言,负载的输入电容CI就是引脚的等效负载电容CL呀,输出负载连接(并联)越多,则等效负载电容CL就越大,消耗的功率也就越大,如下图所示:

一般而言,CL(CI)值是总是相对容易找到的,数据手册中通常都会有,因为输出连接什么负载你肯定是知道的,但CPD却不一定在数据手册能查得到,因此,我们在计算芯片的功耗时可能会分为芯片内与芯片外两个部分。

最基础的数据计算方法我们已经知道了,有两种方法可以估算旁路电容的最小容量:

第一种计算方法思路:逻辑阵列开关等效电容(CPD)需要获取足够的电荷能量,那芯片的旁路电容的容量必定不能比芯片总CPD更小,通常旁路电容的容量比芯片总CPD大25~100倍,我们称其为旁路电容倍乘系数(bypass capacitor multiplier,这里取个中间数50),由于74HC04包含六个逻辑非门,从数据手册上也可以查到CPD约为21pF,因此,芯片总CPD应为21pF×6=126pF,再考虑到50倍的旁路电容系数,旁路电容的容量必须要大于126pF×50=6.3nF。

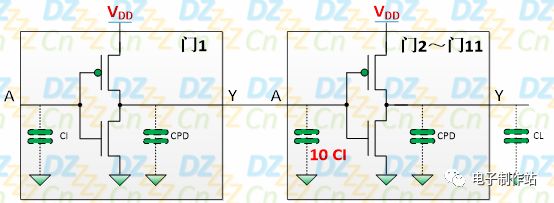

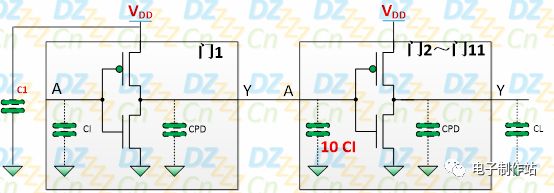

以上计算的是芯片输出未连接负载的情况,假设反相器后面并接了10个逻辑非门(CMOS门电路的扇出系数一般为20~25),则此时等效电路如下图所示:

对于门1 来说,此时芯片的输出负载电容CL=10×CI=10×7pF=70pF,对于整个系统而言,这个CL也可以算是门1的逻辑阵列开关等效电容,因为从图上可以看出,它消耗的是门1的电源能量(而不是门2~门11),这样根据上述同样的算法,门1外接旁路电容的容量至少应为(21pF+70pF)×50=4.55nF,当然,这只是一个逻辑非门的计算结果,如果芯片中其它5个非门也是同样的负载连接,则需要的旁路电容容量至少应为4.55nF×6=27.3nF,在考虑到电路设计裕量情况下,我们可以直接选择100nF的旁路电容。

那功耗PD计算的意义在哪里?前面我们是走了狗屎运,芯片够简单,所以数据手册里提供了CPD的具体值,但更多的应用场合下是没有办法直接获取这个值的,我们看看更大规模集成芯片的情况。

大规模逻辑芯片的旁路电容容量的计算原理也是大体一致的,逻辑阵列开关每秒钟转换的次数至少会以百方来计算(MHz),我们以ALTERA公司FPGA CYCLONE IV芯片来计算一下外接负载时负载电容(不包括内部逻辑开关阵列等效电容CPD,为什么?下面会提到)所消耗的功率。

假设IO供电电源电压VCCIO为3.3V,时钟频率为100MHz,负载数量为30个(也就是输出外接了负载的IO引脚),输出引脚的平均负载电容为10pF,则旁路电容的容量至少应为:10pF×30×50=15000pF=15nF。

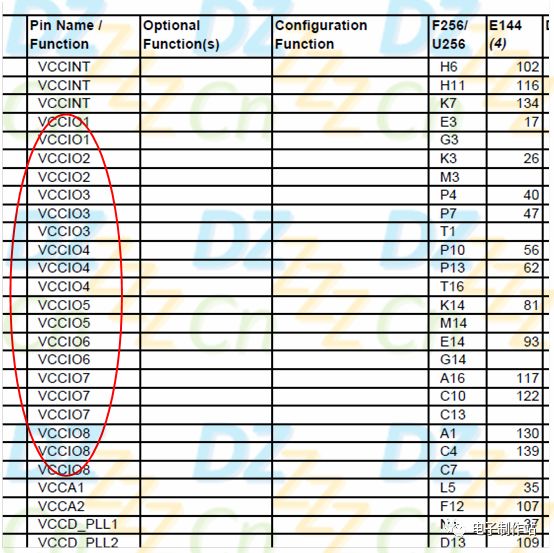

对于FPGA之类的大规模集成芯片,内核电压VCCINT或IO电压VCCIO都会有多个,如果计算某一个电源引脚所需的旁路电容的容量,还需要除以这些电源引脚的个数,如下图所示:

不同封装芯片的VCCIO数量是不一样的,F256/U256(BGA)封装有20个,而E144(QFP)封装只有12个,但是FPGA的VCCIO是按BANK来供电的(就是VCCIO后面带的那个数字,数字相同表示BANK相同,不了解FPGA的读者不必深究),不应该直接除了这个总数,如果这30个连接的负载分布在2个BANK,对于E144封装每个BANK约有2个VCCIO电源,仅需要除以数量4就行了,因此,单个电源引脚所需要的旁路电容容量应至少约为3.75nF。

我们可以用灭火的水龙头来理解:当芯片只有一个电源引脚时,相当于灭火的水龙头只有一个,而芯片有多个电源引脚时,相当于灭火的水龙头有多个,在火灾危害程度相同的情况下,需要灭火的用水量是一定的,因此,对于有多个水龙头的情形而言,单个水龙头需要的用水量需求就少了,当然,总的用水量肯定是一样的,亦即总的旁路电容值是不会变化的。

上面只是计算芯片外接负载时需要的旁路电容容量,那如何计算内部逻辑阵列等效电容呢?没办法直接去计算,除非知道具体的CPD的值(前面我们是走运),但是这个值通常是不提供的,因为这个值会随实际电路逻辑规模的大小与功能而有很大的不同,那就没有办法了吗?NO!

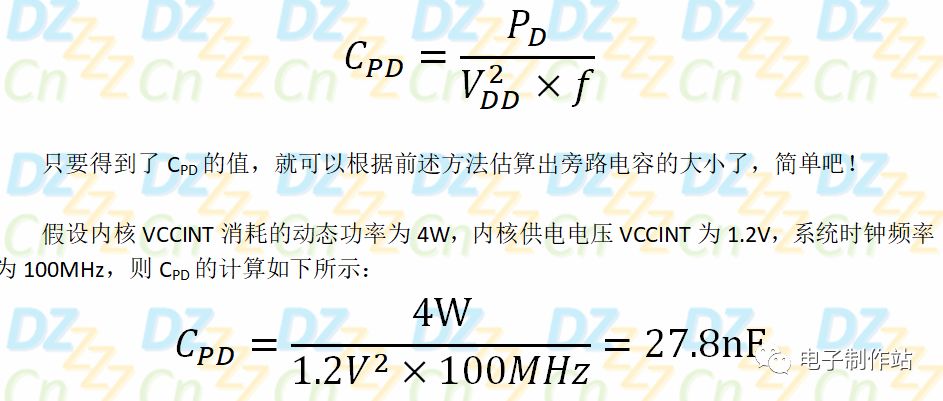

我们可以用测量仪器实际测量出FPGA芯片在具体逻辑功能应用时所消耗的动态功率PD,或使用配套的功耗分析软件进行功耗的计算,总而言之,芯片逻辑阵开关等效电容的功耗PD的值总是可以获取出来的,再根据之前的功耗计算公式反推出CPD,如下所示:

27.8nF已经不小了,再乘上50倍旁路电容的倍数,则旁路电容的总容量至少应为27.8nF×50=1390nF=1.39uF,因此,动态功耗越大的芯片需要在旁边放置更多的旁路电容就是这个道理。

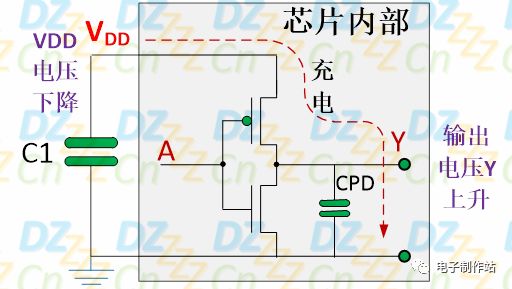

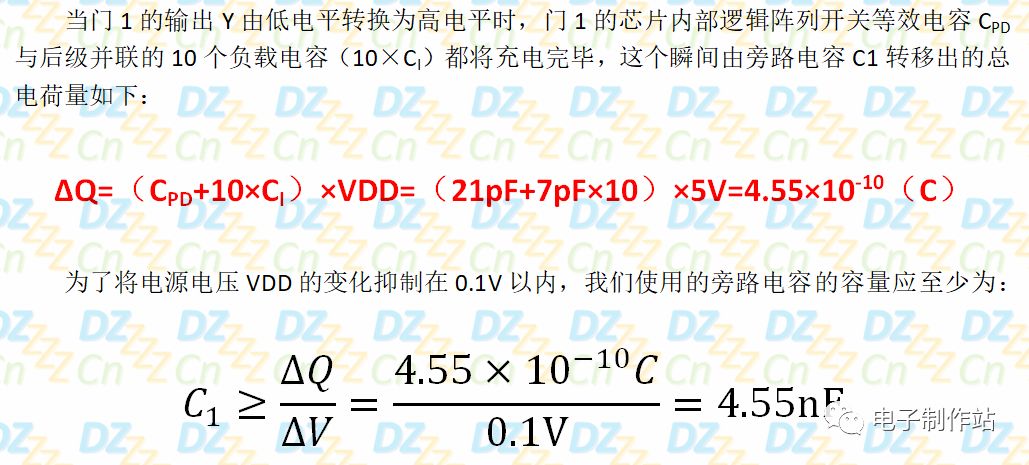

另外一个计算方法是:假定旁路电容的电荷量能将VDD变化量维持在某一特定范围内(比如VDD仅变化0.1V),我们根据逻辑阵列开关等效电容CPD的电荷消耗需求来估算旁路电容的容值,如下图所示:

当PMOS管(上侧带圈圈)开关打开时,VDD电源对芯片逻辑阵列开关等效电容CPD充电,CPD电容两端的电压会上升,旁路电容C1两端的电压(VDD)将会下降,因为旁路电容C1的部分电荷已经转移到了CPD中,为了维持电压VDD变化不超过0.1V,我们可以根据需要转移的电荷量与VDD电压的允许变化量求出旁路电容的最小容量。

我们还是以一个逻辑非门驱动10个逻辑非门的情况来计算CPD的大小,如下图所示:

如果芯片中的其它5个逻辑非门也是同样的负载连接,则旁路电容的最小容量至少应为4.55nF×6=27.3nF,这个计算结果与前一种方法相差无几。在考虑设计裕量的情况下,我们也会使用100nF(0.1uF)的旁路电容。

事实上,以上两者估算的本质是完全相同的,我们同样可以用水龙头的比喻来理解旁路电容容量的计算原理,但同一道菜上得太多就没意思了,我们换另做一道菜来吃:

假设芯片逻辑开关总等效电容CPD(不仅包括芯片本身的CPD,也包括负载总电容CL)相当于一个取水的杯子,而旁路电容C1相当于储藏水源的地方,我们认为储水之地的水位相当于电源电压VDD,如果储水之地是一只盛满水的小碗,那么CPD这只杯子从小碗中取一杯水(也就是CPD充满电的总电荷)后,小碗中的水位就会下降(相当于电源VDD下降),因为两者储水的空间相差并不大,而如果储水之地是一大缸水,则从中取同样CPD一杯水对这缸水的水位影响非常小,因此,如果你想要这个水位(VDD)变化越小,则储水之地(旁路电容的容量)就必须比CPD要大得多。

审核编辑:刘清

-

jf_25316624

2023-04-03

0 回复 举报还得慢慢消化 收起回复

jf_25316624

2023-04-03

0 回复 举报还得慢慢消化 收起回复

-

0.1uF小电容滤波原理详解2023-11-03 5711

-

芯片附近0.1uF电容的作用2025-06-17 561

-

max232能用0.1uf电容吗2015-04-17 10026

-

芯片附近为什么要放置0.1uF电容2019-05-24 4864

-

电路中0.1UF和10UF电容有什么用?2021-03-11 4928

-

为什么旁路电容紧盯着IC不放?为什么旁路电容总是0.1uF?2023-04-03 1866

-

电路中0.1UF和10UF电容有什么用?怎么用?资料下载2021-03-28 8299

-

揭秘0.1uF容量的旁路电容的由来2021-06-29 7220

-

芯片电源脚放0.1uF的电容的作用2023-02-16 4407

-

芯片IC0.1uF的电容,这些参数是如何确定2023-06-05 2714

-

芯片附近为何要放置0.1uF电容?2023-10-13 2930

-

电源端加旁路电容的作用 电源旁路电容为何选择0.1uF 10uF?2023-10-20 3980

-

Y电容容量为什么基本不大于0.1uF?2023-12-04 1427

-

资深详解:旁路电容0.1uF是这样来的2024-01-14 3465

-

为什么要在每个芯片电源管脚加0.1uF的电容呢?2024-02-28 7402

全部0条评论

快来发表一下你的评论吧 !