几个氮化镓GaN驱动器PCB设计必须掌握的要点

电子说

描述

几个氮化镓GaN驱动器PCB设计必须掌握的要点

NCP51820 是一款 650 V、高速、半桥驱动器,能够以高达 200 V/ns 的 dV/dt 速率驱动氮化镓(以下简称“GaN”)功率开关。之前我们简单介绍过氮化镓GaN驱动器的PCB设计策略概要,本文将为大家重点说明利用 NCP51820 设计高性能 GaN 半桥栅极驱动电路必须考虑的 PCB 设计注意事项。

本设计文档其余部分引用的布线示例将使用含有源极开尔文连接引脚的 GaNFET 封装。

VDD 电容

VDD 引脚应有两个尽可能靠近 VDD 引脚放置的陶瓷电容。如图 7 所示,较低值的高频旁路电容(通常为 0.1 μF)应与第二个并联电容(1 μF)一起放在最靠近 VDD 引脚的位置。

图1. NCP51820 VDD 电容布局和布线

所有走线须尽可能短而直。可以使用过孔,因为 VDD 电流相对较低。SGND 返回平面对于其屏蔽特性以及让所有信号侧接地回路保持相同电位很有好处,建议使用。SGND 平面位于第 2 层,使其靠近信号侧元器件和 NCP51820。所有信号侧元器件都放在 SGND 平面上,并通过过孔连接。VDD 引脚和 VDD 电容之间应建立直接连接,最好使用过孔作为 SGND 平面的返回连接。

如图1所示,两个 VDD 电容的接地连接并在一起,并通过单个过孔连接到 SGND 平面。如果可能,最好使用不间断的实心 SGND 接地平面,以免形成接地环路。建议将“安静”的 SGND 平面延伸到 NCP51820 下方,以帮助屏蔽驱动器 IC,使其不受噪声影响。注意在图1中,SGND 平面没有延伸到 NCP51820 栅极驱动器输出引脚下方。这是有意为之,目的是避免噪声从栅极驱动 di/dt 峰值拉电流和灌电流耦合到 SGND 平面中。

VBST 电容和二极管、VDDH 和 VDDL 旁路电容

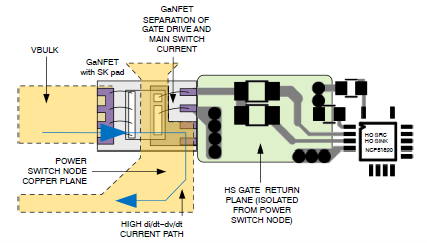

VBST 电容应尽可能靠近 VBST 引脚放置。VBST 电容返回引脚应连接到 GaNFET 的驱动器 SW 引脚、VDDH 返回引脚和源极开尔文引脚。每个连接都是通过过孔接到 HS 栅极返回平面,如图2所示。务必注意,不应从功率级开关节点接回到 NCP51820。请勿将 VBST 电容连接到功率级开关节点。“开关节点”的唯一连接是通过 HS GaNFET 源极开尔文引脚。

HS 栅极返回平面的设计应注意,不得与功率级开关节点发生重叠或相互作用。同样,LS 栅极返回平面的设计应注意,不得与 LS GaNFET 电源地发生重叠或相互作用。请勿将 SGND 平面放在 VBST 二极管或 VBST 电容下方,因为 VBST 二极管的阴极上存在高 dV/dt,它可能会将噪声注入 SGND 平面。

图2. NCP51820 VBST 电容和二极管、VDDH 和 VDDL 电容

VDDH 电容应尽可能靠近 VDDH 引脚放置。如图2所示,VDDH 电容返回引脚应通过过孔连接到 HS 栅极返回平面(与 VBST 电容共用一个双过孔连接)。

VDDL 电容应尽可能靠近 VDDL 引脚放置。如图2所示,VDDL 电容返回引脚应通过过孔连接到 LS 栅极返回平面。VDDL 电容返回引脚必须连接到驱动器上的 PGND 引脚。VDDL 电容返回引脚通过过孔连接到 LS 栅极返回平面,该平面也通过过孔连接到驱动器 PGND 引脚。

由于栅极驱动电流峰值很高,并且为了降低过孔寄生电感,VBST、VDDH 和 VDDL 需要多个过孔。在此示例中,每个 GaNFET 栅极返回连接使用四个过孔。这是一个合理的折衷考虑,一方面能在 NCP51820 栅极驱动器返回引脚与 GaNFET 返回引脚之间获得低阻抗连接,另一方面能保持实心返回平面和良好的屏蔽完整性。如果可能,最好使用导电材料填充的过孔,因为其相关电感更低。

栅极驱动布线

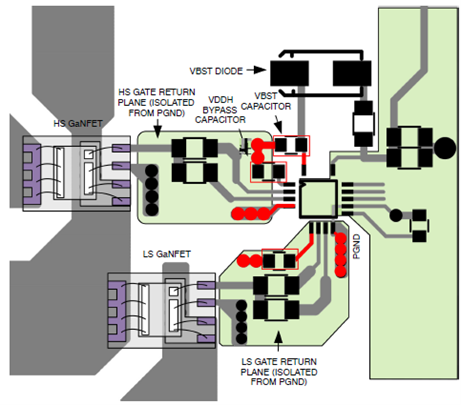

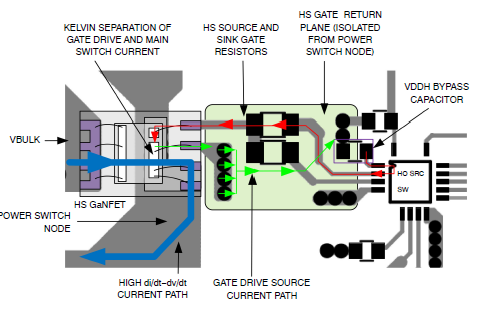

当 NCP51820 向 HS GaNFET 栅极提供电流时,该栅极电流来自 VDDH 调节器旁路电容中储存的电荷。如图3所示,拉电流流经 HO 驱动器源极阻抗和栅源电阻,进入 GaNFET 栅极。然后,电流从 GaNFET 源极开尔文引脚返回,又回到 VDDH 旁路电容。

图3. 高压侧栅极驱动拉电流

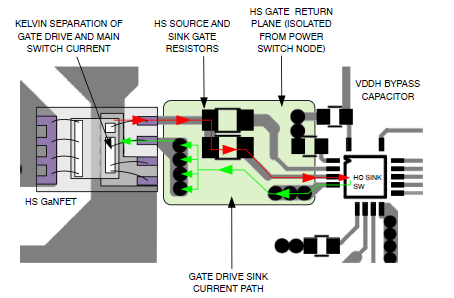

当 NCP51820 从 HS GaNFET 吸收电流时,该电流来自栅源电容中储存的能量。如图4所示,灌电流从 HS GaNFET 栅极流出,经过栅极灌电流电阻、HO SINK 驱动器阻抗和 SW 引脚,回到 GaNFET 源极开尔文引脚。

图4. 高压侧栅极驱动灌电流

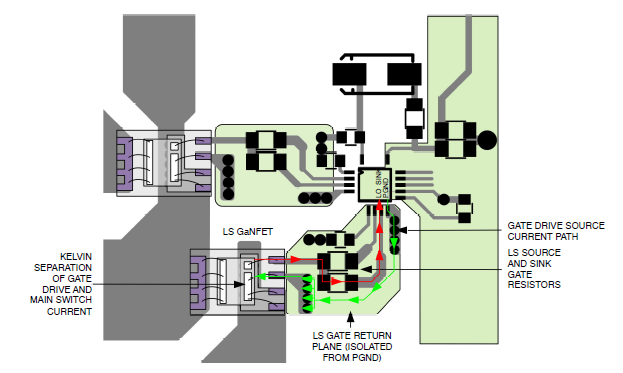

当 NCP51820 向 LS GaNFET 栅极提供电流时,该栅极电流来自 VDDL 调节器旁路电容中储存的电荷

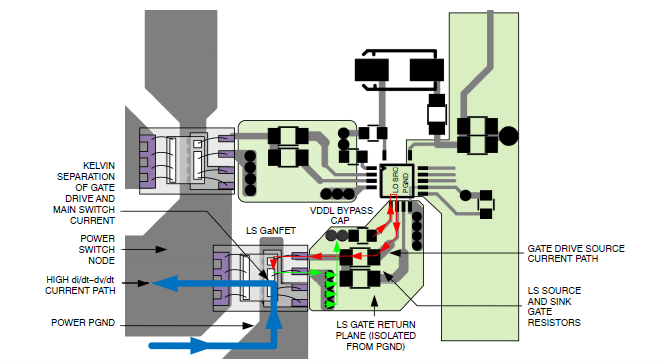

图5. 低压侧栅极驱动拉电流

当 NCP51820 从 LS GaNFET 吸收电流时,该电流来自栅源电容中储存的能量。如图6所示,灌电流从 LS GaNFET 栅极流出,经过栅极灌电流电阻、LO SINK 驱动器阻抗和 PGND 引脚,回到 GaNFET 源极开尔文引脚。

图6. 低压侧栅极驱动灌电流

GaNFET 能以高开关频率工作,漏源切换期间会出现高 dV/dt(100 V/ns 及更高)。GaN 的栅源导通阈值较低 (<2 V),因此栅极驱动拉电流和灌电流路径必须尽可能保持短而直,以减轻走线寄生电感的不良影响。栅极环路中的过大寄生电感可能导致超过栅源阈值电压的栅极振荡或高频振铃。栅极驱动和返回路径中的过孔只有在绝对必要时才应使用。最好使用导电材料填充的过孔,因为每个这种过孔的电感要小得多。在栅极电阻和相关布线下方使用载流返回平面,以在拉电流和灌电流路径正下方提供一个返回路径,有助于减少环路电感。

NCP51820 高压侧和低压侧驱动在内部相互隔离。对于高压端,SW 引脚必须与功率开关节点隔离,以防止开关噪声注入栅极驱动路径,并且它只能连接到高压侧 GaNFET 上的 SK 引脚。源极开尔文引脚和电源引脚之间的开尔文连接是 NCP51820 SW 引脚和功率级开关节点之间的唯一电气连接,如图3和图4所示。同样,低压侧栅极驱动的布线应使 NCP51820 PGND 引脚与功率级 PGND 隔离,并且只能连接到低压侧 GaNFET 的 SK。设计目标是避免电源 PGND 噪声注入低压侧栅极驱动路径。在低压侧 GaNFET 内部,SK 引脚和电源引脚之间存在开尔文连接,它是 NCP51820 PGND 和电源 PGND 之间的实际连接,如图5和图6所示。

在设计允许的范围内,HS 和 LS 栅极走线的长度应尽可能相等。这有助于确保两个 GaNFET 具有相似的栅极驱动阻抗。高压侧和低压侧 GaNFET 交错对齐具有双重作用:一是使得栅极驱动布线接近对称且等距,二是允许使用更大、更高电流的功率开关节点铜触点。

最好将 HS 和 LS 返回平面分配至第 2 层,并将它们直接放置在栅极驱动电阻和走线下方,这样有助于减少栅极驱动环路电感。对于高压侧 GaNFET,由于 VDDH 旁路电容返回引脚和 NCP51820 SW 引脚被 HO 拉电流和 HO 灌电流走线分开,因此可以使用无填充的过孔通过 HS 栅极返回平面连接到 GaNFET 的源极开尔文引脚。建议使用多个过孔以帮助减少过孔电感。请注意,栅极驱动电流路径与功率开关节点电流路径隔离,尽可能避免主电流路径中的噪声注入栅极驱动电流路径。

对于低压侧 GaNFET,由于 VDDL 旁路电容返回引脚和 NCP51820 PGND 引脚被 LO 拉电流和 LO 灌电流走线分开,因此可以使用无填充的过孔通过 LS 栅极返回平面连接到 GaNFET 的源极开尔文引脚。建议使用多个过孔以帮助减少过孔寄生电感。请注意,栅极驱动电流路径与电源 PGND 电流路径隔离,尽可能避免主电流路径中的噪声注入栅极驱动电流路径。

信号接地 (SGND) 和电源接地 (PGND)

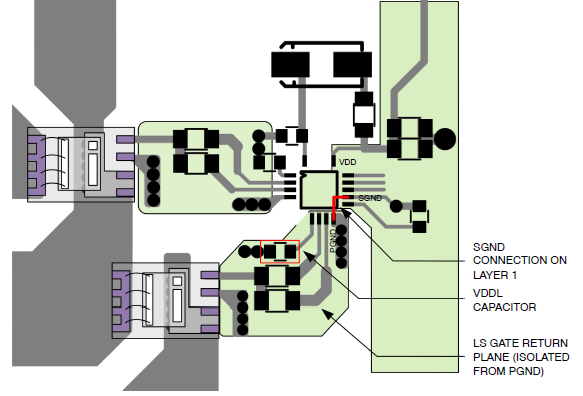

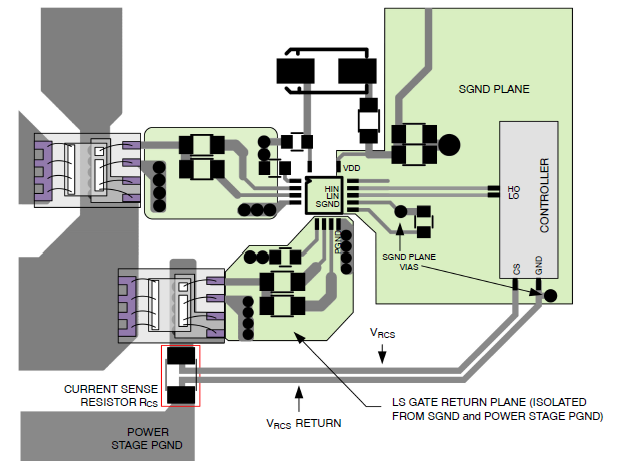

SGND 是所有内部控制逻辑和数字输入接地。在内部,SGND 和 PGND 引脚相互隔离。PGND 用作低压侧栅极驱动和返回基准。

对于半桥电源拓扑或任何使用电流检测变压器的应用,NCP51820 SGND 和 PGND 应在 PCB 上连接在一起。在此类应用中,建议在 PCB 上通过一条低阻抗短走线将 SGND 和 PGND 引脚连接在一起,并且让它们尽可能靠近 NCP51820。NCP51820 正下方是建立 SGND 至 PGND 连接的理想位置,如图7所示。

图7. PGND 至 SGND,0 Ω 单点连接

对于低功耗应用,例如有源箝位反激式或正激式转换器,通常会在低压侧 GaN FET 源极支路中使用一个电流检测电阻 RCS。在此类应用中,NCP51820 PGND 和 SGND 引脚不得在 PCB 上连接,因为 RCS 会通过此连接短路。NCP51820 低压侧驱动电路能够承受 -3.5 V 至 +3.5 V 的共模电压。大多数电流检测电压信号小于 1 V,因此低压侧驱动级很容易“浮动”到电流检测所产生的电压 VRCS 以上。如图8所示,整个低压侧栅极驱动浮动到 VRCS 以上。这一点很重要,因为它确保栅极驱动幅度不会有损失,因此完整的 VDDL 电压会出现在低压侧 GaN FET 栅源端子。

按照上文所述布置电路时,连接到 NCP51820 HIN 和 LIN 的控制器 HO/LO 路径必须返回到控制器 GND 以形成完整电路。因此,NCP51820 SGND 和控制器 GND 必须相连。这是通过使用过孔将 NCP51820 SGND 和控制器 GND 连接到 SGND 平面来实现的,如图 14 所示。SGND 平面仅用于信号和信号侧 VDD 返回,也会充当信号的屏蔽层。VRCS 返回引脚还必须连接到控制器 GND,这应该使用单条低阻抗走线来完成,该走线应尽可能靠近 VRCS 走线(或位于其下方)。这会将功率级 PGND 单点连接到 SGND,并将功率级 PGND 上的高 dV/dt 和 di/dt 与 SGND 平面隔离开来。

图8. LS 栅极返回隔离和 VRCS 连接

开关性能验证

在利用 NCP51820 驱动 GaNFET 的半桥功率级布局中使用了本文介绍的 PCB 设计技术。

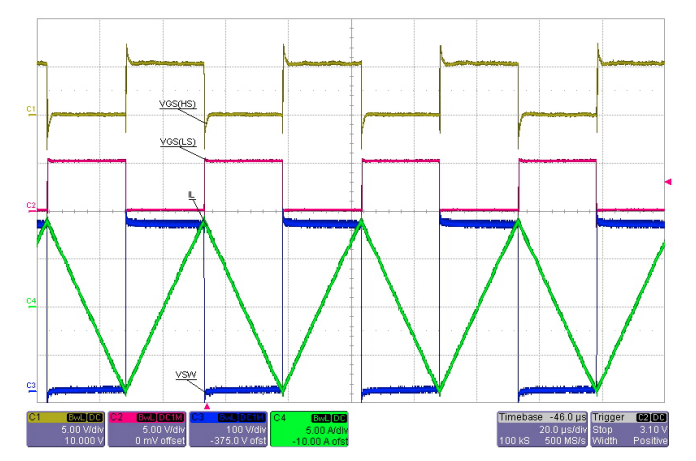

图9. 650 V,18 A,HEMT,GaNFET,350 V,10 APK

图9显示了驱动两个 650 V、18 A、90 mΩ GaNFET 的稳态波形。通道 1(黄色)是高压侧栅源电压,通道 2(红色)是低压侧栅源电压,通道 3(蓝色)是开关节点电压(低压侧 GaN VDS),通道 4(绿色)是电感电流。高压侧栅源电压(通道 1,黄色)显示存在轻微过冲和欠冲,这是使用高压探针测量低压浮动信号(在栅极和功率开关节点之间测量)的附带结果。通道 2(红色)显示了栅源电压的“更真实”测量结果,其中低压侧 GaNFET 栅源电压在栅极和 PGND 之间测得。可以看到,栅极驱动边沿非常锐利且干净。同样,开关节点电压(通道 3,蓝色)没有振铃、过冲或欠冲。

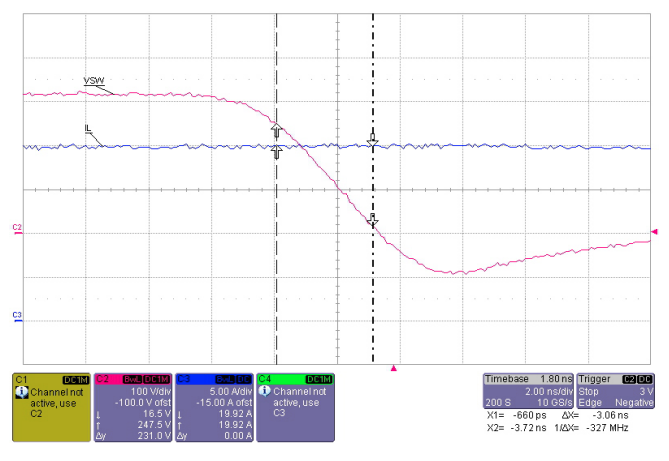

图10. 600 V,26 A,HEMT,GIT,GaNFET,dV/dt = 75 V/ns,320 V,20 APK

图10所示波形是驱动两个 HEMT、GIT、600 V、26 A、56 mΩ GaNFET 的结果,其电流能力比图9中使用的器件要高。要实现高 dV/dt,需要相当大的漏极电流 ID。例如,所示测量是在 ID = 20 APK 下进行的,导致实测 VDS dV/dt = 75 V/ns。三角形峰值电感电流显示为纯直流,这是进行此测量所需的时基 (2 ns/div) 造成的。VSW 波形的 100 V 欠冲是用于显示高 dV/dt 的测量技术的结果,在开关节点上并不真正存在。

在高电压、高频率 PCB 设计中,为了成功运用宽禁带半导体,需要更好地了解寄生电感和电容的负面影响。透彻理解电气返回平面、屏蔽、电流分离、隔离和精心布线的重要性,对于充分发挥 GaN 技术的性能优势至关重要。本文重点说明在利用 NCP51820 驱动高速电源拓扑中使用的 GaN 功率开关设计中,实现成功设计必须采用的重要 PCB 设计准则。这些技术已通过实测波形得到了验证,表明其能够获得出色的结果。

审核编辑:汤梓红

-

氮化镓(GaN)的最新技术进展2024-07-06 2298

-

干货 | 氮化镓GaN驱动器的PCB设计策略概要2023-09-27 2536

-

为什么氮化镓(GaN)很重要?2023-06-15 1698

-

氮化镓GaN驱动器PCB设计必须掌握的要点2023-05-17 1922

-

几个氮化镓GaN驱动器PCB设计必须掌握的要点2023-02-27 1385

-

划重点 | 几个氮化镓GaN驱动器PCB设计必须掌握的要点2023-02-22 2196

-

氮化镓GaN驱动器的PCB设计策略概要2023-02-20 1311

-

如何用集成驱动器优化氮化镓性能2022-11-16 990

-

用集成驱动器优化氮化镓性能2022-11-02 1024

-

传统的硅组件、碳化硅(Sic)和氮化镓(GaN)2021-09-23 6154

-

请问氮化镓GaN是什么?2021-06-16 2857

-

什么是氮化镓(GaN)?2019-07-31 8032

-

氮化镓GaN技术助力电源管理革新2018-11-20 2104

全部0条评论

快来发表一下你的评论吧 !