基于Arm Cortex-M0处理器的智能娱乐收音机系统设计

音视频及家电

描述

由工业和信息化部人才交流中心主办的2022年第六届全国大学生集成电路创新创业大赛(以下简称:集创赛)已落下帷幕,来自武汉理工大学的“夜的第七章”团队做的智能娱乐收音机项目,在2022年集创赛安谋科技杯获得了一等奖。此项目基于Arm Cortex-M0处理器在安路EG4S20上利用FM_SDR板卡构建具备无线通信基带信号处理的片上系统。

1 项目简介

本项目基于Arm Cortex-M0处理器在安路EG4S20上利用FM_SDR板卡构建具备无线通信基带信号处理的片上系统,下载程序后,可在Keil界面中完成调试及运行。

作品使用内部总线连接存储器与FPGA板载的外设,如数码管、矩阵键盘、拨动开关、LED、蜂鸣器、FLASH等,配合控制外围扩展电路实现FM等通信信号的调制解调等处理。在此基础上,设计FIR带通滤波器并为FM射频板配备了性能更加优良的射频天线与大音腔喇叭,使音质得到了提升;采用芯片CI1122完成对特定语句的离线识别功能简化了调台的操作步骤;利用芯片内合封的SDRAM和SD卡模块实现对音乐的播放、录制和评分功能;用板载QN8027发射芯片增加FM游戏、机械臂控制等通信功能,同时作为专用的FM发射芯片,QN8027支持立体声传输,但MSi001仅支持FM基带解调,采用立体声数字解调的方案,实现了对立体声副载波的解调(AM解调),完成了立体声传输,展示效果良好,实践创新性强。

2 系统设计

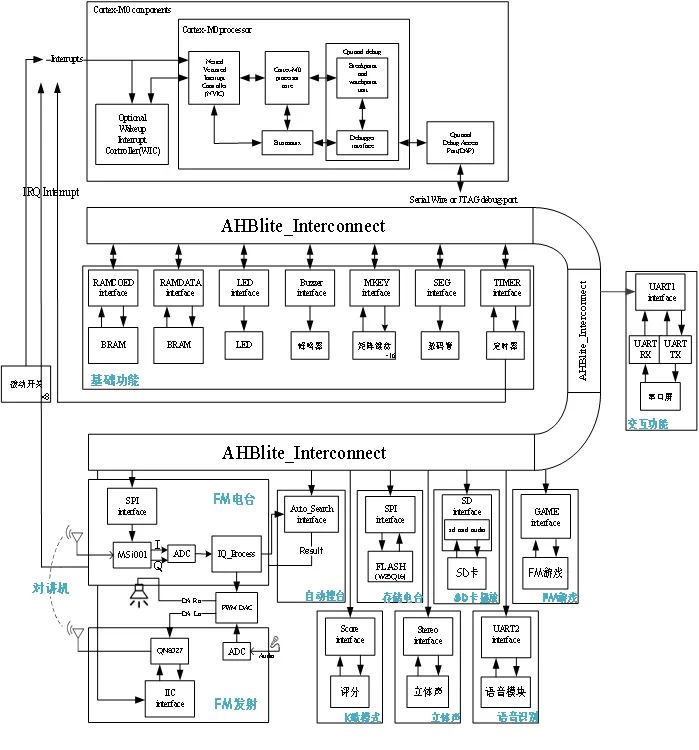

本系统的主要功能部件包括ARM Cortex-M0内核、AHB总线矩阵、CMSIS-DAP调试端口、语音识别模块、SD卡模块等,具体系统框图如下图所示。在方案设计时,核心思想为软硬件协同,充分利用开发板资源完成整个系统的搭建,结构如图所示。

图2. 整体系统设计

3 硬件搭建

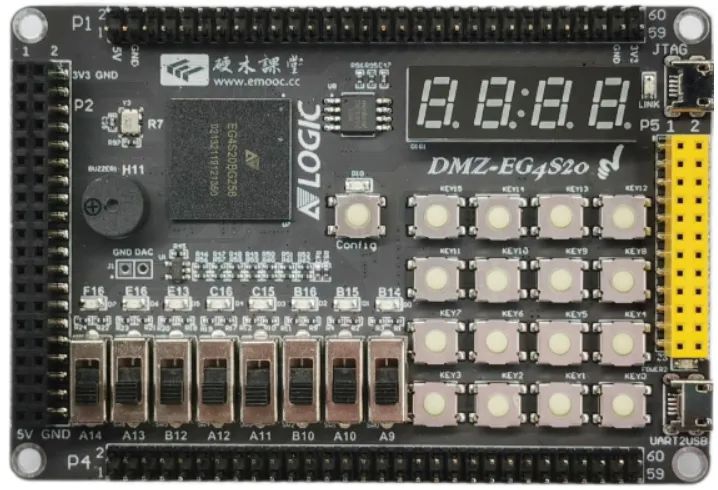

3.1 FPGA开发板

我们将开发板的核心芯片型号选定为安路科技的EG4S20BG256,它具有低功耗、低成本、高性能等特点。有丰富的LUT、DSP、BRAM、高速差分IO等资源,强大的引脚兼容替换性能。有256个管脚(其中可用IO共193个);在外围功能模块的设计上,则以简洁直观、小巧易携带为目标,主要包括以下几类模块:板载USB-JTAG电路,实现一根线供电和调试;输出显示类,如LED灯、数码管;输入操作类的,如矩阵按键、拨动开关;发声及音频类的,如蜂鸣器;对外通信接口类的,如UART转USB接口;存储器类的,如FLASH存储器、SDRAM存储器;模数混合类的,如ADC和DAC。

同时安路科技提供丰富的设计工具(例如TD)帮助用户有效地利用 EAGLE 平台实现复杂设计。业界领先的综合和布局布线工具,为用户设计高质量产品提供有力保障。本设计选定芯片型号为EG4S20BG256,是基于安路成熟可靠的低成本、低功耗可编程 FPGA—EG4S20,采用最新的3D 合封技术,与一块 2M X 32bits 的 SDRAM合封而成。开发板实物如图所示。

图3. FPGA开发板实物图

EG4S20BG256的特色优势包括: 灵活的逻辑结构

19600个 LUTs,用户IO数量193个

低功耗器件

先进的55nm低功耗工艺

静态功耗低至5mA

支持分布式和嵌入式存储器

156 Kbits分布存储器(Distribute RAM)

1 Mbits嵌入块存储器(Block RAM简称BRAM)包括:64个9 Kbits BRAM,可配置为真双口,8Kx1到512x18模式16个32 Kbits BRAM,可配置为真双口,可设置为2K16或4K8专用FIFO控制逻辑

内置大容量存储器

内置2M* 32bits SDR SDRAM,最高工作时钟200MHz

可配置逻辑模块(PLBs)

优化的的LUT4/LUT5组合设计双端口分布式存储器支持算数逻辑运算快速进位链逻辑

源同步输入/输出接口

输入/输出单元包含DDR寄存器

Generic DDRx1

Generic DDRx2

高性能,灵活的输入/输出缓冲器

支持LVTTL、LVCMOS (3.3/2.5/1.8V/1.5/1.2V)、PCI

支持LVDS,Bus-LVDS, MLVDS, RSDS, LVPECL

支持热插拔

可配置上拉/下拉模式

片内100欧姆差分电阻

时钟资源

针对高速I/O接口设计的2路IOCLK

16路全局时钟

支持4个PLLs用于频率综合

5路时钟输出

分频系数1到128

支持5路时钟输出级联

动态相位选择

配置模式

主模式串行SPI (MSPI)

从模式串行 (SS)

主模式并行x8 (MP)

从模式并行x8 (SP)

JTAG模式 (IEEE-1532)

每个芯片拥有唯一的64位DNA

嵌入式硬核IP

8通道12位1MSPS SAR ADC

集成电压监控模块

内置环形振荡器

3.2 射频开发板

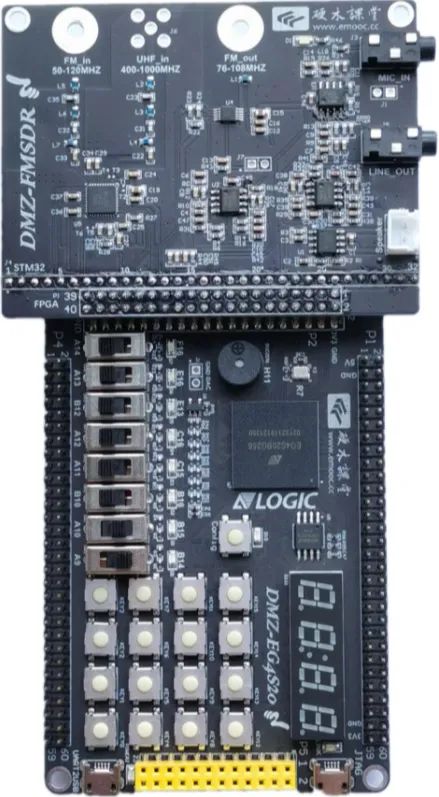

选用了DMZ_FMSDR开发板。DMZ_FMSDR内部包含了50M-120M,400M-1000M射频接收电路,76M-108M的FM频道发射电路,麦克风电路,音频耳放和功放电路。可以通过编程实现FM收音机、FM发射机、FM对讲机以及其他频段的接收机。FM_SDR模块与EG4S20模块对插示意图如图所示。

图4. FM_SDR模块与EG4S20模块对插示意图

4 功能设计

FM电台:基带信号处理1)IQ信号接收2)解调算法3)符号转换,PWM_DAC模块, 自动搜台原理,存储与切换频道,音质提升;K歌模式;语音识别;FM通信:FM游戏,FM机械臂;立体声传输。

5 作品外观

图5. 实物图

团队介绍

参赛单位:武汉理工大学

队伍名称:夜的第七章

指导老师:付琴,杨媛媛

参赛队员:王鑫鹏,卢思远,黄俊颖

总决赛奖项:一等奖

编辑:黄飞

-

Cortex-M0 处理器介绍2026-01-16 205

-

ARM Cortex-M0设计启动评估用户指南2023-08-18 666

-

基于ARM Cortex-M0的智能娱乐收音机设计方案分享2022-09-13 3473

-

制造一种基于Cortex-M0和Cortex-M3处理器的SoC2022-07-27 4314

-

Cortex-M0处理器的中断请求形式:电平触发和脉冲输入2022-05-13 3033

-

Cortex-M0处理器的异常处理模型资料下载2021-04-08 1170

-

Cortex-M0处理器的基础知识2021-02-26 3636

-

采用ARM Cortex-M0处理器内核 英飞凌XMC1302马达控制解决方案2017-08-04 16631

-

ARM Cortex-M0权威指南(英文版)2016-10-08 3114

-

ARM推出Cortex—M0处理器2016-01-22 981

-

ARM为主流嵌入式SoC设计提供免费的Cortex-M0处理器IP2015-10-15 2982

-

基于ARM Cortex-M0处理器的LPC1200工业控制系列2011-02-24 1652

-

ARM Cortex-M0处理器内核LPC1100系列微控制2010-08-31 4048

-

恩智浦获得ARM Cortex-M4处理器授权2010-03-03 1790

全部0条评论

快来发表一下你的评论吧 !