SOC芯片的DFT策略的可测试性设计

制造/封装

描述

一、芯片生产过程所引入的问题:

硅片在制程上可能有以下问题:

1、污染造成金属线开路

2、突出的金属导致短路

3、注入掺杂不够

4、制程或掩膜错误

5、金属meta层桥接问题

6、过孔的开路问题

7、CMOS晶体管常开/常关

8、制程问题导致晶体管trans过慢

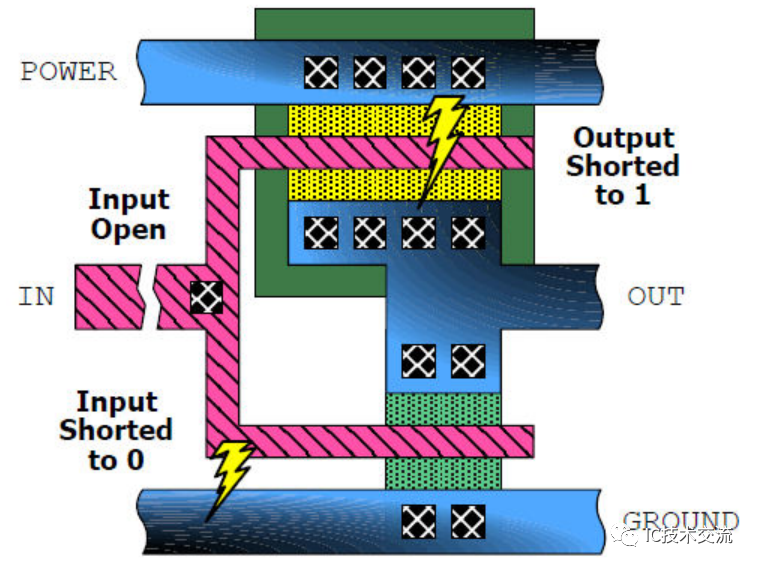

以上图为例,一个非门的版图,可能存在输入断开,输入短接至GND,输入短接至VCC。生产出来的芯片无法保证100%没问题。

制程外可能有如下问题:

1、材料缺陷——大块缺陷(裂纹、晶体缺陷),表面杂质(离子迁移)

2、时间相关故障——介质击穿、电迁移(线很细,电流很大,电子冲击连接处,慢慢接触部分越来越细)

3、封装故障——接触点退化、密封泄露

二、硅后测试

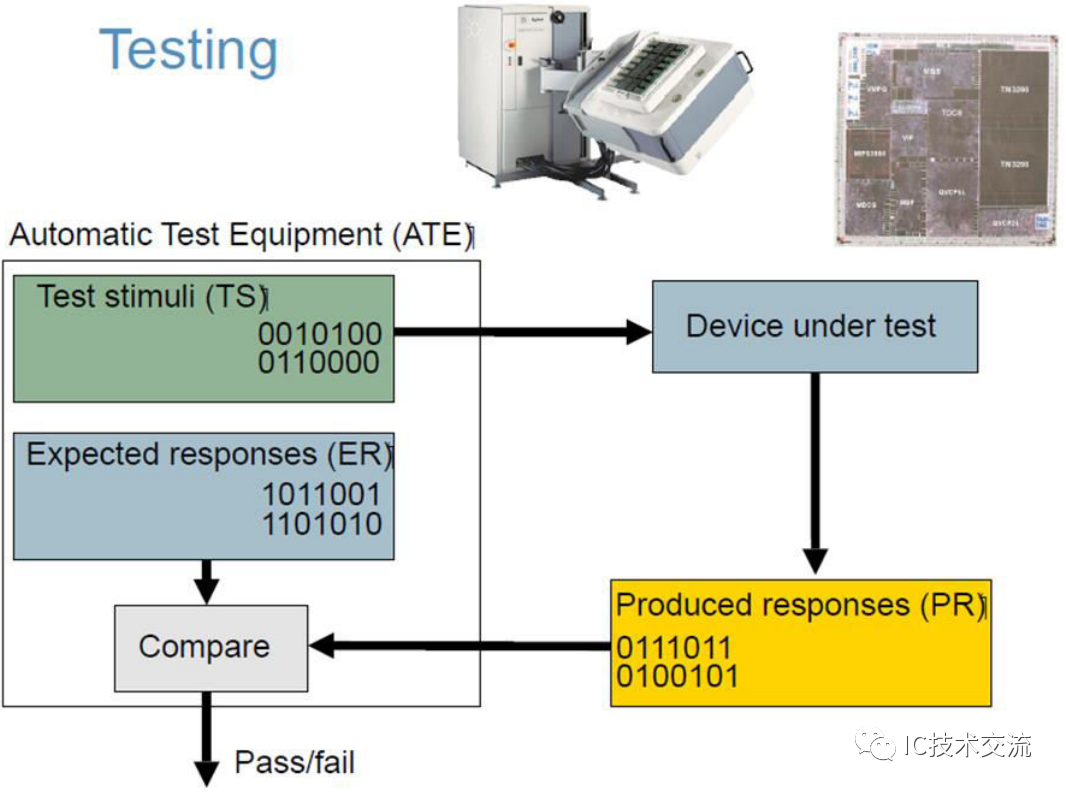

因此在芯片生成后,需对其进行测试,ATE(自动测试设备)会向芯片发送测试激励,然后比较返回的激励与期望激励是否一致,不一致的说明有问题,会将其定为缺陷芯片,以此将好的芯片区分出来。随着设计规模越来越大,工艺尺寸越来越小, 测试成本不断提高,为降低测试成本和难度,提高芯片质量和成品率,需要为芯片进行可测试设计。

以测试阶段可分为以下三种:

1、Wafer sort(CP,circuit probe)

测试wafer上面每个die的逻辑,该项测试最完善,封装前测试出有问题,马上筛除节约成本,该阶段也称为CP综测。

2、Final Test(FT):测试封装后的芯片

3、Board test:板级测试

测试质量的评价:

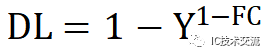

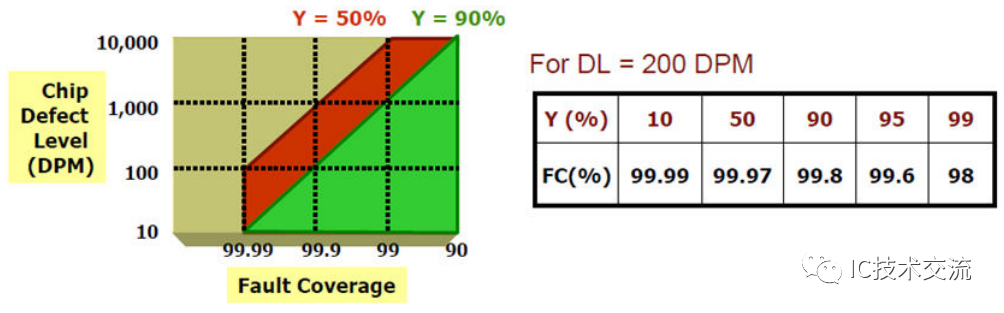

经过测试后每百万片故障的比例DPM(Defective parts per million),200DPM(0.02%)才符合测试标准。Defect level计算公式如下:

其中Y为良率,FC为测试覆盖率(Fault Coverage)。

三、SOC芯片的DFT策略:

SOC是在同一块芯片中集成了CPU、各种存储器、总线系统、专用模块以及多种I/O接口的系统级超大规模集成电路。ASIC是专用于某一方面的芯片,与SOC芯片相比较为简单。由于SOC芯片的规模比较大、内部模块的类型多样,因此SOC芯片的DFT面临诸多问题。SOC中不同部分测试策略也不同:

标准单元——基于SCAN的测试

存储器与模拟模块——BIST

硬核IP、软核IP——BIST,SCAN

封装与IO——Boundary Scan

SOC的全面测试包含以下:

1、DC直流参数测试

①VOH/VOL:输出高/低时的电压

②IIH/IIL:输入高/低时的电流

③IOH/IOL:输出高/低时的电流

④IDDQ:静态漏电流测试

对CMOS来说,输入阻抗很大的,输出阻抗很小的,这要求输入电流必须在某个水平之下,而输出电流必须在某个水平之上。

2、基于SCAN的测试

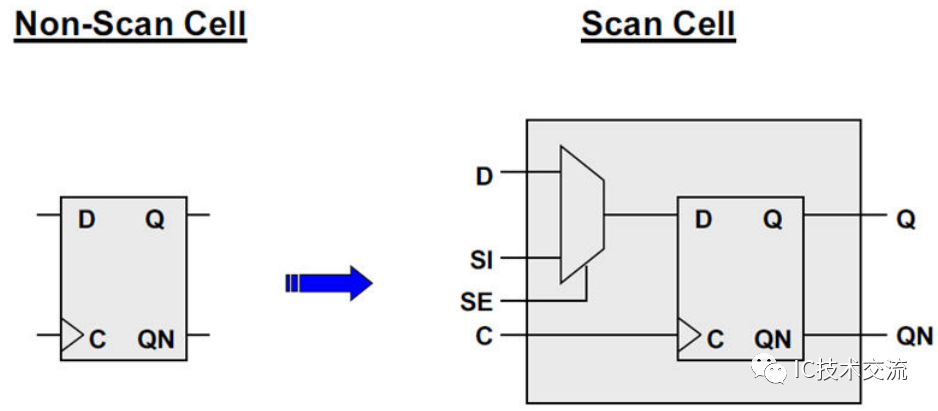

将寄存器替换为可扫描的寄存器(D端输入插入mux)然后串在一起形成扫描链。在测试模式下,将测试序列顺次移入扫描链,这些值经过组合逻辑后,再通过另一条扫描链将结果传出。

3、Memory BIST,Logic BIST,Analog test

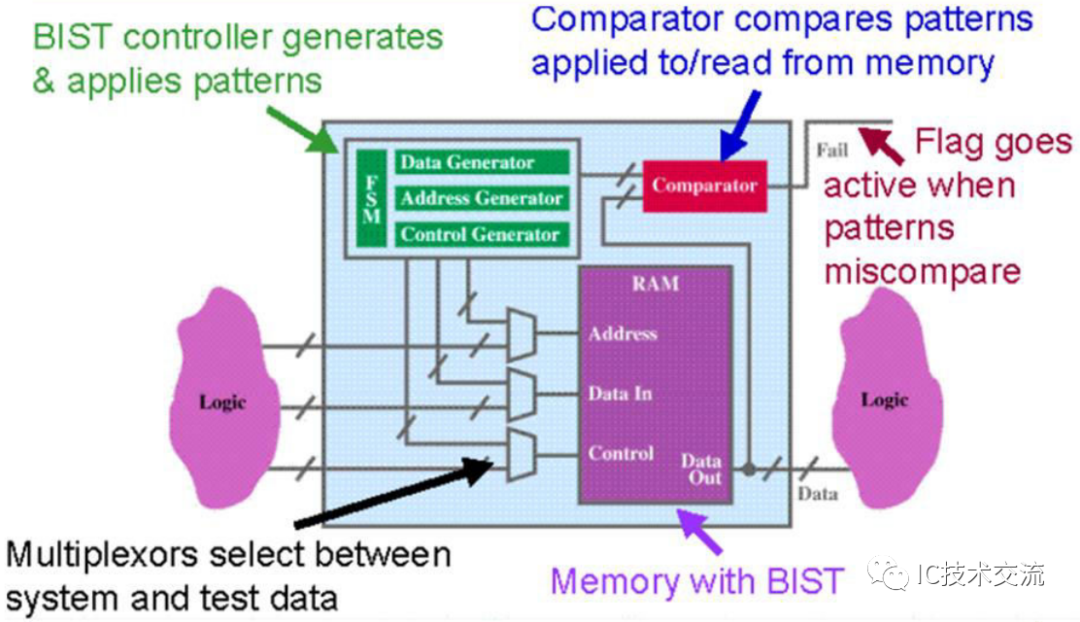

MBIST用于存储器测试,典型的MBIST包含测试电路用于加载,读取和比较测试图形。目前存在几种业界通用的MBIST算法,比如“March”算法、Checkerboard算法等。

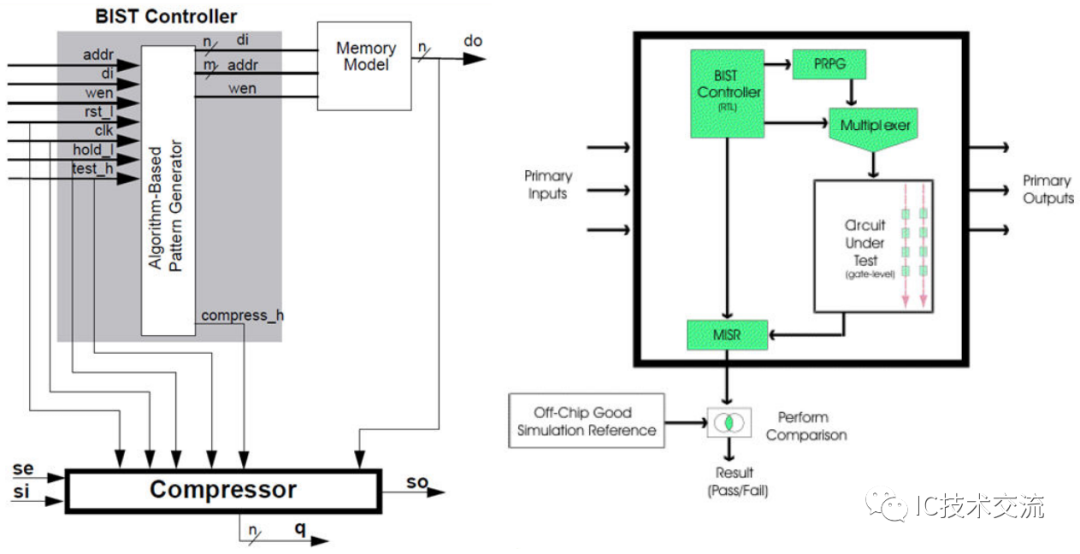

LBIST通常用于测试随机逻辑电路,一般采用一个伪随机测试图形生成器来产生输入测试图形,应用于器件内部机制;而采用多输入特征寄存器(MISR)作为获得输出信号产生器。LogicBIST一般用于Scan Based Test的补充。

AnalogBIST则用于模拟电路的自我测试。

简单来说BIST是自己产生激励,自己比对,给出测试结果,无需在ATE上输入激励测试。

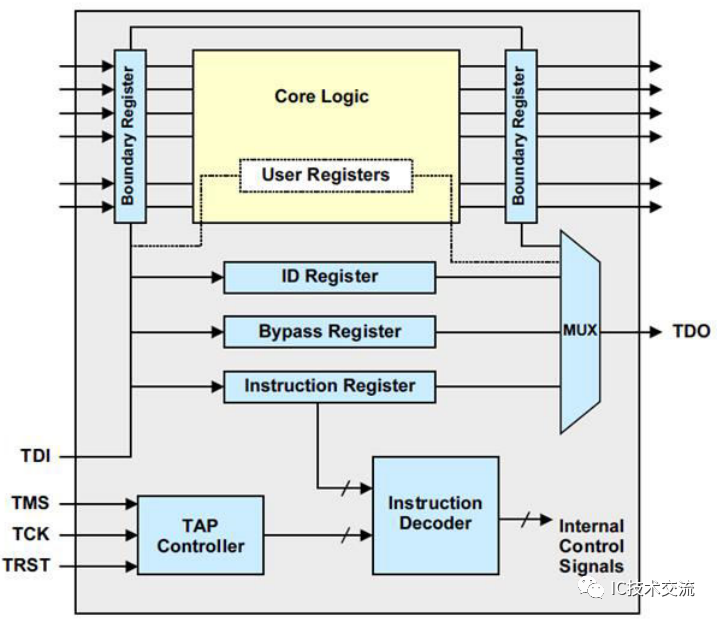

4、Boundary SCAN

边界扫描可用于测试PCB或芯片内部的互联,此外还可作为调试工具,观测芯片内部寄存器,配置等功能。ATE上主要是测试die上的PAD与封装后金属引脚互联的这一段测试。

5、function pattern

用于补充SCAN测试,主要是功能上的测试。

6、ESD测试

静电测试。

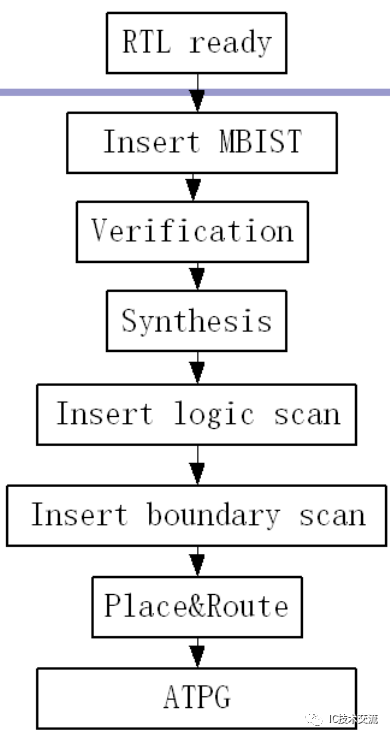

三、DFT在flow中的位置

DFT的主要部分都是在中后端实现的,前期可以插入DFT类rtl,综合之后整体插入scan,布局布线后生成ATPG测试激励。

四、Scan Based Test详细介绍

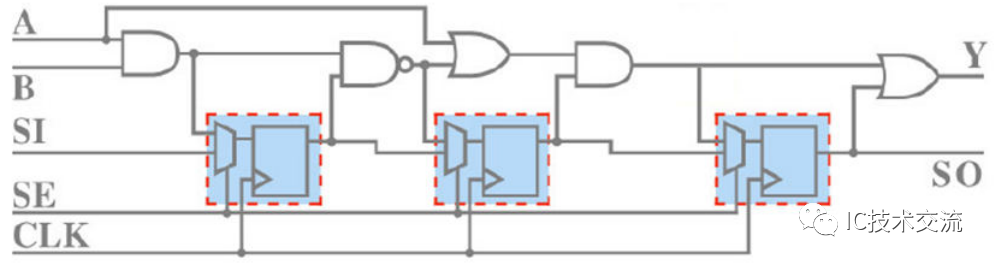

rtl中普通的寄存器是不可扫描的,需在D端插入MUX才是可扫描的,这一步可以在DC中加参数来自动插入。然后将这些寄存器连在一起形成扫描链。当SE为高电平时将激励从SI端口输入进去,这些激励与A/B经过组合逻辑后输出至Y。

这里还需再了解下Fault模型:

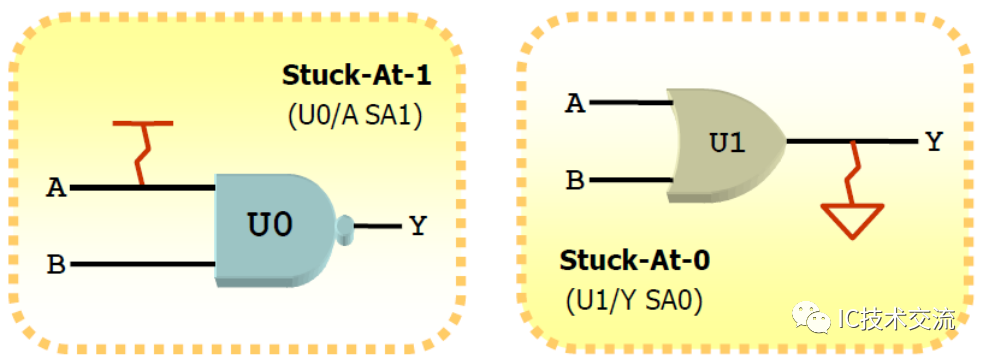

1、Stuck-at Fault——用于低速测试

最常见的一类故障模型。它分为"Stuck-at 1"和“Stuck-at 0”,用来模拟器件间互连的短路和短路故障。

如上图,要测试SA1/SA0需要AB端口给出不同的激励,工具有算法自动推导,这类故障都是在慢速时钟下测试的,统称DC SCAN。

2、At-Speed Fault——用于高速测试

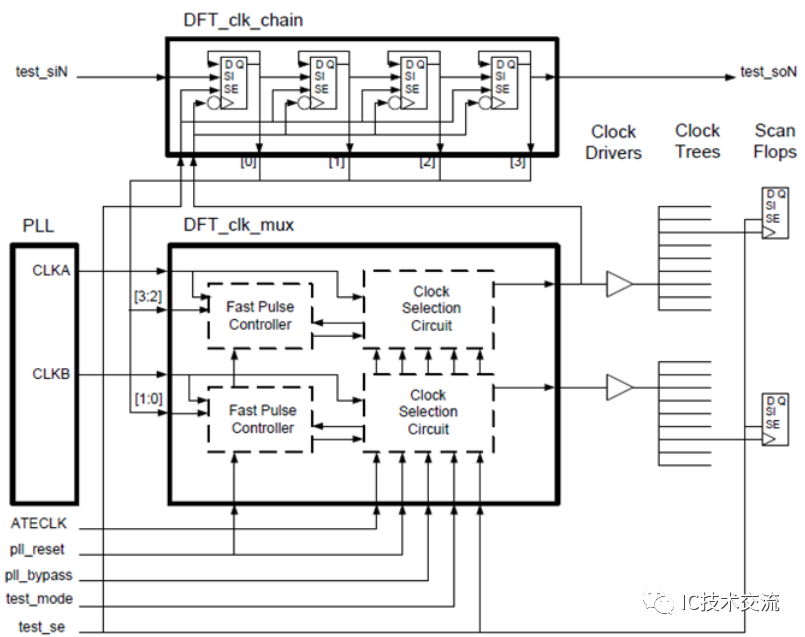

这种故障模型主要用于高速的测试,用片上PLL时钟测试,需要插入OCC电路,OCC的基本原理是在scan shift模式下,选中慢速的ATE时钟进行load测试向量和unload测试结果,在capture模式下,对free-running的PLL clock过滤筛选launch和capture clock进行at-speed测试,这类测试统称AC SCAN。主要分为两大类:

①Transition Fault Model:

a、STR——Slow to Rise

从0跳变至1,是否存在转换延迟的gate;

b、STF——Slow to Fall

从1跳变至0,是否存在转换延迟的gate;

②Path Delay:

Path Delay: 最大延时路径测试。相对于transition test想去覆盖大多数的function path,delay test更关注critical timing path,生成delay test pattern,一般需要读入一个timing report,里面记录那些slack非常小的path,工具会根据report的begin end point产生pattern。

D算法是Scan Based Test的基础,可以认为是拓扑结构测试中最经典的方法,也是最早实现自动化的测试生成算法之一。它是完备的测试算法,它可以检测非冗余电路中所有可以检测的故障。

下面具体说明Scan Test工作步骤:

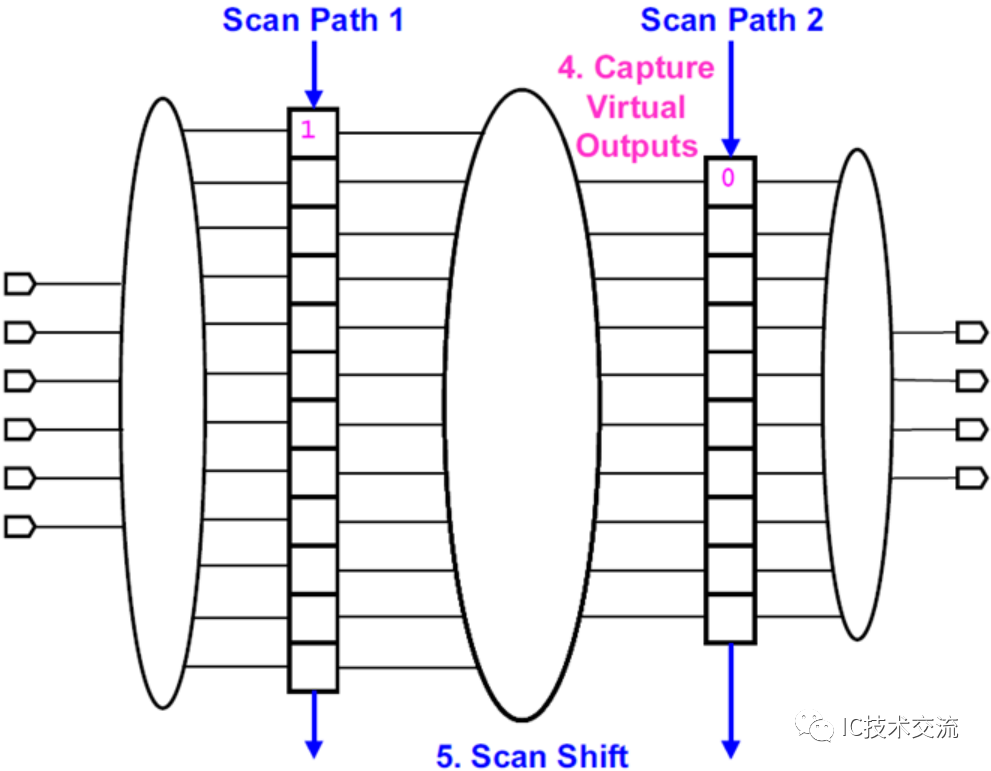

上图中有两条扫描链:Scan Path1和Scan Path2,左侧的端口为Primary Inputs,右侧的端口为Primary Outputs。

1、Scan Shift,两条扫描链移位in

2、给Primary Inputs Force值

3、观测Primary Outputs

4、捕获虚拟输出

5、Scan Shift,两条扫描链移位out

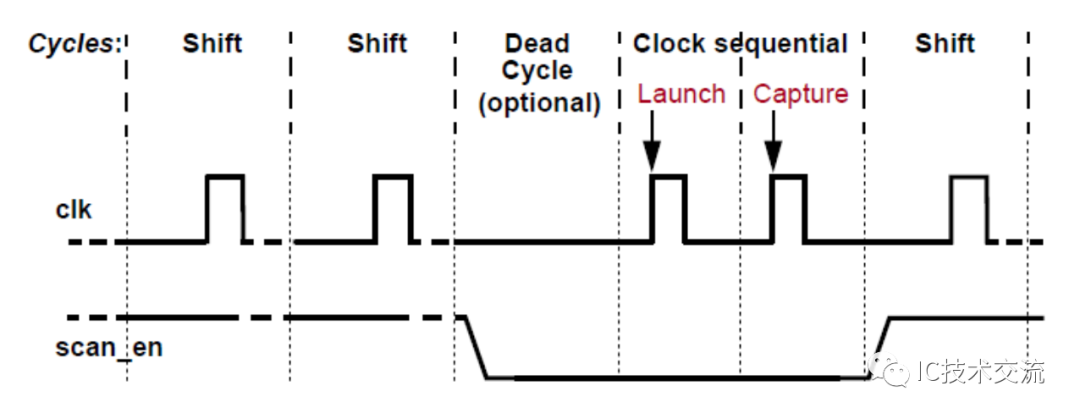

时序图如下所示:

图中当scan_en为低时选择function mode,这里有两个时钟脉冲,一个为Launch,意思是第一条扫描链1的移位寄存器中包含function逻辑,并将相应值输出至Q端,Capture用于扫描链2捕获来自扫描链1的输出值。

在整个扫描过程中实际上测试了三部分逻辑:

1、PI到扫描链1中间的组合逻辑;

2、扫描链1和扫描链2中间的组合逻辑;

3、扫描链2和PO之间的组合逻辑;

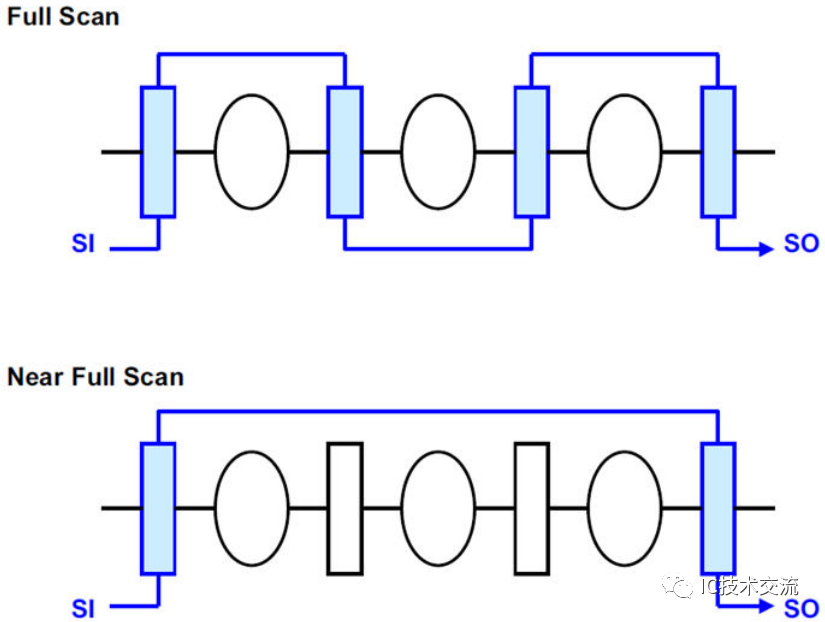

这里还需了解下full scan和near full scan,full scan是一个时钟周期完成capture的扫描链,非full scan可能需要多个时钟周期才能将capture值拿到。

OOC电路如下所示,主要用于ATE慢速时钟和片上PLL快速时钟的动态切换,一般由工具自动插入。

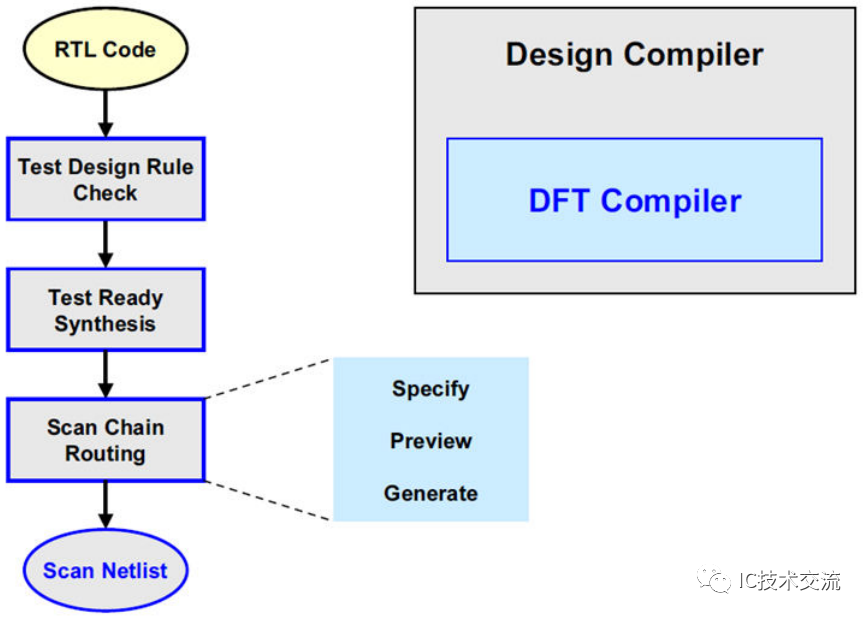

SCAN Chain在综合后插入,工具DFT Compiler已被合并进DC中。

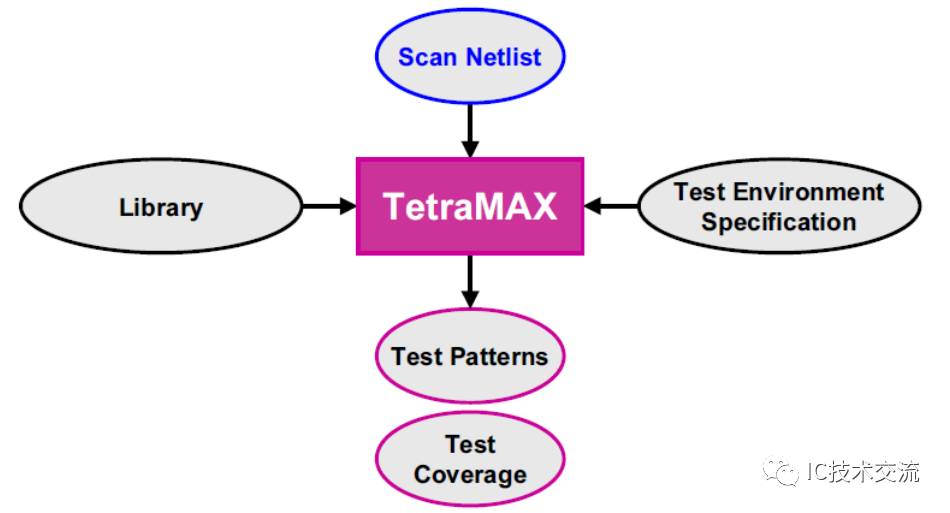

插链后的网表就可以使用TetraMAX软件来生成ATPG以及测试覆盖率。

四、BIST详细介绍

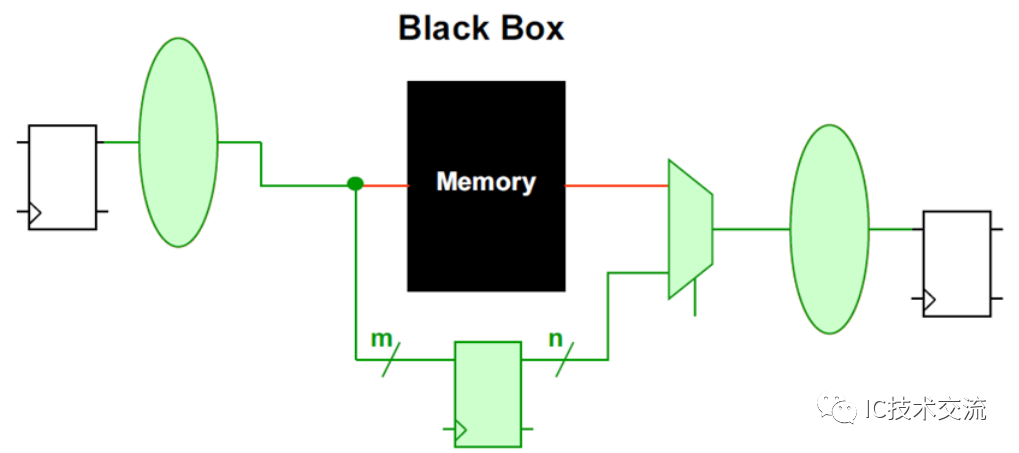

RAM的BIST如下所示,在测试模式下由内部状态机控制执行比较操作,当比较失败时会拉高指示信号。

对于ROM而言,需要将结果拿到片外进行比较,因为ROM中固化的数据可能是不一样的。数据经过HASH压缩后输出至ATE进行比较。Logic BIST与ROM的BIST类似,都需要将结果拿到ATE上面比较。

对于存储器而言,与其相连的前后级寄存器在SCAN中扫描不到,因此可将前后端用寄存器连接起来,这样扫描链就可包含了。

五、Boundary Scan

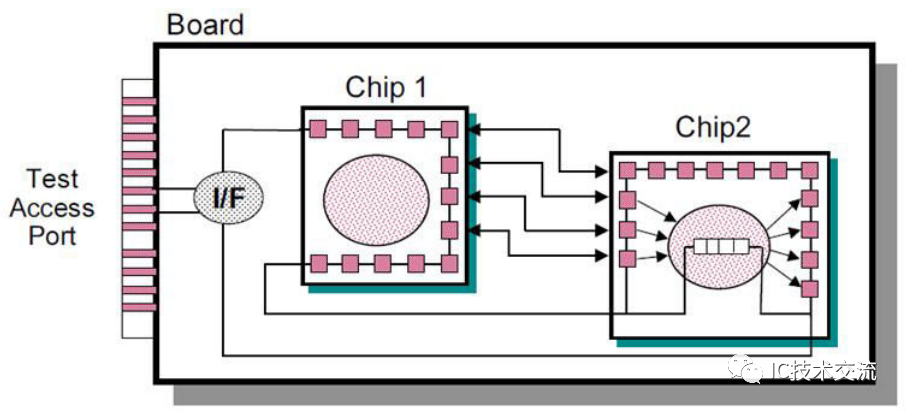

边界扫描不仅可以测试板上芯片的连接关系,也可用于测试package内die的die的互联。

JTAG的结构如下图所示:

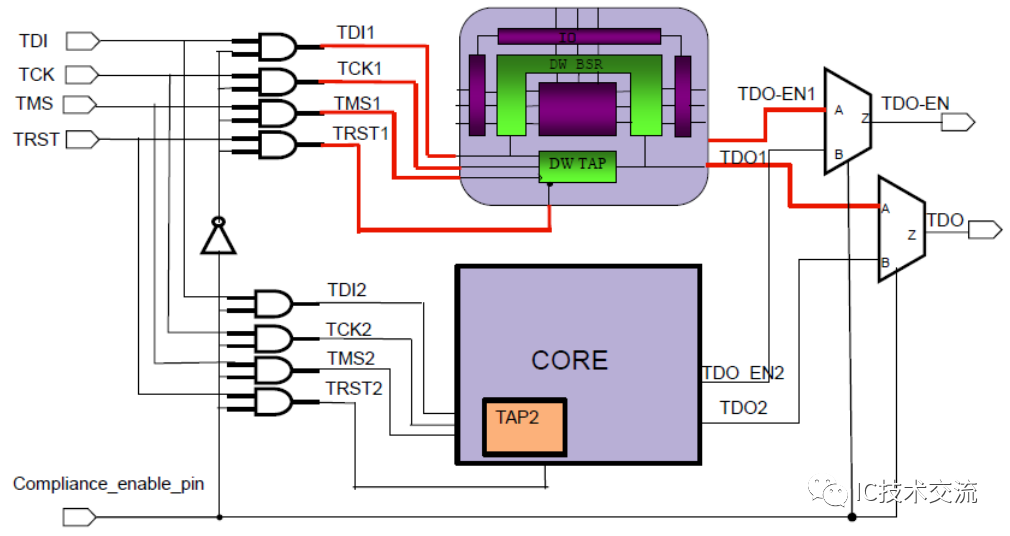

当然片上可能存在多个JTAG TAP,可加入选择信号来控制,如下图所示,有两个TAP,Compliance_enable_pin用于选择使用哪个JTAG。

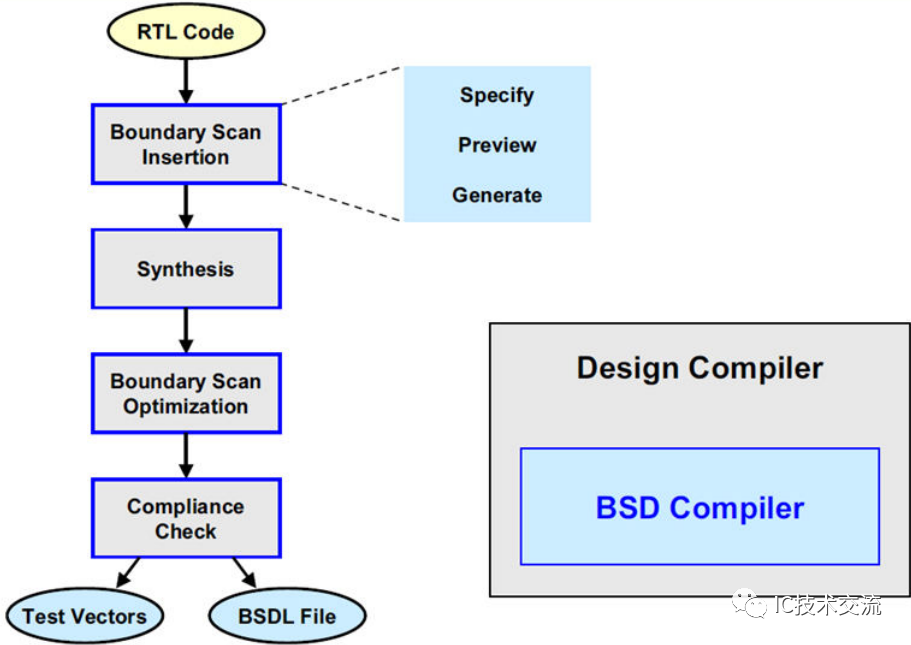

boundary scan可在综合前或综合后插入,BSD Compiler同样包含在DC中。

六、静态功耗IDDQ

主要是测静态下有没有VCC/GND短接在一起,在没有寄存器翻转的情况下如果漏电流过大,可能是输出短接在GND上,其实它是ATPG的一部分。

编辑:黄飞

-

DFT设计—MBIST算法测试2023-12-09 9046

-

DFT和BIST在SoC设计中的应用2011-12-15 6820

-

dft可测试性设计2021-07-22 1339

-

CPU可测试性设计2010-09-21 617

-

什么是DFT,DFT是什么意思2010-06-07 31728

-

SOC的可测试性设计策略2012-04-27 3898

-

PADS DFT审核确保设计的可测试性2019-05-21 4335

-

利用PADS可测试性设计优化PCB测试点和DFT审核2019-05-14 5179

-

可测试性设计(DFT):真的需要吗?2020-10-12 5575

-

分层DFT技术如何实现在最大化SoC2022-11-23 1869

-

解析什么是DFT友好的功能ECO?2023-05-05 3232

-

什么是可测试性设计 可测试性评估详解2023-09-01 2234

-

SoC芯片设计中的可测试性设计(DFT)2023-09-02 4693

-

DFT如何产生PLL 测试pattern2023-10-30 3771

-

一文了解SOC的DFT策略及全芯片测试的内容2023-12-22 5263

全部0条评论

快来发表一下你的评论吧 !