基于500MHz带宽的TPS563209输出电压噪声优化和测试

描述

简介

小功率DCDC芯片及其应用电路已广泛应用于工业和消费等电子类产品中,由于系统中的滤波电路和去耦电容等使系统具有一定的抗高频纹波干扰能力,因此在测量DCDC的输出电压纹波时,示波器的带宽限制通常选择20MHz。但是在某些高精密测量系统和射频应用系统中,高频纹波会给系统带来一系列干扰问题,因此,为了验证DCDC输出电压纹波是否满足系统对于高频纹波的限制,测量电压纹波时示波器带宽限制会选择500MHz,称为DCDC的输出电压噪声测试。由于高频信号易于通过寄生参数进行耦合,所以对于DCDC电路的设计提出了很大挑战。以下通过PCB layout优化,输入输出去耦电容设计,示波器测量方法优化等三方面来有效抑制DCDC输出电压纹波中的高频成分。本文以TPS563209为例进行详细的论述和实验验证。

PCB layout优化

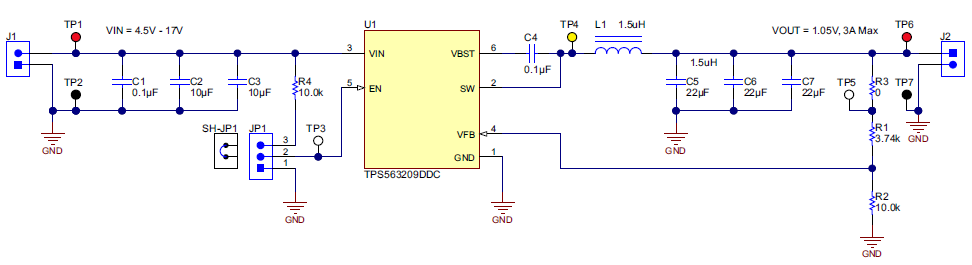

图1是TPS563209EVM-652的原理图,在这个功率电路中,核心的功率回路包含输入电容,芯片内置的高边和低边MOSFET,功率电感和输出电容,因此,在PCB layout的过程中,尽量减小功率回路的走线距离和增加功率回路的走线宽度,可以有效减小功率功率回路的寄生参数,从而有效降低TPS563209工作时产生的高频噪声。

图1 TPS563209EVM-652原理图

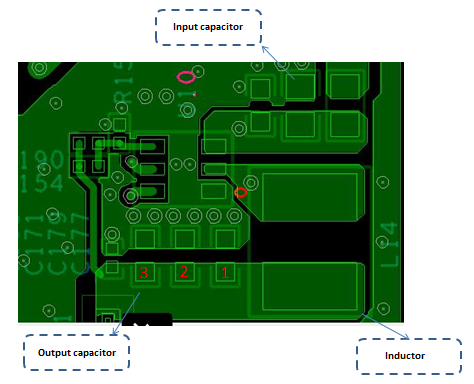

图2是推荐的TPS563209 PCB layout,所有器件均在同一层,GND通过芯片底部走线将输入电容地,芯片地和输出电容地直接连接,输入电容,芯片,电感和输出电容的回路最小,输入端和输出端都有100nF去耦电容,由于开关噪声从开关电路内部产生,所以输入去耦电容靠近芯片VIN脚,输出去耦电容靠近最后一个输出电容,电压采样点选取输出去耦电容的正端。

图2 TPS563209推荐PCB Layout

输入输出去耦电容设计

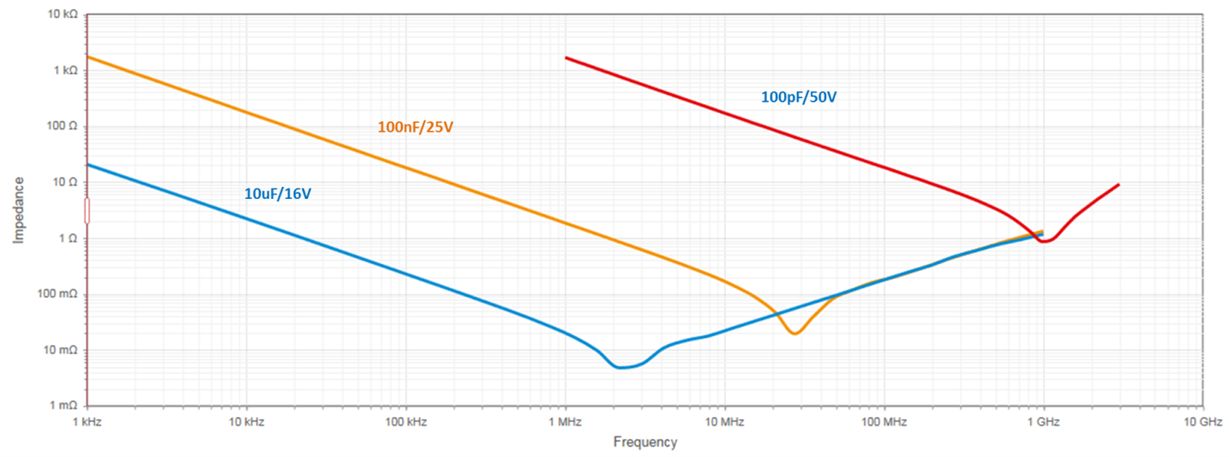

图3是陶瓷电容的频率响应曲线。

在低频时,电容的容抗起主导作用,所以随着频率的增加等效阻抗降低,在高频时,电容的感抗起主导作用,所以随着频率的增加等效阻抗升高。

不同容值的电容对频率的响应曲线不同,如图3,在3种陶瓷电容中,10uF/16V电容容值最大,所以低频时等效阻抗较低,因此在开关电源设计中适合用来做储能电容,例如TPS563209的输入和输出均放置了uF级的陶瓷电容。

100nF/25V电容容值居中,图3中等效阻抗曲线显示转折频率为28MHz,在MHz频率范围的等效阻抗较低,在测试DCDC输出电压噪声时,示波器带宽为500MHz,所以nF级电容在对于DCDC输出噪声的滤波作用较好。本文测试中选择100nF/25V陶瓷电容作为去耦电容。

100pF/50V电容容值最小,等效阻抗曲线显示转折频率为1GHz,所以100pF电容对高频信号的滤波作用较好,一般pF级电容在高频通信中使用较多。

示波器测量方法优化

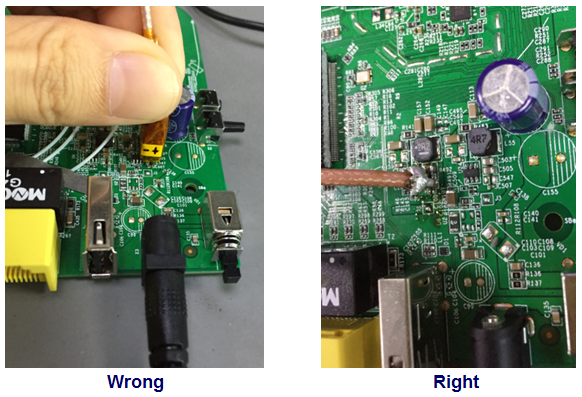

在输出电压纹波的测试中,工程师通常选择图4中左图的测试方式,将同轴线的信号线和地线分别焊接金属探针,然后用手将两个金属探针分别按压在输出去耦电容的正负两端。这种测试方法中金属探针和电容的接触点不牢靠,容易引入高频噪声,但是在输出电压纹波的测试中,示波器带宽通常设置为20MHz,高频噪声可以被有效滤除,所以从示波器显示的信号波形中观测不到高频噪声。

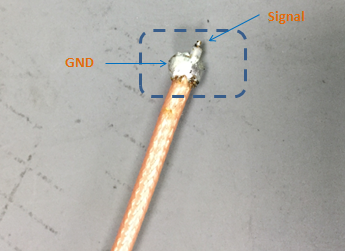

但是在输出电压噪声的测试中,示波器带宽设置为500MHz,高频噪声没有被有效滤除,而是被直接显示在示波器的信号波形中。因此在输出电压噪声的测试中,同轴线需要经过仔细处理,如图5所示,地线和信号线的距离尽量小,以减小高频噪声的耦合回路。然后将同轴线焊接在100nF去耦电容上,如图4中右图所示。

图4 输出电压噪声测试方法

图5 测试同轴线

实验结果

实验条件:

DCDC变换器:TPS563209

输入电压:12V

输出电压电流:1V/3A

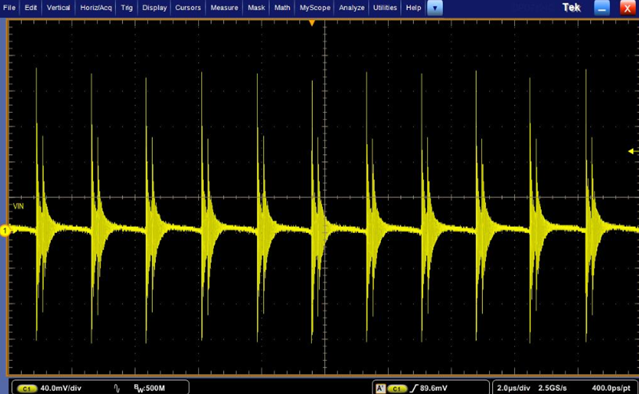

图6是基于较差的PCB layout和错误的测试方法的测试结果,显示输出电压噪声为310mV。

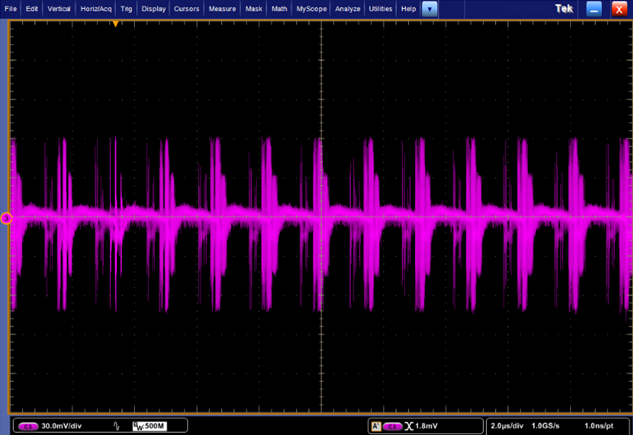

图7是基于良好的PCB layout和错误的测试方法的测试结果,显示输出电压噪声为140mV。

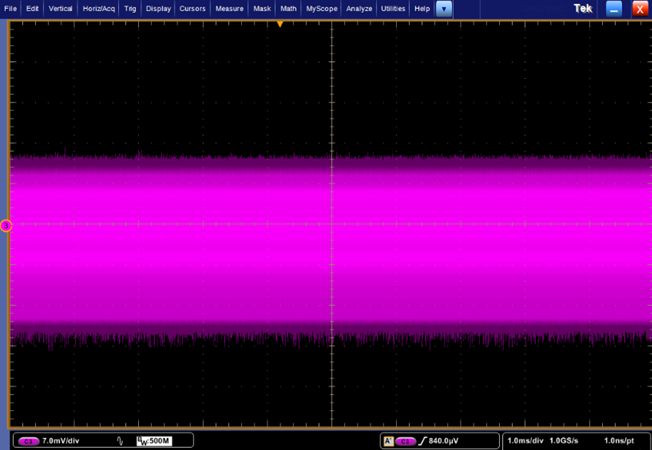

图8是基于良好的PCB layout和正确的测试方法的测试结果,显示输出电压噪声为34mV。

从实验结果可以看出,良好的PCB layout和正确的测试方法对输出电压噪声的测试至关重要。

图6 Bad PCB layout and Bad test method

图7 Good PCB layout and Bad test method

图8 Good PCB layout and Good test method

结论

TPS563209是一款性能优良的DCDC变换器,可以满足对输出电压噪声的严苛要求。

为了获得较低的TPS563209输出电压噪声,在DCDC设计和输出电压噪声测量时需要注意以下3点。

良好的PCB layout。

合适的去耦电容选择。

合理的测试方式。

审核编辑:郭婷

-

如何产生500MHz的时钟信号?2011-10-23 2983

-

DCDC变换器TPS563209在DCDC设计和输出电压噪声测量的应用2019-03-15 3297

-

500MHz单位增益带宽的OPA656运算放大器2020-10-26 2498

-

DCDC变换器输出电压噪声优化和测试2021-07-02 7315

-

基于TPS563209输出电压噪声优化和测试2022-11-11 495

-

500MHz振荡器电路图2009-04-09 1355

-

TPS563209 采用 SOT-23-6 封装的 4.5V 至 16V 输入、3A 同步降压转换器2018-10-16 491

-

MSO/DS4000系列数字示波器带宽100MHz ~ 500MHz2020-04-25 2454

-

DC696A LT5546EUF | 具有VGA和I/Q解调器和宽基带带宽的500MHz IF接收器2021-05-28 899

-

运算放大器噪声优化手册2021-05-31 2036

-

以TPS563209为例进行详细的论述和实验验证2022-01-11 2522

-

基于500MHz带宽的TPS563209输出电压噪声优化和测试2022-11-01 595

-

TPS563209降压转换器评估模块用户指南2024-12-04 420

-

TPS563209 17 V 输入、3A 同步降压稳压器,采用 SOT-23 封装数据手册2025-06-24 990

-

TPS563209降压转换器评估模块使用指南2026-04-25 229

全部0条评论

快来发表一下你的评论吧 !