功能性SPI隔离

描述

假设恒定的接地电压有助于我们分析电路,但事实并非如此 必然准确。1寄生电感和大高电平的组合 频率电流在电路接地上产生电压噪声。例如 可能导致大高频电流流过接地参考 来自数字电路中的数千个晶体管同时切换。 这对于敏感的模拟组件(例如模数转换器)来说是个坏消息 使用数字元件接地的转换器 (ADC)。

为模拟元件提供干净的接地参考非常重要。 实现多点接地系统并滤除模拟 电路的电源连接是有用的技术。数字隔离允许 具有不同接地参考并仍保持通信的组件 链接。用于将接地噪声与敏感接地噪声隔离开来 不需要安全隔离的组件,隔离等级高 是不必要的。具有1 kV rms耐压的数字隔离器,例如 ADuM744x系列足以实现接地噪声隔离 应用。

图1所示为ADuM7441在微控制器之间隔离SPI总线 和一个ADC,允许它们使用单独的接地基准工作。 表1列出了最大SPI时钟频率 ADuM7441A和ADuM7441C采用5 V和3.3 V电源供电,因为它们 最大传播延迟。2有关以下方面的信息,请参阅参考文献 2 为隔离式SPI总线计时。

图1.

| 型 | 电源配置 (V) | 最大传播延迟 (ns) | 最大高射频率(兆赫) |

|

ADuM7441A |

3.3 | 85 | 2.9 |

| 5.0 | 75 | 3.3 | |

|

ADuM7441C |

3.3 | 66 | 3.7 |

| 5.0 | 50 | 5.0 |

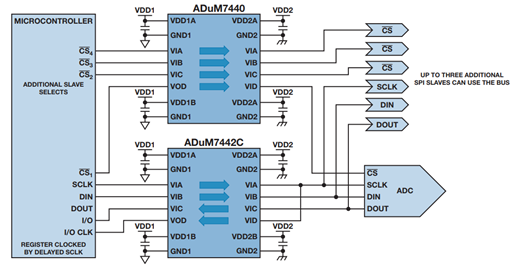

隔离式SPI总线的替代实现如图2所示。 在这种情况下,来自ADC(DOUT)的数据被时钟输入到一个单独的寄存器中。 通过SCLK的延迟版本;此实现还允许另外三个 从设备。采用此配置的ADuM12x系列,SPI总线的时钟速率最高可达5.744 MHz。图7442中的ADuM2分离器件 SCLK、DIN 和 DOUT;ADuM7440隔离<>个CSX信号。三 ADuM7440中的其他通道可用于隔离CSX信号 另外三个从设备。或者,也可以使用ADuM140x系列。 在这种配置中,时钟速率高达 45 MHz。延迟时钟 实现允许SPI总线在数字隔离器的 最大数据速率。

图2.

审核编辑:郭婷

-

模块电源功能性参数指标及测试方法2013-03-04 6444

-

移动设备怎么实现多重功能性2019-06-12 1381

-

视频差动放大器为低压应用带来多功能性2019-06-13 1059

-

功能SPI隔离2019-06-20 1184

-

LTC1590双通道12位DAC的应用多功能性2019-06-27 2917

-

设计一个具有功能性/免费和开源的USB编程器2022-07-28 1469

-

基于非功能性特征的软件动态自演化框架2009-04-07 531

-

PCB外观及功能性测试相关术语2009-11-14 751

-

功能性SPI隔离低功耗应用2012-05-30 1273

-

非功能性垫片有哪些作用2019-10-06 5087

-

可变参数的功能性修复最小存储再生码2021-06-17 843

-

通过多路复用提高 NLSF595 的多功能性2022-11-15 407

-

基于Fork的功能性支架2022-11-18 604

-

如何通过智能布线提升新建筑的功能性?2024-12-02 1139

-

功能性电刺激(FES)—神经假肢2025-06-26 10134

全部0条评论

快来发表一下你的评论吧 !