Kioxia和Western Digital宣布第8代218层3D NAND闪存

存储技术

描述

Kioxia 和 Western Digital 宣布第 8 代 218 层 3D NAND 闪存。

Kioxia与Western Digital(WD)于3月30日宣布了一款218层三维NAND闪存,将成为第8代BiCS FLASH。

218层3D NAND产品部署在4-plane operation 1T-bit TLC和QLC,采用平面缩放技术,通过引入数种独特的工艺和架构实现,比上一代快50%。据称比特密度提高了10%以上。此外,利用晶圆键合技术,开发了CBA(CMOS directly Bonded to Array)技术,用于键合分别制造的CMOS电路晶圆和存储单元阵列晶圆。

传统上,控制逻辑和单元逻辑是在一个晶圆上单片制造的。SK 海力士将其这种制造版本称为 Peri Under Cell (PUC),而 WD 和 Kioxia 将其称为 CUA(Circuit Under Array)。Kioxia CTO Masaki Momodomi 在一份声明中表示:“通过我们独特的工程合作伙伴关系,我们成功推出了具有业界最高位密度的第八代 BiCS FLASH。我很高兴 Kioxia 已经开始为有限客户提供样品。”

WD 技术与战略高级副总裁 Alper Ilkbahar 补充说:“通过使用一个共同的研发路线图和对研发的持续投资,我们已经能够提前将这一基础技术产品化,并提供高性能、资本高效的解决方案。”

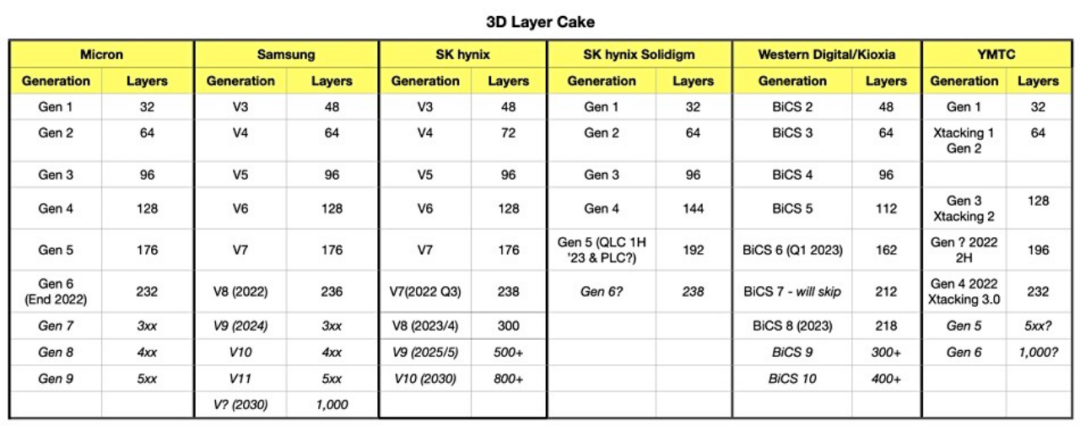

NAND供应商层数代表

Kioxia 和 WD 声称他们可以在其 218 层芯片中提高单元密度,因为它们在横向和垂直方向上都缩小了单元。他们表示,这会以优化的成本在层数更少的更小芯片中产生更大的容量。

238 层芯片具有 1 TB 容量,采用 TLC(3 位/单元)或 QLC(4 位/单元)格式。该芯片的 IO 速率为 3.2Gbps,比之前 BiCS 6 芯片的 162 层 NAND 高出 60%。与 BiCS 6 技术相比,还有 20% 的写入性能改进和更低的读取延迟。

Kioxa 和 WD放弃了中间 BiCS 7 技术,CUA 开发和单元收缩使 BiCS 8 成为可能。

市场可能在一两个季度内看到使用 BiCS 8 技术的 SSD。

内存供应商进入200层竞赛

内存供应商正在竞相为 3D NAND 添加更多层,数据爆炸以及对更大容量固态驱动器和更快访问时间的需求推动了3D NAND市场的竞争。

美光已经在完成 232 层 NAND 的订单,而且不甘示弱,SK 海力士宣布将于2023年上半年开始量产 238 层 512Gb 三层单元 (TLC) 4D NAND。或许更重要的是,芯片制造商私下表示,他们将利用行业学习为目前正在开发的 3D-IC 堆叠 NAND。

西门子 EDA技术产品经理 Ben Whitehead 表示:“处理器的摩尔定律在过去几年中可以说一直滞后,但对于 NAND 闪存来说,摩尔定律仍然存在并且很好。” “这是一件好事,因为现代计算和网络对快速存储有着无法满足的需求。”

回顾 2D NAND,它具有平面架构,浮栅 (FG) 和外围电路彼此相邻。2007 年,随着 2D NAND 达到其规模极限,东芝提出了 3D NAND 结构。3D 设计引入了多晶硅和二氧化硅的交替层,并将浮栅交换为电荷陷阱闪存 (CTF)。这些区别既有技术上的,也有经济上的。FG 将存储器存储在导电层中,而 CTF 将电荷“捕获”在电介质层中。由于制造成本降低,CTF 设计很快成为首选,但肯定不是唯一的。

IBM 研究员 Roman Pletka 指出:“尽管所有制造商都转向电荷陷阱单元架构,但我预计传统的浮栅单元在未来仍将发挥不可忽视的作用,尤其是对于容量或保留敏感的用例。”

海力士表示,尽管有摩天大楼式堆叠的创新,但第一代 3D NAND 设计将外围电路保留在一边。

2016 年,专家指出,由于技术问题,3D NAND 可能会在 300 层或接近 300 层时失去动力。这似乎已被今天的谨慎乐观所取代。

“在 SK海力士的 238 层之后我预计未来几年层数将以大致相同的速度增加,”IBM 的 Pletka 说。“然而,从技术角度来看,由于高纵横比蚀刻工艺,增加层数受到挑战,而且资本支出也受到挑战,因为制造芯片的时间随着层数的增加而增加。这就是为什么我们将通过制作更薄的层、横向缩放(例如更密集地放置垂直孔)以及使用更有效的布局(例如共享位线和逻辑缩放)来看到新的缩放方向(例如,使用拆分门架构或存储更多每个单元的位数)。有了这些技术,预计 NAND 闪存的存储密度至少在未来 5 到 10 年内会以类似的速度增长。”

三星的 Kinam Kim 发表了一个主题演讲,他预测到 2030 年将有 1000 层闪存。这听起来可能令人头晕目眩,但这并不是完全的科幻小说。“与 NAND 闪存的历史趋势线相比,这已经放缓了,”imec 存储存储器项目总监 Maarten Rosmeulen 说。“如果你看看其他公司,比如美光或Western Digital,他们在公开声明中提出的内容,他们甚至比这还要慢。不同的制造商之间也存在一些差异——似乎他们正在延长路线图,让它放慢速度。我们相信这是因为保持空间运转需要非常高的投资。”

编辑:黄飞

-

3D NAND闪存来到290层,400层+不远了2024-05-25 6399

-

铠侠计划2030-2031年推出千层级3D NAND闪存,并开发存储级内存(SCM)2024-04-07 1561

-

什么是3D NAND闪存?2023-03-30 4733

-

Kioxia和西部数据合作开发第六代162层3D闪存技术2021-02-20 3041

-

美光科技宣布已批量出货全球首款 176 层 3D NAND 闪存2020-11-12 2877

-

美光宣布了其第五代3D NAND闪存技术2020-11-11 3318

-

Western Digital和Kioxia宣布BiCS5 112层3D NAND2020-02-13 7497

-

西部数据和Kioxia研发第五代BiCS 3D NAND成功,今年实现量产2020-02-04 5427

-

Kioxia展示了NAND闪存的潜在替代产品2019-12-23 5354

-

SK海力士开始采样128层3D NAND SSD2019-11-25 6845

-

中国量产64层3D NAND闪存芯片会带来什么影响2019-09-23 1570

-

中国首次量产64层3D NAND闪存芯片会有什么市场影响2019-09-19 1268

-

SK Hynix月底量产48层堆栈3D NAND闪存 三星后第二家2016-11-09 1183

-

三星48层3D V-NAND闪存技术揭秘2016-07-13 7751

全部0条评论

快来发表一下你的评论吧 !