使用硬件加速仿真进行有意义的功耗分析

描述

功耗分析和优化在最近几年逐渐引起了人们的重视,大多数 IC 设计团队现在都会为了功耗管理在自己的流程中纳入功率管理步骤和工具。尽管如此,功耗分析任务往往要基于验证场景,而这些场景过于基础,并且与实际系统使用完全脱节。

本白皮书将解释说明,使用真实的有效载荷为何对于准确估算功耗和执行优化任务而言至关重要。之后,我们将会展示Veloce客户如何使用硬件加速仿真来实现可靠性高得多的使用模型,并且利用这一模型,可以更可靠地识别和分析潜在的功耗问题。

有效矢量的激励

在功耗方面,设计人员有着许多不同的目标和关注点。一方面,团队需要确保其芯片的平均功耗足够低,以保证延长电池的续航时间。另一方面,团队的主要关注点可能是预防出现局部感性电压降,该电压降会破坏芯片的功能。但不论哪种情况,使用不够真实的矢量执行任何分析都会导致所得的结论和决定不正确。

功率估算

其中一个使用最普遍的功耗分析任务是估算整个芯片在较长时段内的平均功耗。执行此任务的目的通常是确保凭借低能耗芯片保证延长电池续航时间,节省能源费用和/或简化散热方案,从而获得竞争优势。很显然,通过仿真生成有代表性的有效载荷可能变得极具挑战性,而且很多设计人员都会采用分而治之的方法,这种情况下,他们可以收集不同子模块的数据并组合在一张电子表格中。这种方法是否值得信赖,这是设计团队在从制造厂取回自己的芯片之前苦思冥想的一个问题。

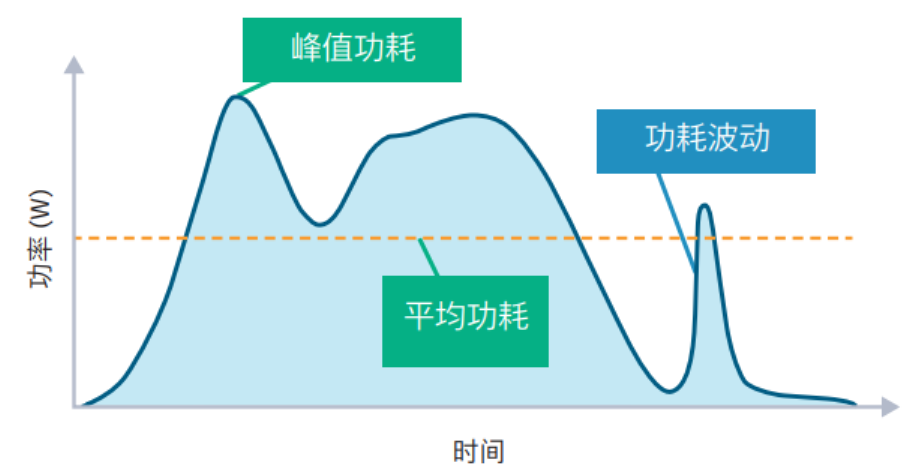

图 1. 不同类型的功率估算。

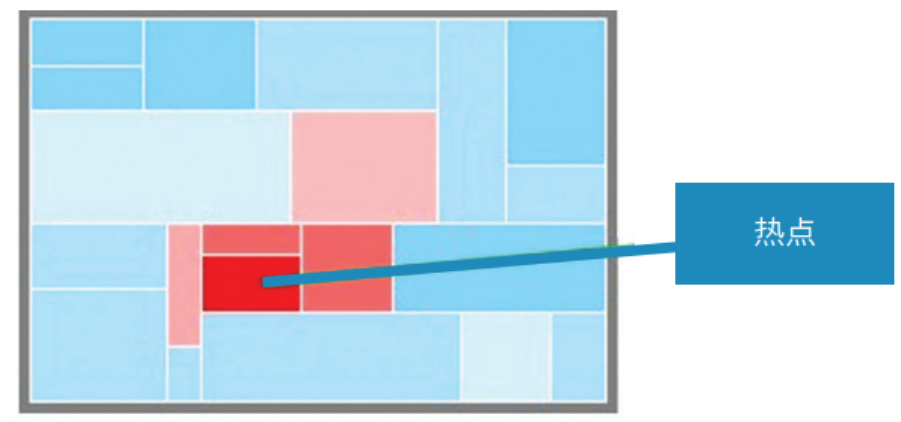

而在其他情况下,人们关注的是峰值功耗(图 1)。关于峰值功耗,根据问题的性质,必要的分析可能因空间和时间范围而大相径庭。举个例子,问题可能出在一个局部的快速现象,例如可能在一个时钟周期内发生的电压降(阻性或感性)。或者,也可能是更全局性的问题,例如当电流高于给定阈值的时间超过一定时间(譬如说几毫秒)时所导致的电源完整性违规等。如果关注的是散热问题,需要识别的峰值还可能分布在较宽的范围。而且,如果空间范围小于整个 SoC,则设计人员将需要识别局部热点,并执行层次化或基于底层规划的分析(图 2)。

图 2. 局部热点识别。

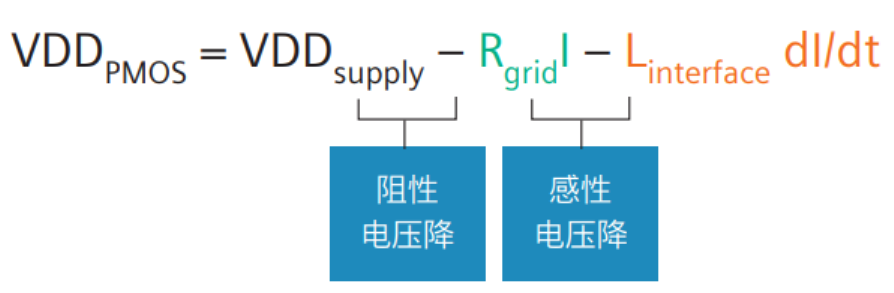

最后,除了空间和时间范围考虑之外,有时设计人员感兴趣的不仅仅是功耗水平,还有变化率。这是因为在高级技术节点,电压降的感性分量会变得与阻性分量一样关键(图 3)。

图 3. 电压降类型。

降低功耗

除以上所列的全部功率估算目标之外,使用有代表性的活动数据对于相关的功耗验证和优化任务也是至关重要的。例如,可以考虑一个非常复杂的 SoC 情形,其中往往可以看到几十个电源域(其中一些使用保留策略)和复杂的时钟方案。这种情形下,特别当功率控制器是基于软件时,能否以统一功率格式 (UPF) 的形式考量实际系统使用并解释功耗意图,对于完整的功耗验证非常关键。

要在 RTL 中降低功耗,也是如此。降低功耗所用的大多数(即使不是全部)方法对于信号层的活动水平估算非常敏感。确定是否应该直接对数据门控或时钟门控运用稳定性或可观测性条件取决于出现这类条件的概率。因此,设计人员在接受工具自动建议或实施的修改之前,需要考虑真实的系统有效载荷。

审核编辑:汤梓红

-

高通收购NXP真的有意义吗?2016-10-27 3567

-

用于软件验证的硬件加速仿真之一:物理和虚拟探针2017-08-18 2537

-

硬件加速模块的时钟设计2025-10-23 250

-

MCU厂推多样解决方案 DSP/FPU硬件加速芯片整合2016-10-14 2255

-

横河测量测试 对于要求较高的测试应用,非常有意义2019-01-21 1906

-

Mentor Graphics硬件加速仿真服务使用Veloce 硬件加速仿真平台加速验证2016-04-20 3001

-

Mentor Graphics Veloce 硬件加速仿真平台协助 Barefoot Networks 验证全球首个完全可编程开关2016-07-20 1592

-

基于硬件加速的实时仿真平台构建技术2017-01-03 972

-

MD5算法硬件加速模型2018-01-12 1025

-

忆芯科技利用Veloce 硬件加速仿真平台进行高速企业级固态硬盘存储设计2018-07-12 2243

-

Veloce仿真环境下的SoC端到端硬件加速器功能验证2018-03-28 4706

-

使用硬件加速仿真的功耗分析2018-03-01 720

-

利用硬件加速器提高仿真速度时的验证平台考虑2018-03-05 1552

-

分享硬件加速仿真的 11 个谬论介绍和说明2019-10-11 6115

-

基于Arduino的矫枉过正但具有意义的COVID流行病展示2022-11-01 588

全部0条评论

快来发表一下你的评论吧 !