串行通信接口SPI接口介绍

电子说

描述

前言:

接口的存在是使得芯片的设计达到 模块化 ( modularity ),就像在第一篇文章所讲到的,我们可以通过不同的IP组成一个功能完备的芯片(或称之为 SoC )。

芯片的接口可以分为两大类:片上通信接口与 片外通信接口 。以AMBA为代表的片上接口主要有灵活,效率高的优势,而片外接口的选择则更加广泛,根据不同的成本需求或是性能需求,能够选择的片外通信接口有IIC,SPI等。

今天讨论的SPI接口是一种十分常用的片外通信接口,经常作为芯片与片外存储器(多为 serial nand flash )的通信接口。同时,硬件物理接口也是应届生面试时被提问最多的问题之一。有意在毕业后从事计算机硬件行业的朋友们可以在准备应聘的时候多多储备这方面的知识。

SPI接口介绍

SPI是一种串行通信接口,全称是 Serial Peripheral Interface 。它是一种 full-duplex (全双工:支持发射端TX与接收端RX同时双向传输数据)接口。最基础的SPI接口由四根线组成:

- SCLK(Serial Clock)

- SS(Slave Select或CS:Chip Select)

- MOSI(Mater Out Slave In)

- MISO(Mater In Slave Out)

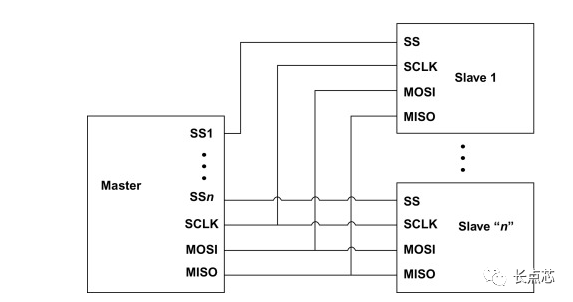

如下图。

SPI接口pin

1. SCLK:

首先是这根时钟线,这也是将接口分为 Synchronous (同步接口)与 asynchronous (异步接口)的重要标志。由于异步接口发送与采集数据没有一个统一控制信号,所以没法确保发送端与接收端有相同的收发 data rate, 这给现在许多使用同步设计方法的芯片带来的很多难题,所以这也是目前同步接口更受欢迎的原因。

异步通信接口

同步通信接口

不过当然了,异步接口也有它的好处。可以在数据的起始位和终止位来添加两个 flag (标记符)来控制数据的接收,而且需要在使用前确保两个模块收发数据的速率是相同的。

所以要是有了这个由 Master (一般是一个 microcontroller )发出的CLK给slave,slave端就知道什么时候接受数据了,可以是上升沿也可以是下降沿,一般由datasheet决定。时钟的频率也取决于slave能够正常工作的时钟频率范围,一般在80MHz左右。

2.SS/CS:

因为SPI接口有时候会连有多个Slave(一般不超过三个),所以随着slave的增加,master端就会需要越来越多的pin口。当Master与slave处于断链状态时,SS/CS一般是置成高位的,这样在master决定要给与哪个slave交互的时候就会把相应的SS/CS置低,称作 active low 。

3.MISO/MOSI:

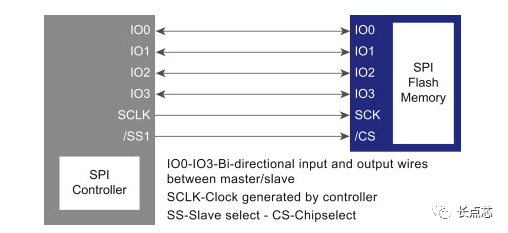

剩下的几个接口都是SPI的数据线,在每个时钟周期内,master都会向slave发送1bit数据,slave也可以同时向master发送1bit数据。所以说假设某个SPI接口正工作在50MHz的时钟频率,那么它的数据传输速率可以达到50Mbps/100Mbps(随着数据线的增加SPI的数据传输速率还能增大更多)。相较于普通的IIC接口已经高出不少了。这也是为什么对于许多传感器来说会选择SPI接口。

多位宽数据pin口的SPI通信接口

其实呢,SPI作为一个常用的外设接口,却不存在一个标准,因此没有用于验证给定产品的接口一致性的基准。。所以SPI可以说是一个 * de facto standard ( 在实践中被接受,但尚未经过任何正式程序以达成共识的标准,甚至可能没有公开可用的文档 )。* * *

A de facto standard :is one that has become accepted in practice but has not undergone any formal process to obtain consensus and may not even have publicly available documentation。

并且在SPI中没有任何通信流程控制单元,SPI的硬件实现有时候就是靠一个简单的 shift register ,时钟这个唯一的控制信号的稳定性至关重要。除此之外,如何确保数据的传输是否准确也十分重要,一般只能通过软件来检测。在一些 real-time embedded system (实时嵌入式系统)中,软件必须以比数据到达更快的速度处理接收到的数据。通过接收端的FIFO Buffer,可以缓解此问题。SPI接口中没有嵌入到错误检测和校正功能中。如果需要,必须在软件中实现错误检测/纠正。

-

基于PC/104 总线与CPLD 的SPI 接口设计2009-05-30 1139

-

SPI接口读写串行EEPROM2009-09-19 1126

-

串行接口SPI接口应用设计2011-11-07 895

-

AVR单片机串行接口SPI接口应用设计2011-11-09 4364

-

一文读懂SPI串行外设接口2017-04-27 10814

-

基于MSP430F2的SPI串行同步通信2017-09-21 932

-

串行外设接口SPI通信协议的应用2019-01-09 2635

-

嵌入式硬件通信接口协议中的串行通信接口-SPI2019-02-05 2166

-

Firefly-RK328-SPI接口介绍2019-11-25 2765

-

Firefly-RK3128--SPI接口介绍2019-11-28 4079

-

通信接口的作用_常用的串行通信接口有哪些2020-03-28 18485

-

基于SPI串行总线接口的Verilog实现2021-05-29 6200

-

SPI 串行外设接口2021-12-20 902

-

SPI串行外设接口设计实现2023-05-29 2342

-

串行通信接口SPI与QSPI的区别2025-04-09 3591

全部0条评论

快来发表一下你的评论吧 !