SoC接口技术之低速接口分析(下)

电子说

描述

4.协议解析

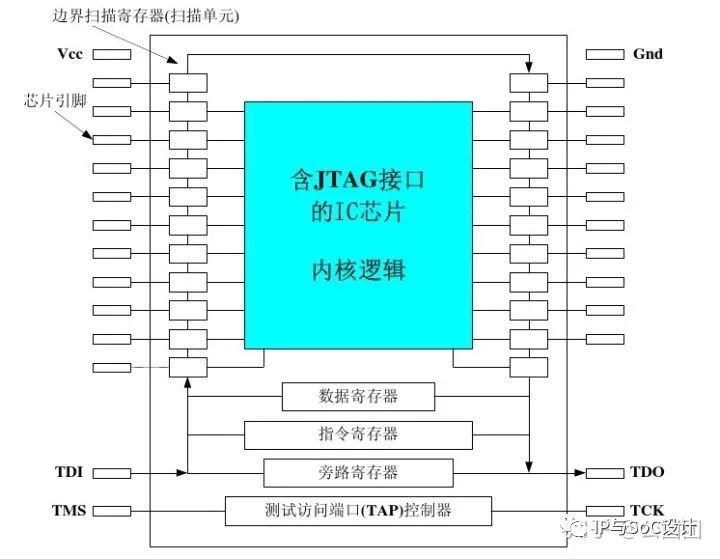

JTAG协议核心是三个寄存器和TAP状态机。作为DEBUG的JTAG接口会在DAP中利用旁路寄存器将JTAG协议转换为APB协议。作为DFT的JTAG接口会直接利用数据寄存器进行边界扫描。

JTAG协议通过TMS信号控制TAP状态机的转换。

系统上电后,TAP Controller首先进入Test-LogicReset状态,然后依次进入Run-Test/Idle、Selcct-DR- Scan、Select-IR-Scan、Capture-IR、Shift-IR、Exitl-IR、Update-IR状态,最后回到Run- Tcst/Idle状态。

在此过程中,状态的转移都是通过TCK信号进行驱动(上升沿),通过TMS信号对TAP的状态进行选择转换的。

其中,在 Capture-IR状态下,一个特定的逻辑序列被加载到指令寄存器中;在Shift-IR状态下,可以将一条特定的指令送到指令寄存器中;在 Update—IR状态下,刚才输入到指令寄存器中的指令将用来更新指令寄存器。

最后,系统又回到Run—Test/Idle状态,指令生效,完成对指令 寄存器的访问。当系统又返回到Run—Test/Idle状态后,根据前面指令寄存器的内容选定所需要的数据寄存器,开始执行对数据寄存器的工作。

其基本 原理与指令寄存器的访问完全相同,依次为seIect—DR—Scan、Capture—DR、Shift—D、Exitl一DR、Update—DR, 最后回到Run-Tcst/Idle状态。通过TDl和TDO,就可以将新的数据加载到数据寄存器中。经过一个周期后,就可以捕获数据寄存器中的数据,完成对与数据寄存器的每个寄存器单元相连的芯片引脚的数据更新,也完成了对数据寄存器的访问。

5.SBW_JTAG

JTAG接口除了标准的4信号引脚外,TI还支持2信号引脚的SBW_JTAG。SBW_JTAG仅使用SBWTCK和SBWTDIO信号,常用于引脚受限芯片上。

4

I2C

1.名词解释

I2C总线全称Integrated Circuit,中文名I方C总线。

2. 历史由来

I2C 总线是由 Philips 公司开发的一种简单、双向二线制同步串行总线。

3.应用场景

I2C总线大量用于Host与外部设备的连接,简化了系统布线。I2C是双向二线制同步串行总线,每次可传输NByte数据,支持100kbps/400kbps/3.4Mbps/5Mbps速率。I2C总线包含两条信号线,串行数据SDA和串行时钟SCL。I2C的一个总线上可以挂在多个主机和多个设备,每次数据传输都是由主机发起,且由主机提供时钟。

4. 协议解析

I2C传输是以8bit为单元传输数据的,每个8bit单元数据后必须紧跟1bit回应数据。I2C的每笔传输包含四个阶段:

(1)开始信号(S):SCL为高电平时,SDA高电平向低电平跳变,开始传送数据。

(2)结束信号(P):SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

(3)响应信号(ACK):接收器在接收到8位数据后,在第9个时钟周期,拉低SDA。

(4)数据信号(DAT): 必须为8bit,传输时先传输最高位(MSB),之后必须紧跟着ACK信号。

此外,每笔传输的第一个8bit数据被用来作为,设备地址和访问类型。

写数据

若配置的方向传输位为“写数据”方向,即第一幅图的情况,广播完地址,接收到应答信号后,主机开始正式向从机传输数据(DATA),数据包的大小为8 位,主机每发送完一个字节数据,都要等待从机的应答信号(ACK),重复这个过程,可以向从机传输N 个数据,这个N 没有大小限制。当数据传输结束时,主机向从机发送一个停止传输信号(P),表示不再传输数据。

读数据

若配置的方向传输位为“读数据”方向,即第二幅图的情况,广播完地址,接收到应答信号后,从机开始向主机返回数据(DATA),数据包大小也为8 位,从机每发送完一个数据,都会等待主机的应答信号(ACK),重复这个过程,可以返回N 个数据,这个N 也没有大小限制。当主机希望停止接收数据时,就向从机返回一个非应答信号(NACK),则从机自动停止数据传输。

读和写数据

除了基本的读写,I2C 通讯更常用的是复合格式,即第三幅图的情况,该传输过程有两次起始信号(S)。一般在第一次传输中,主机通过 SLAVE_ADDRESS 寻找到从设备后,发送一段“数据”,这段数据通常用于表示从设备内部的寄存器或存储器地址(注意区分它与SLAVE_ADDRESS 的区别);在第二次的传输中,对该地址的内容进行读或写。也就是说,第一次通讯是告诉从机读写地址,第二次则是读写的实际内容。

以上通讯流程中包含的各个信号分解如下:

通讯的起始和停止信号

前文中提到的起始(S)和停止(P)信号是两种特殊的状态,见图 24-5。当 SCL 线是高电平时 SDA 线从高电平向低电平切换,这个情况表示通讯的起始。当 SCL 是高电平时 SDA线由低电平向高电平切换,表示通讯的停止。起始和停止信号一般由主机产生。

5

CAN

1.名词解释

CAN总线全称Controller Area Network,中文名控制器局域网络。

2.历史由来

CAN总线由以研发和生产汽车电子产品著称的德国BOSCH公司开发的,并最终成为国际标准(ISO 11898),是国际上应用最广泛的现场总线之一。

3.应用场景

CAN总线采用差分信号线CAN_L和CAN_H进行通信,最高支持1Mbps的通信速率。CAN总线采用多主控(Multi-Master)线性拓扑结构,加入网络节点的设备均可以向总线发送广播消息,其他设备通过ID过滤掉不感兴趣的消息。CAN总线按照帧为单位进行数据传输,数据帧支持1-8Byte数据传输。

4.协议解析

CAN总线基于多路载波侦听+基于消息优先级的冲突检测和非破坏性的仲裁机制,所有节点必须都等到总线处于空闲状态时才能往总线上发送消息,多个节点往总线上发送消息时具备最高优先级的消息获得总线。

通过ID仲裁,ID数值越小,报文优先级越高。

CAN总线通过过采样技术进行位同步,CAN控制器工作的最小时间单位(CAN时钟周期)称为时间份额,一个位包含多个CAN时钟周期。

为了实现位同步,CAN协议把每一位的时序分解成下图所示的四段。这四段的长度加起来即为一个CAN数据位的长度。一个完整的位由8-25个Tq组成。

当总线上出现帧起始信号(SOF,即隐性到显性的边沿)时,其他节点的控制器根据总线上的这个下降沿对自己的位时序进行调整,把该下降沿包含到SS段内。这样根据起始帧来进行的同步称为硬同步。因为硬同步时只是在有帧起始信号时起作用,无法确保后续一连串的位时序都是同步的,所以CAN引入了重新同步的方式。在检测到总线上的时序与节点使用的时序有相位差时(即总线上的跳变沿不在节点时序的SS段范围),通过延长PBS1段或缩短PBS2段来获得同步,这样的方式称为重新同步。

CAN一共规定了5中类型的帧,帧也称为报文。数据帧在CAN通信中最主要,也最复杂。数据帧以一个显性位(逻辑0)开始,以7个连续的隐性位(逻辑1)结束。CAN总线的数据帧有标准格式(Standard Format)和扩展格式(Extended Format)的区分。

-

常见硬盘接口技术分析2023-04-04 7944

-

语音接口技术浅析2022-11-01 719

-

微机接口技术实用教程2021-09-13 2023

-

人机交互接口技术简析2021-09-10 1571

-

谈谈微机原理与接口技术2021-07-28 1402

-

MAVLink学习之路05_ MAVLink应用编程接口分析2020-03-07 7708

-

基于IP核的SoC接口技术2019-06-11 1874

-

采用的IP核与系统的接口技术2019-05-27 2203

-

微机原理与接口技术2016-12-19 3891

-

高清晰视频会议终端应用接口分析2010-02-21 2549

-

WCDMA无线接口技术2009-09-18 6574

-

微机接口技术课件2009-06-12 8140

全部0条评论

快来发表一下你的评论吧 !