SDRAM芯片引脚说明和存储单元

存储技术

描述

SDRAM英文名是:Synchronous Dynamic Random Access Memory,即同步动态随机存储器,同步指存储器的工作需要参考时钟;

SDRAM的信号电平为LVTTL,属单端信号;

对于同步存储器,有三个与工作速率相关的重要指标:内核工作频率、时钟频率、数据传输速率;就SDRAM而言,其内核工作频率、时钟频率和数据传输速率三者相同;最高速率可达200MHz,设计中常用的速率有100 MHz、133 MHz、167 MHz;

下面以W9825G6KH为例,来对SDRAM进行介绍

一、SDRAM芯片引脚说明

CLK:时钟信号,在该时钟的上升沿采集输入信号;为输入信号;

CKE:时钟使能,高电平有效;禁止时钟时,SDRAM会进入自刷新模式;为输入信号;

CS#:片选信号,低电平有效;为输入信号;

RAS#:行地址选通信号,低电平时,表示行地址;为输入信号;

CAS#:列地址选通信号,低电平时,表示列地址;为输入信号;

WE#:写使能信号,低电平有效;为输入信号;

A0~A12:地址线(行/列);为输入信号;

BS0/BS1或BA0/BA1:BANK地址线;为输入信号;

DQ0~15:数据线;为输入/输出双向信号;

LDQM,UDQM:数据掩码,表示DQ的有效部分;为输入/输出双向信号,其方向与数据总线的方向相同,高电平有效;当DQM有效时,数据总线上出现的对应数据字节被接收端屏蔽;

举例说明:假设以 8 位数据访问,我们只需要 DQ0DQ7 的数据,而 DQ8DQ15的数据需要忽略;此时,我们只需要设置 LDQM 为低电平, UDQM 为高电平,就可以了;

VDD:SDRAM内核工作电源,为3.3V

VDDQ:SDRAM数据总线IO口电源,为3.3V

二、存储单元

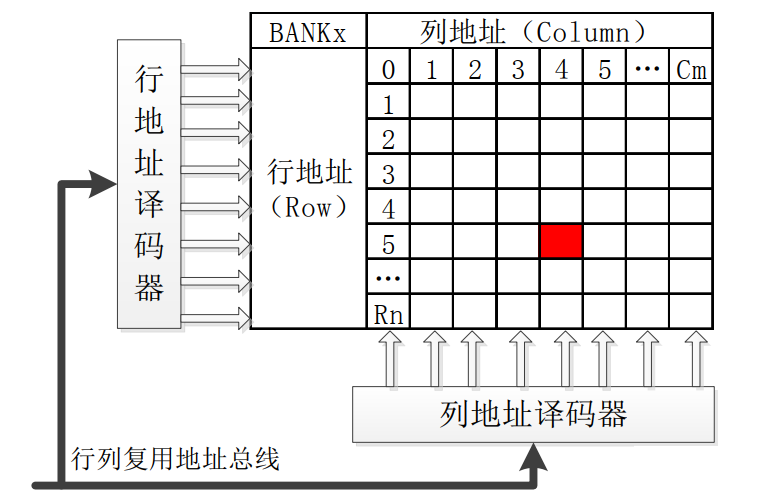

SDRAM的存储电源(称之为:BANK)是以阵列的形式排列,如图,每个存储单元的结构示意图

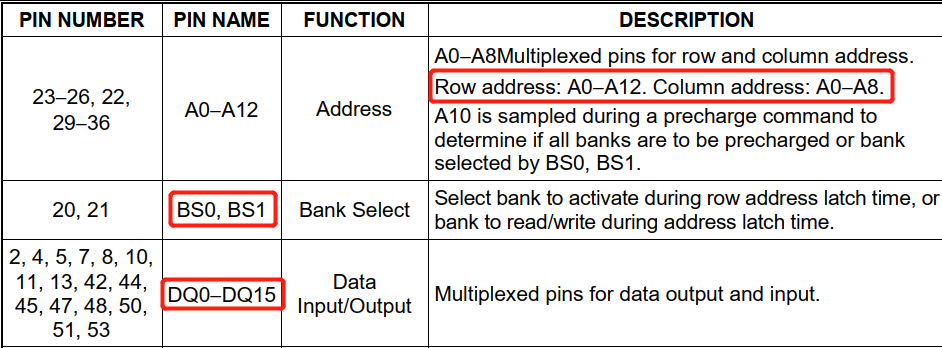

对于这个存储阵列,我们可以将其看成是一个表格,只需要给定行地址和列地址,就可以确定其唯一位置,这就是SDRAM寻址的基本原理,而一个SDRAM芯片内部,一般又有4个这样的存储单元(BANK),所以,在SDRAM内部寻址的时候,先指定BANK号和行地址,然后再指定列地址,就可以查找到目标地址;

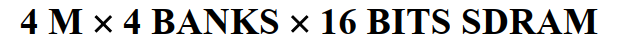

因此,在器件资料上,SDRAM存储容量的定义方式是:地址数х位宽х BANK;以W9825G6KH为例(容量为256Mb ):4Mх4BANK х 16bit

行地址信号线为A0~A12共13根,可组成2的十三次方不同的行地址,列地址信号线为A0 ~ A8共9根,可组成2的九次方不同的列地址,因此地址数为4M(2的二十二次方,注:1M为2的二十次方),BANK信号线为BS0/BS1或BA0/BA1共两根,因此BANK数为4;数据信号线为DQ0 ~15共16根,因此数据线宽为16bit

补充说明:行地址选择和列地址选择处于SDRAM操作的不同阶段,因此,行地址和列地址信号线可被相互复用;

下图为SDRAM存储结构图

-

存储单元是指什么2024-08-30 8114

-

常用存储单元的原理和特点2022-12-02 4197

-

存储位元与存储单元是什么含义2022-01-21 5931

-

主存中存储单元地址的分配2021-07-28 1856

-

存储单元结构2020-05-14 4521

-

DRAM上电时存储单元的内容是全0,而Flash上电时存储单元的内容是全1,对吗?2017-08-23 22708

-

高性能开关电流存储单元的设计及应用2010-07-05 897

-

熔丝型PROM的存储单元2009-12-04 2554

-

低电压甲乙类开关电流存储单元2007-08-15 746

全部0条评论

快来发表一下你的评论吧 !