SDRAM介绍

存储技术

描述

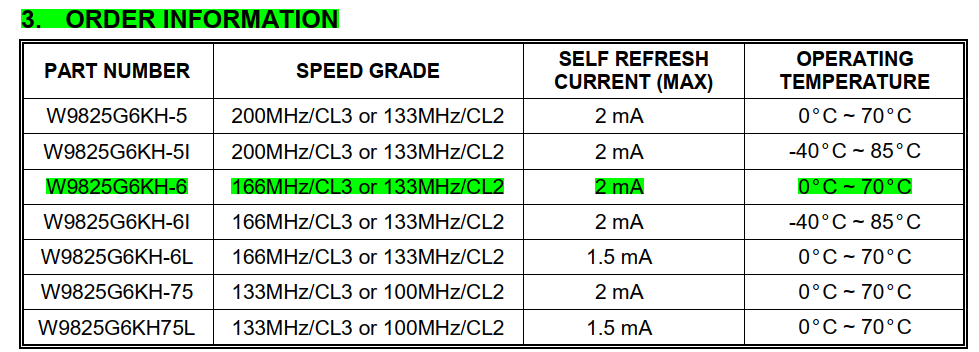

接下来看下W9825G6KH 规格书,挑选需要看的。

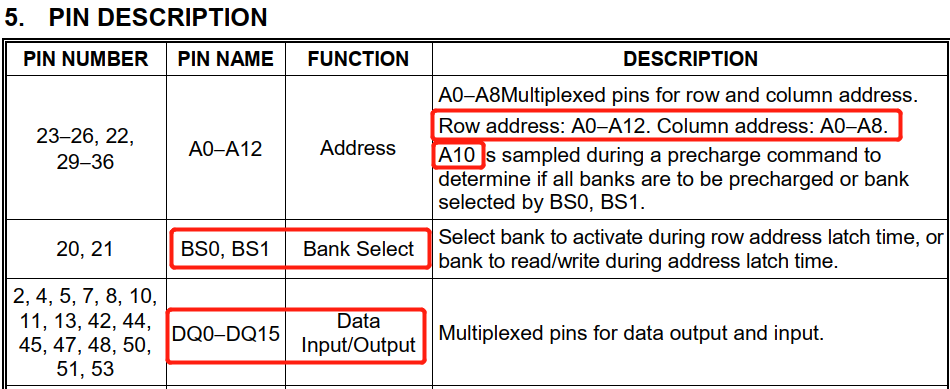

一、引脚说明:

行地址A0~A12,共13根线,可组成2的十三次方个不同的行地址;

列地址A0~A8,共9根线,可组成2的九次方个不同的列地址;

BANK线为:BS0、BS1,因此BANK为4;

数据线为DQ0~DQ15共16根,因此数据线宽为16位;

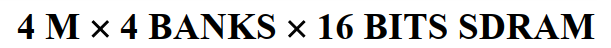

W9825G6KH的内存容量为:

A10:是用来设置自动预充电,当A10=1,使能所有BANK的预充电;

二、时间参数

2.1 CAS 延迟

就是前面说的CL,一般设置为2或3个时钟周期(在读命令发送完之后,需要等待几个时钟周期,DQ数据线上的数据才会有效,这个延迟时间叫CL)

2.2 SDCLK

W9825G6KH最快可达到200M(@CL=3)

注:时钟是MCU来决定的,STM32F429的SDRAM时钟为96MHz

2.3 BURST(突发操作)

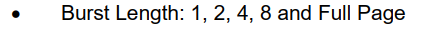

先解释下突发操作:在应用中,存储器的一次数据传输通常涉及多个字节,例如,某些CPU的存储接口数据总线为64位,则一次传输涉及8个字节数据,通常这8字节数据在存储器中处于相邻的位置,因此,采用BURST操作,可简化读写命令; BURST操作,即一次读写命令可传输同一行中若干连续的存储单元,一次传输字节的数量称为突发长度(BURST Length); 可设置以1、2、4、8或整页的突发长度

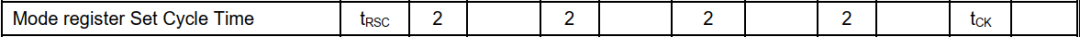

2.4 模式寄存器设置时间 tRSC

加载模式寄存器命令和激活或刷新命令之间的延迟,tRSC=2时钟周期

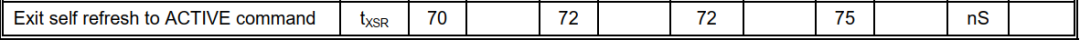

2.5 自刷新命令到激活命令之间的延迟 tXSR

器件要求为tXSR = 72ns

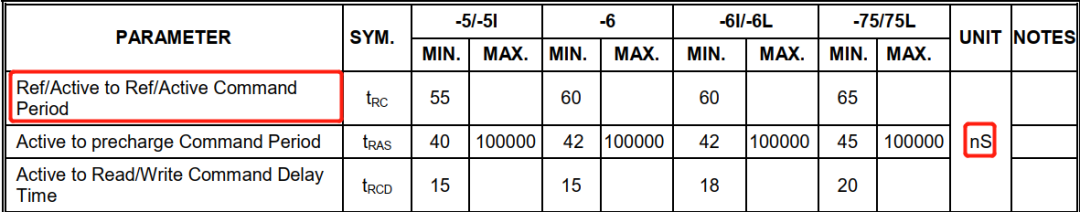

2.6 自刷新周期、刷新命令到激活命令之间的延迟tRC

器件要求tRC = 60ns

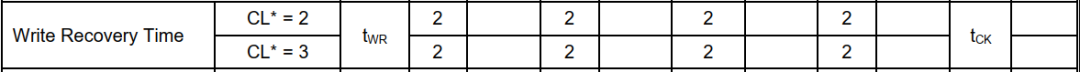

2.7 写命令和预充电命令之间的延迟tWR

器件要求tWR = 2个时钟周期

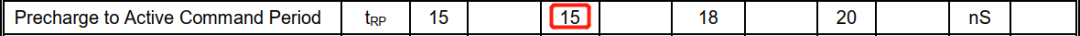

2.8 预充电命令与其他命令之间的延迟tRP

器件要求tRP = 15ns

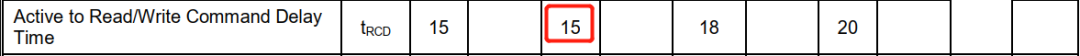

2.9 激活命令与读写命令之间的延迟tRCD

器件要求tRCD = 15ns

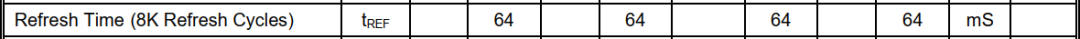

2.10 器件刷新时间tREF

器件的刷新tREF = 64ms,W9825G6KH 行数为 8192行(2的13次方),所以刷新速率为:64/8192=7.81us

三 、STM32F429与SDRAM接口

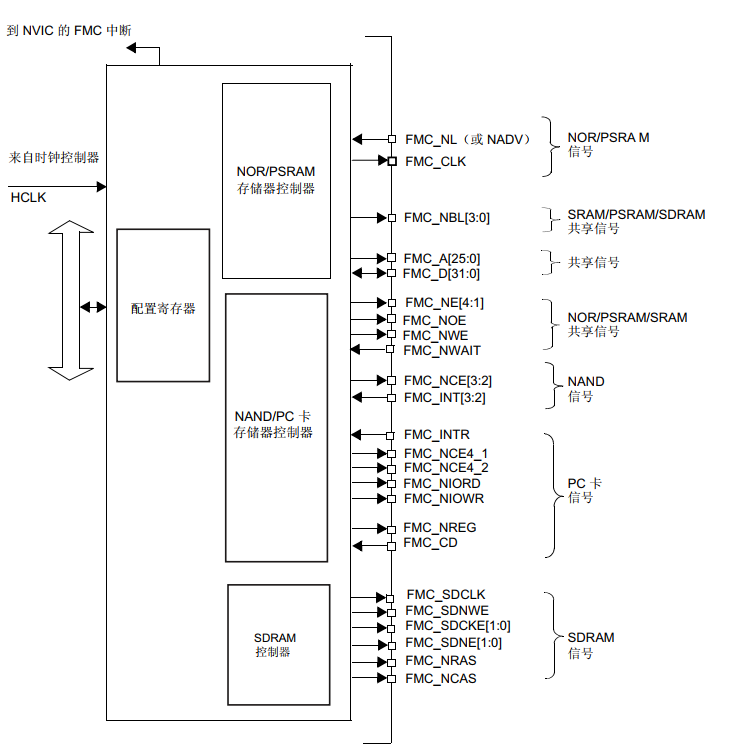

通过STM32F429的FMC接口驱动SDRAM; FMC(可变存储控制器)能够与同步或异步存储器、SDRAM存储器和16位PC存储器卡连接; FMC框图如下:

由于是驱动SDRAM,重点看下SDRAM控制器

SDRAM控制器的主要特定如下:

(1)两个 SDRAM 存储区域,可独立配置;

(2)8 位、 16 位和 32 位数据总线宽度;

(3)13 位地址行, 11 位地址列, 4 个内部存储区域:4x16Mx32bit (256 MB)、 4x16Mx16bit(128 MB)、 4x16Mx8bit (64 MB)

(4)支持字、半字和字节访问

(5)SDRAM 时钟可以是 HCLK/2 或 HCLK/3

(6) 自动进行行和存储区域边界管理

(7)多存储区域乒乓访问

(8)可编程时序参数

(9)支持自动刷新操作,可编程刷新速率

(10)自刷新模式

(11)掉电模式

(12)通过软件进行 SDRAM 上电初始化

(13)CAS 延迟 1,2,3

(14)读 FIFO 可缓存,支持 6 行 x 32 位深度( 6 x14 位地址标记)

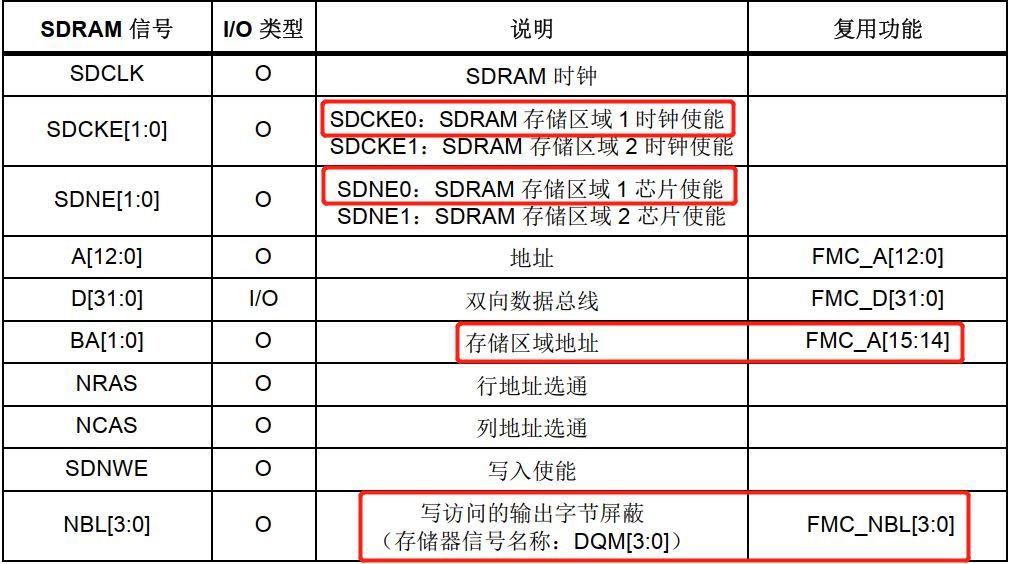

与SDRAM 驱动 IO接口如下:

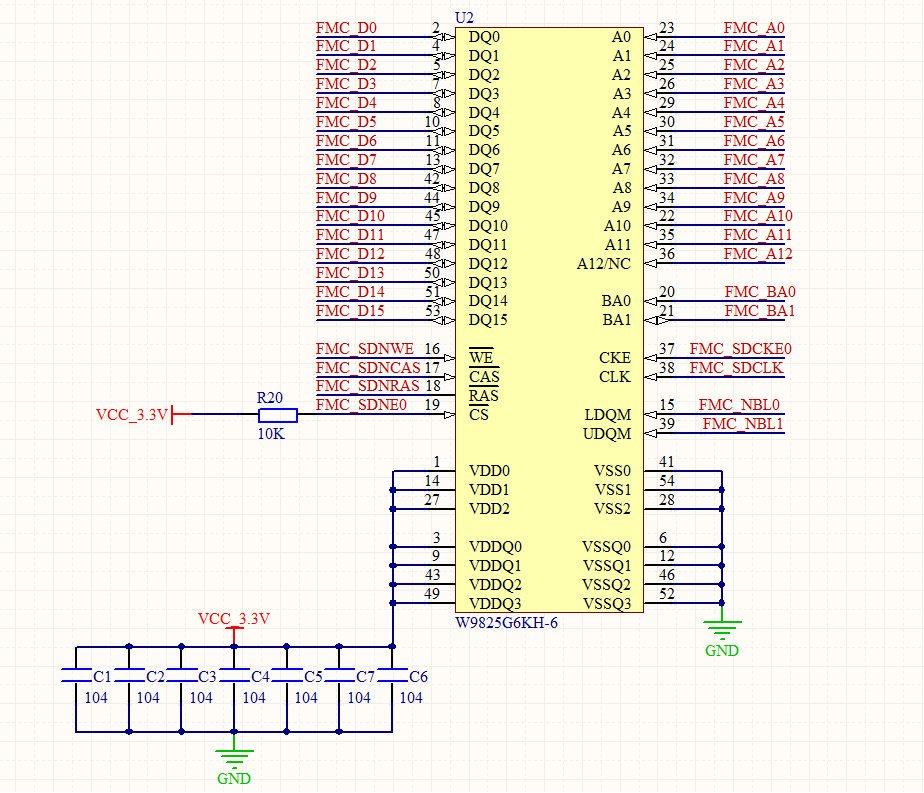

电路图如下:

-

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文2018-12-25 1741

-

SDRAM的介绍及设计应用2009-11-13 5801

-

电力监控行业常用SDRAM介绍2014-07-16 5129

-

FPGA应用案例:实现 DSP 到 SDRAM 的数据存取2020-04-23 3098

-

求大佬详细介绍一下DRAM、SDRAM及DDR SDRAM的概念2021-04-20 2744

-

关于s3c2440中存储控制器操作SDRAM的介绍2022-05-07 3604

-

ARM里的ram和SDRAM有什么区别2022-10-25 1923

-

DDR SDRAM技术总结2010-08-30 864

-

DDR_SDRAM介绍以及时序图2016-02-23 1132

-

DRAM、SDRAM及DDR SDRAM之间的概念详解2018-06-07 95256

-

关于SDRAM电路的设计2018-06-11 4505

-

一文看懂ARM里的RAM和SDRAM有什么区别2018-04-27 35052

-

RAM和SDRAM介绍及有什么区别2018-05-09 12632

-

AT32讲堂039 | AT32 MCU SDRAM控制器的使用2022-12-19 3986

-

同步DRAM(SDRAM)介绍2024-07-29 2289

全部0条评论

快来发表一下你的评论吧 !