求一种基于AMD器件的EtherCAT从站方案

描述

EtherCAT现场总线协议是由德国倍福公司在2003年提出的,该通讯协议拓扑结构十分灵活,数据传输速度快,同步特性好,可以形成各种网络拓扑结构。

1、EtherCAT简介

EtherCAT是一个开放架构,以以太网为基础的现场总线系统,其名称的CAT为控制自动化技术(Control Automation Technology)字首的缩写。EtherCAT是确定性的工业以太网,最早是由德国的Beckhoff公司研发。

EtherCAT主站可以用软件,在标准的以太网媒体接入控制器中实现。许多供应商有提供在不同操作系统下的代码,也有许多开源软件或共享软件。

EtherCAT从站需要特殊的EtherCAT从站控制器,才能实现飞速传输(processing on the fly)的技术。EtherCAT从站控制器可以用FPGA来实现,且已有现成的代码,此控制器也可以用ASIC来实现。

2、EtherCAT特性

A. 完全符合以太网标准:

EtherCAT是对传统的以太网协议进行修改,因此可以与其他以太网协议并存于统一总线。EtherCAT网络中也可以使用普通的以太网设备,例如以太网线、以太网卡、交换机、路由器等设备。此外,任何具有标准以太网控制器的设备都可以作为EtherCAT 主站,包括PC计算机、带有以太网控制器的嵌入式设备。

B. 卓越的性能:

EtherCAT是基于以太网技术,数据传输速度可以达到100Mbit/s,是最快的工业以太网技术。EtherCAT最大利用以太网带宽进行数据传输,有效数据利用率高,可达90%以上。另外EtherCAT数据帧处理的实时性很高,数据刷新周期小于100us,满足对实时性要求高的场合。EtherCAT使用高精度的分布式时钟,能保证各个从站节点设备的同步精度小于1us。

C. 简单、低成本:

EtherCAT结构简单,而无需交换机或集线器,复杂功能的节点设备或简单的I/O节点都可以用作EtherCAT从站。此外EtherCAT在网络拓扑方面没有限制,支持多种网络拓扑结构,如线型、星型、树型拓扑结构,以及各种拓扑结构的组合,从而使得设备连接非常灵活。

3、BECKHOFFESC IP Core For AMD FPGAs Release 3.00

概述:

BECKHOFFEtherCAT IP核是一个可配置的EtherCAT从控制器(ESC)。它负责EtherCAT通信,作为EtherCAT现场总线和应用程序之间的接口。

A、EtherCATIP核是作为一个可配置的IP,各项功能可以自定义;

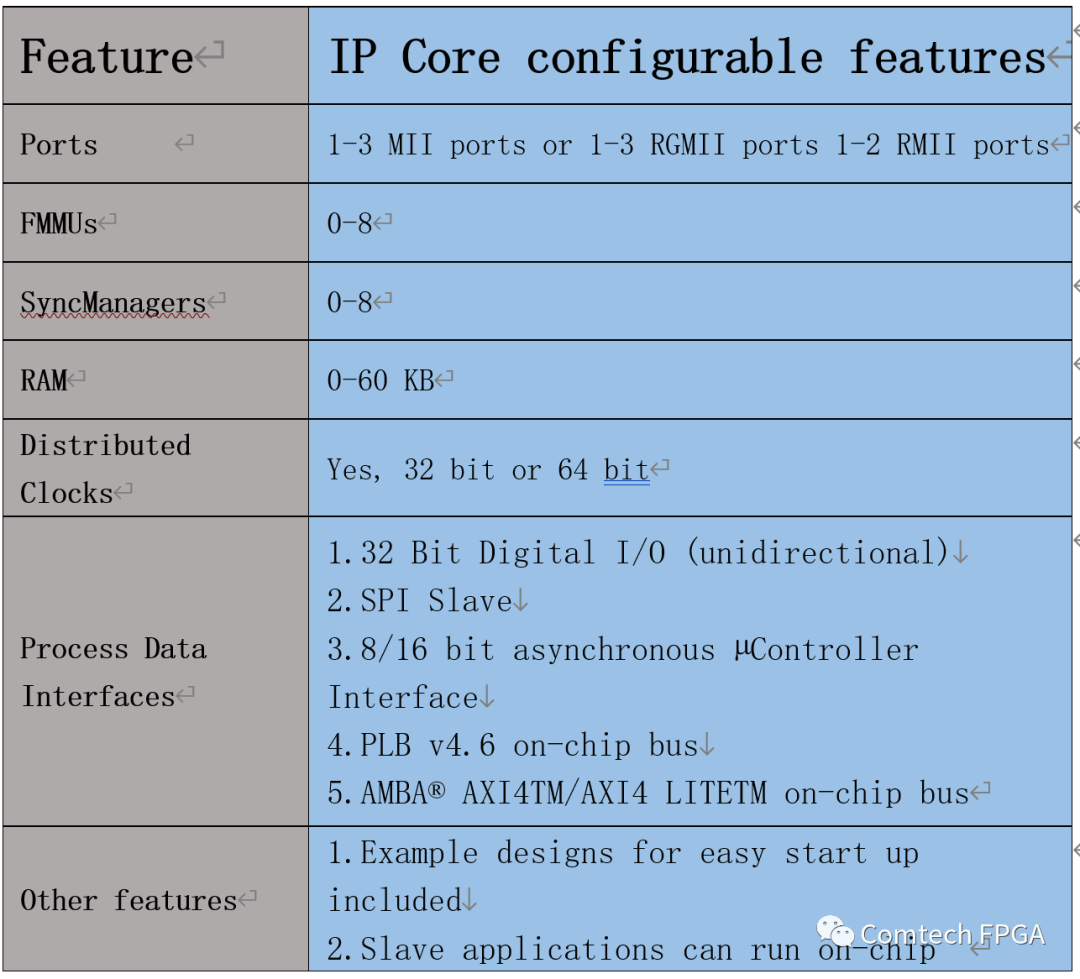

BECKHOFFIP Core Main Features : Table 1

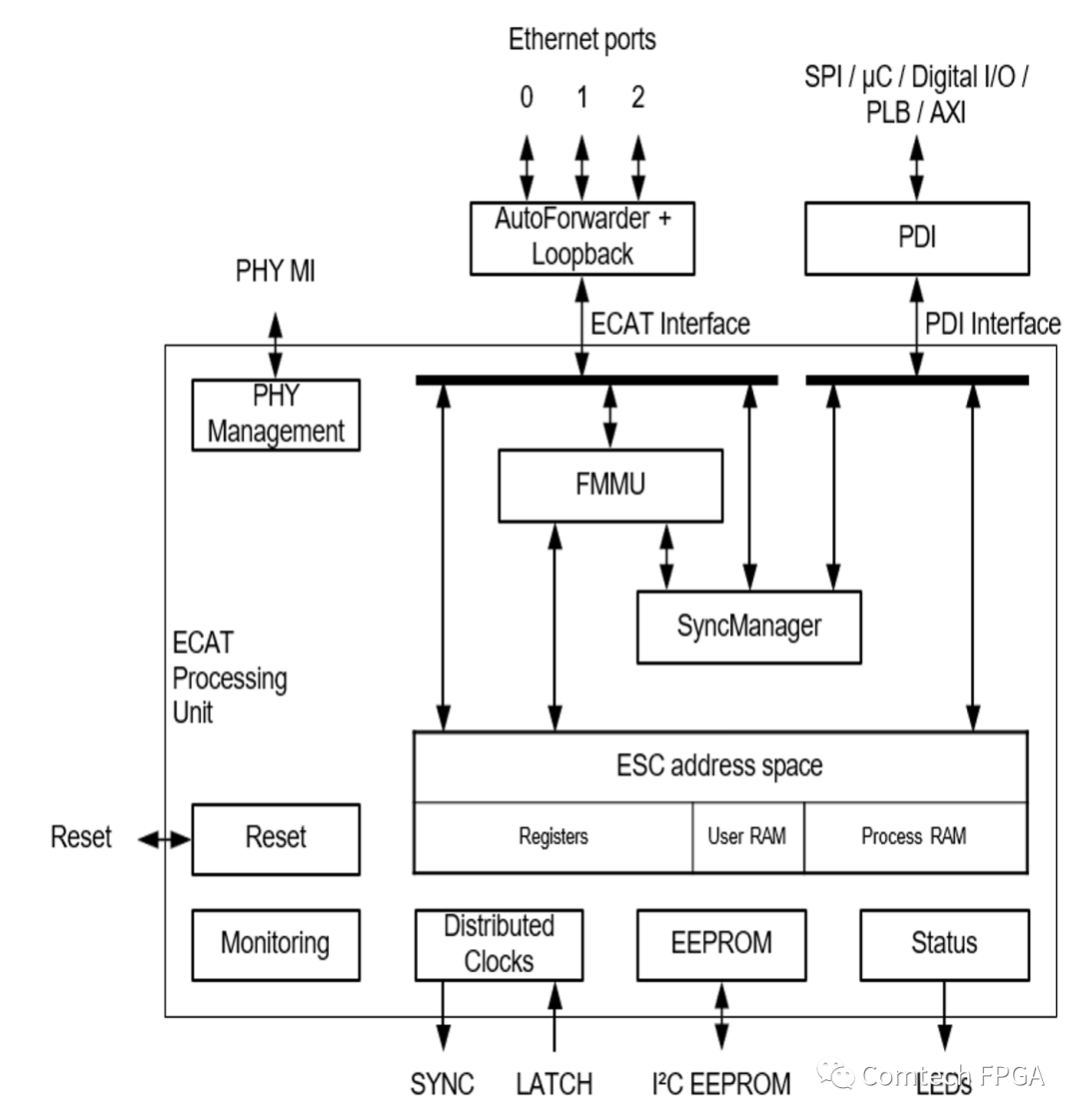

B、 EtherCATIP Core Block Diagram;

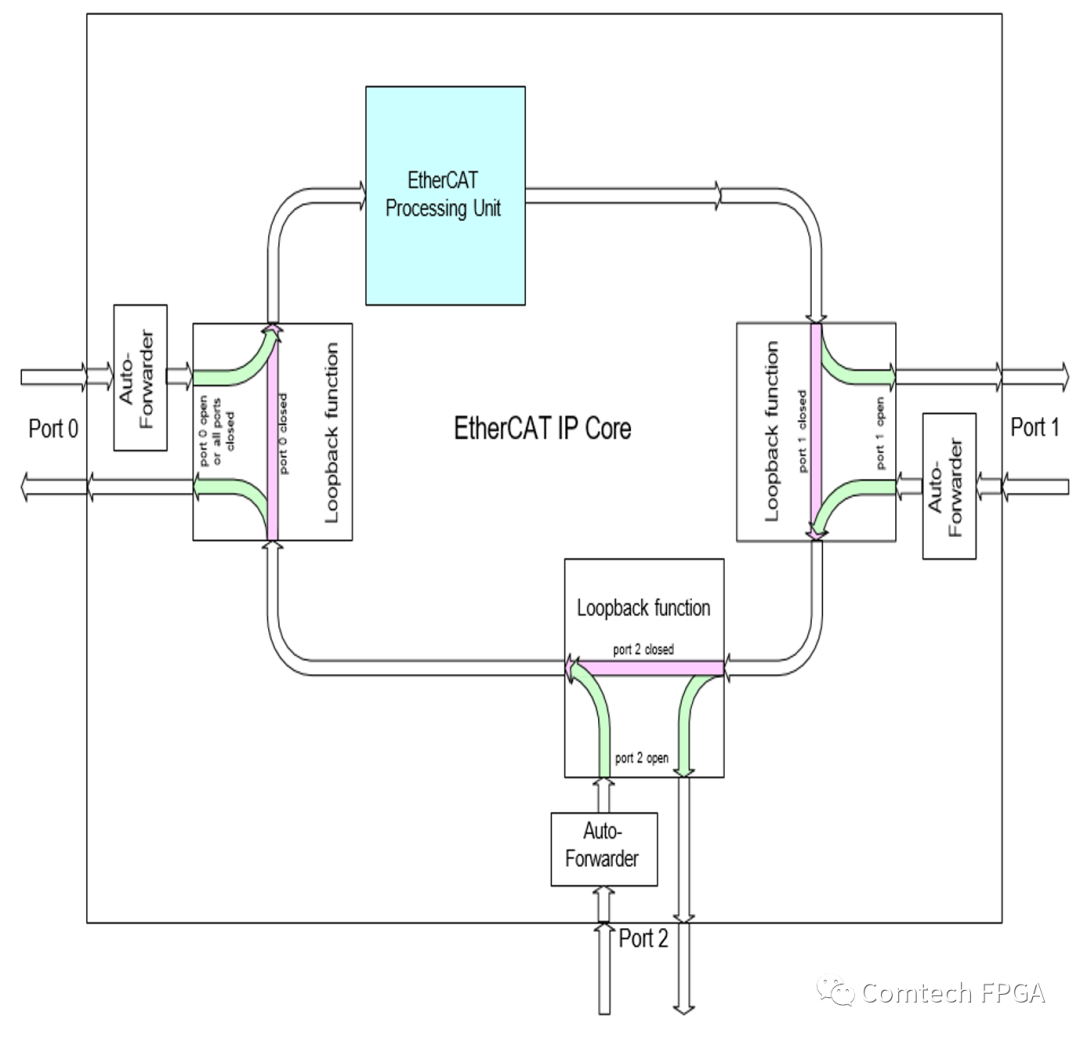

C、端口数据处理顺序;

a、0→EtherCAT Processing Unit→1 / 1→2 / 2→0

b、0→EtherCATProcessing Unit→0

c、0→EtherCATProcessing Unit→1 / 1→0

4、BECKHOFFESC IP使用流程:

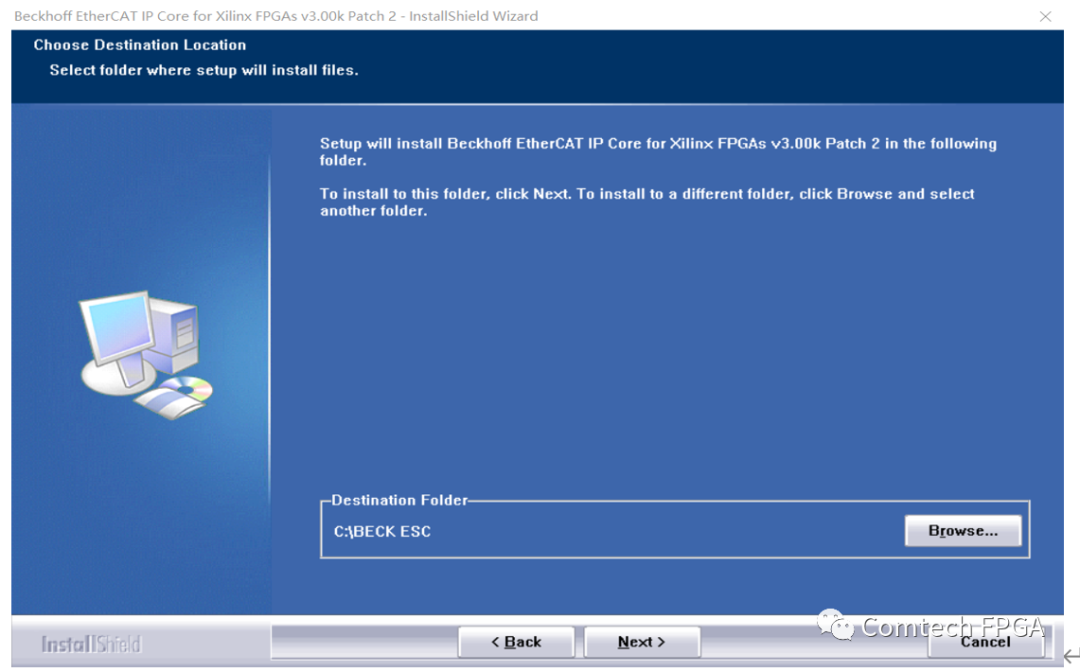

A. 直接安装,英文目录;

ISE14.3 - 14.7

B. 安装过程中提示要加入VENDER ID ,直接跳过 ,需要申请License才能综合;

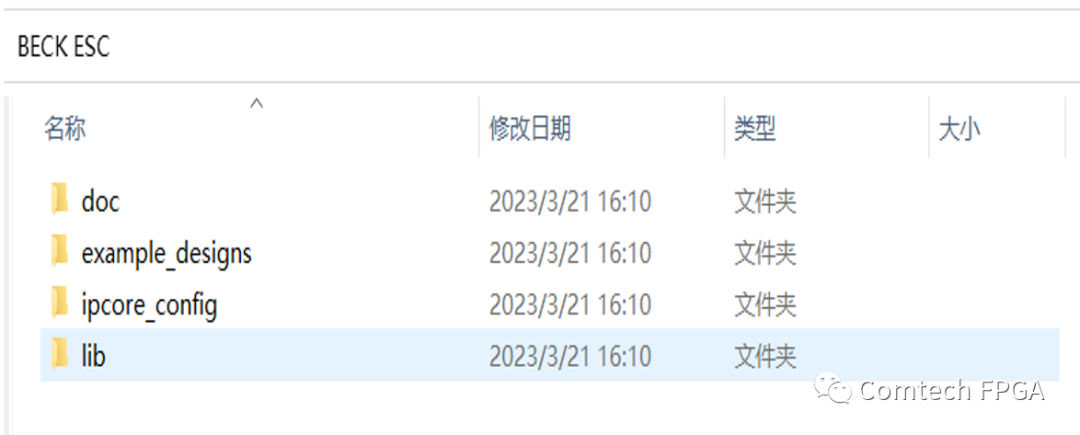

C. 安装完目录截图如下;

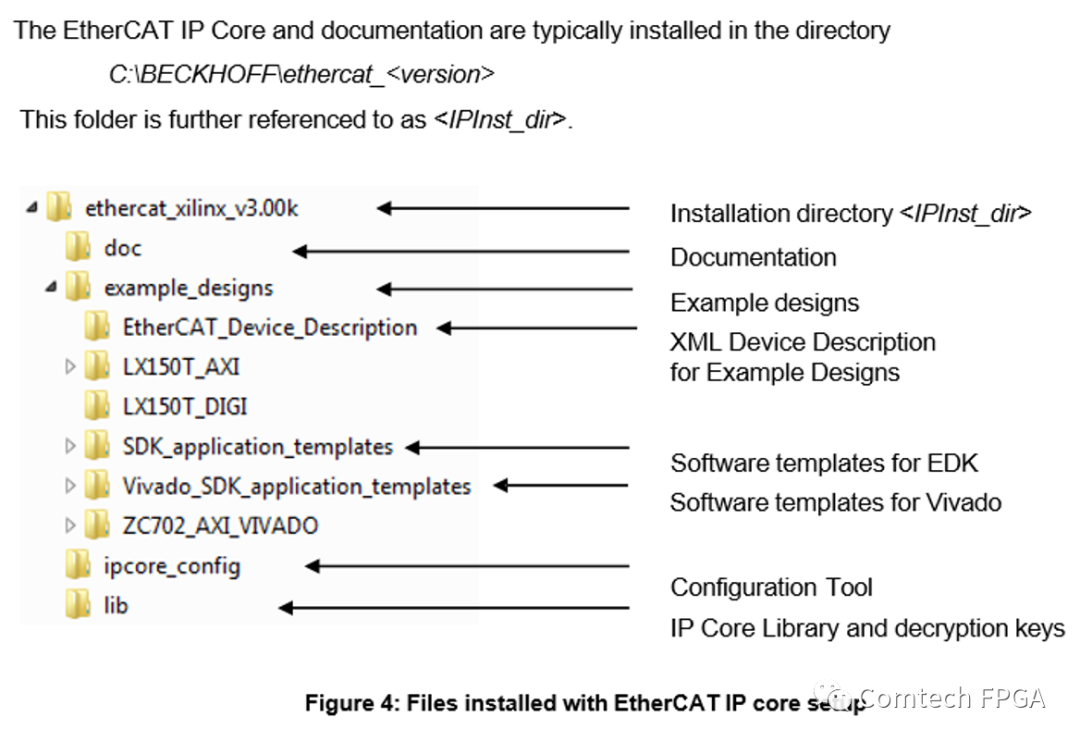

D. 安装完后,文件截图以下;

EtherCATIP Core (encrypted VHDL library)

Decryptionkeys for encrypted EtherCAT IP Core

IPCore Configuration Tool (IPCore_Config.exe)

Exampledesigns

E. 支持的AMD 器件包括SOC器件和纯FPGA器件;

F. 支持的软件版本:

Vivado2013.1 - 2013.4, 2014.1 - 2019.3

SDK

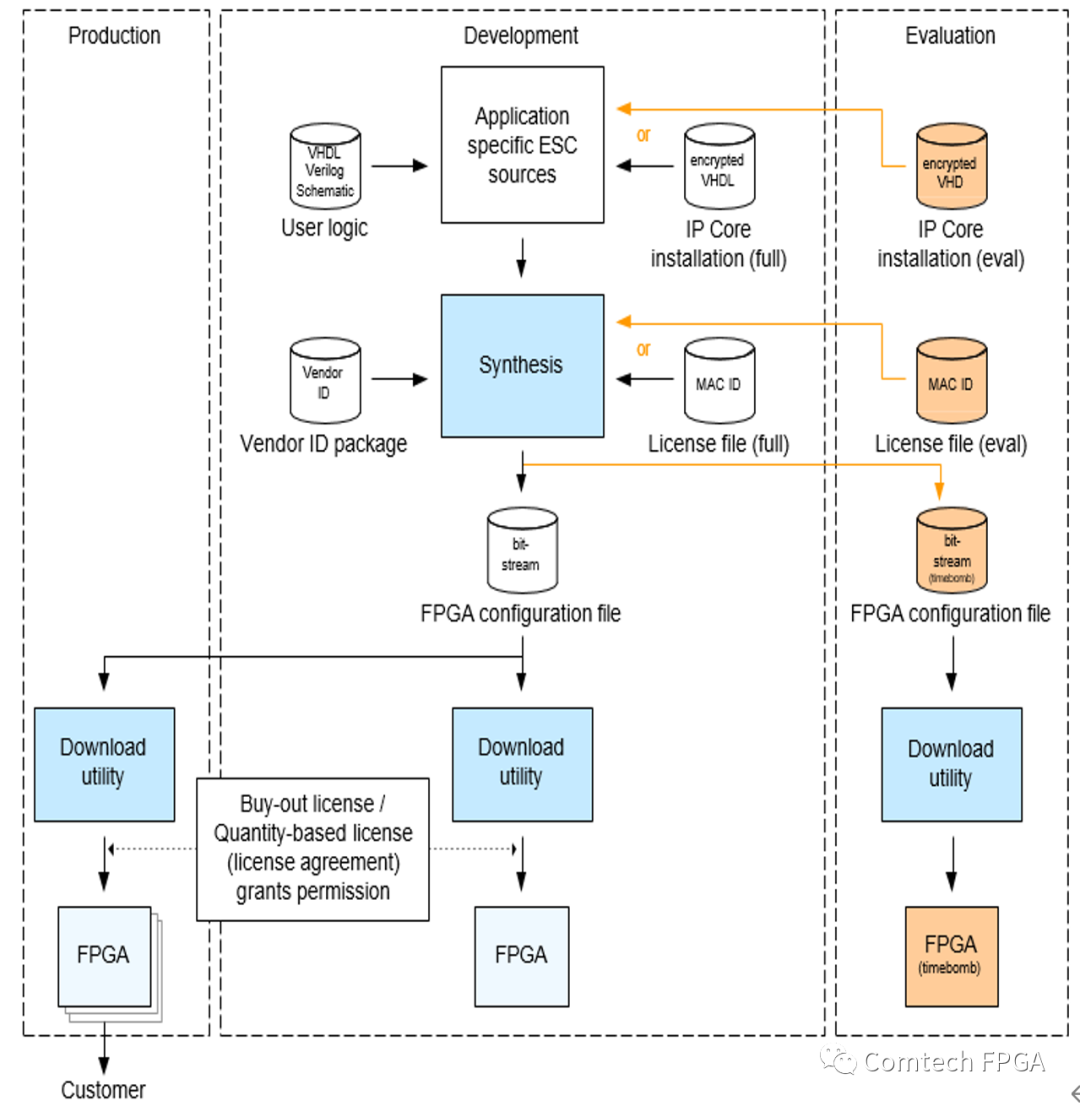

5、设计流程图:

6、详细过程如下:

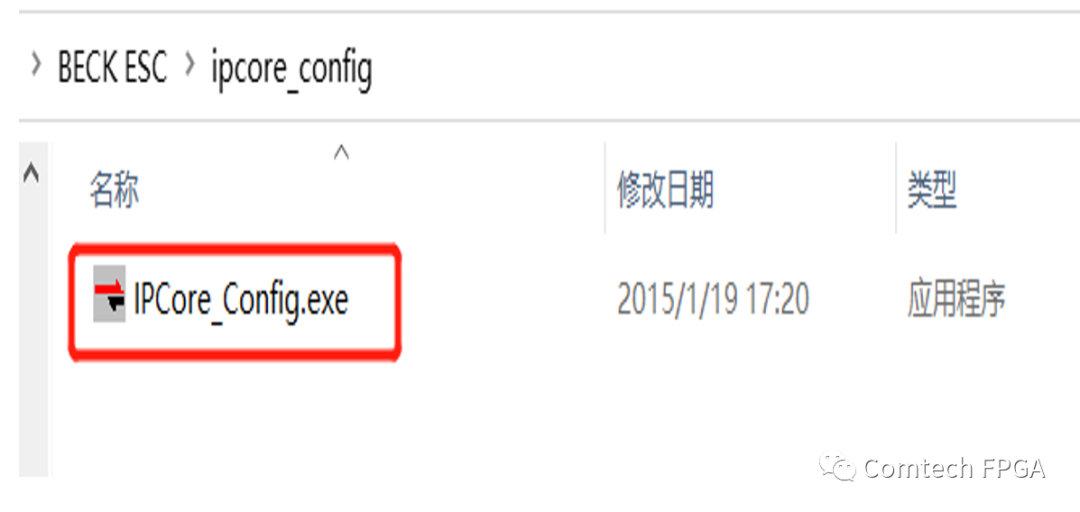

A. 双击Ipcore_config目录下的IPCore_Config.exe;

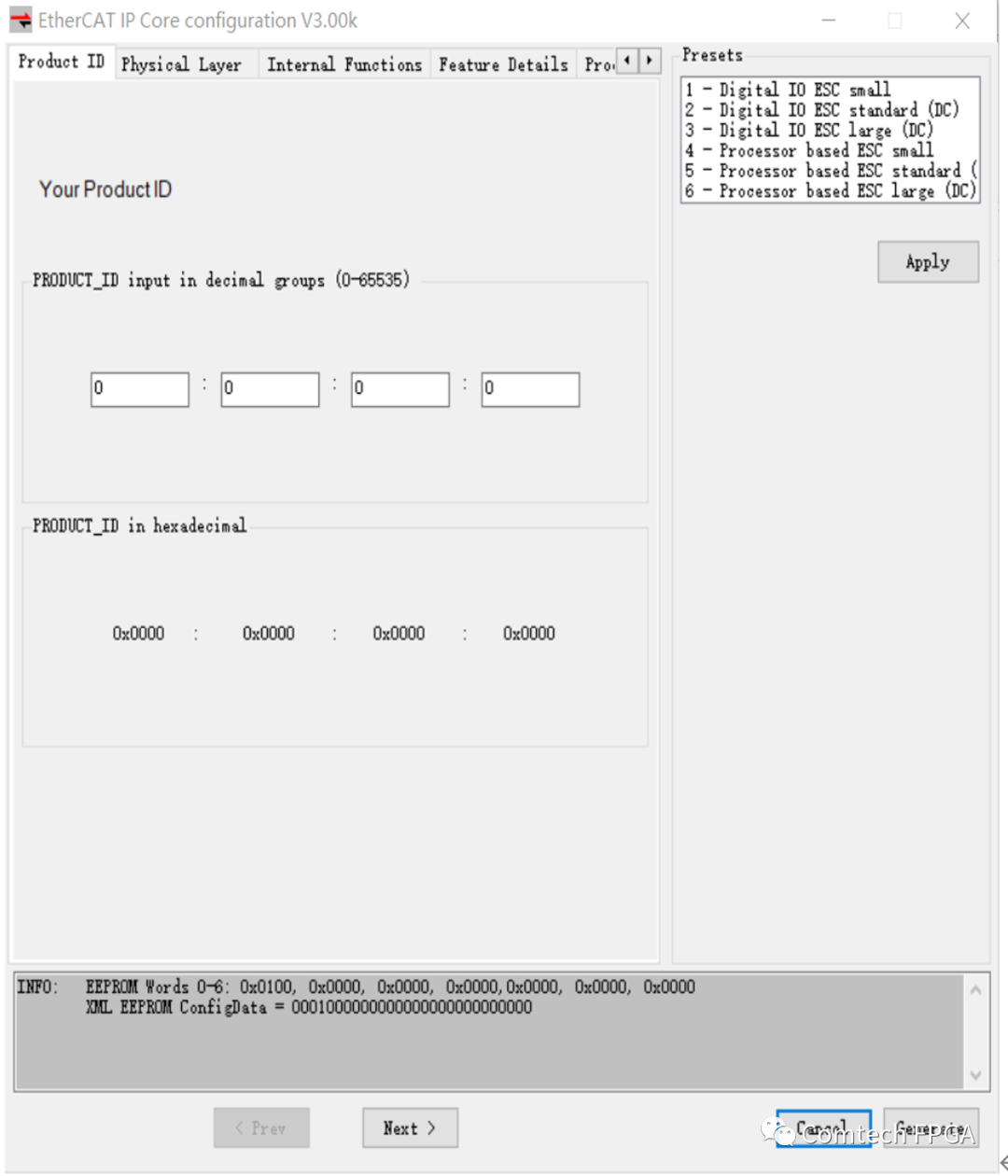

B. 填写Porduct ID;

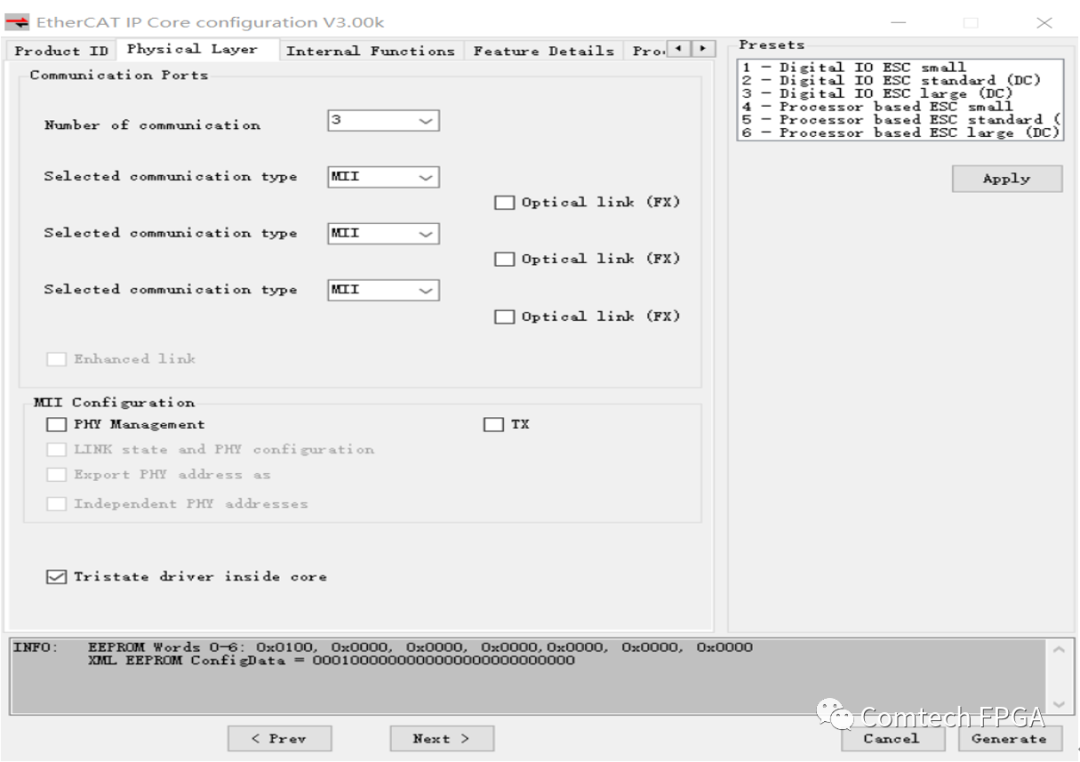

C. 物理层的一些配置:例如几路端口,PHY的接口类型,MII/RGMII/RMII,由客户的PHY芯片决定;

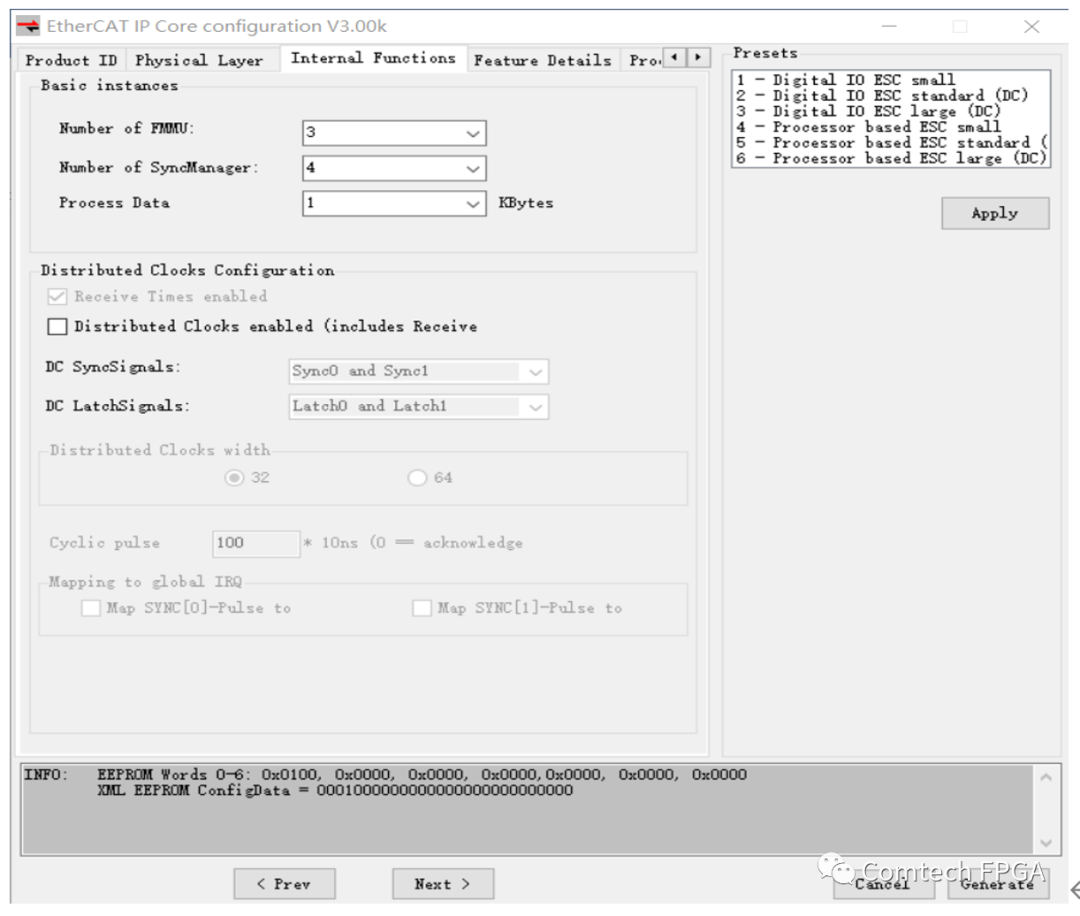

D. 网络功能的配置;

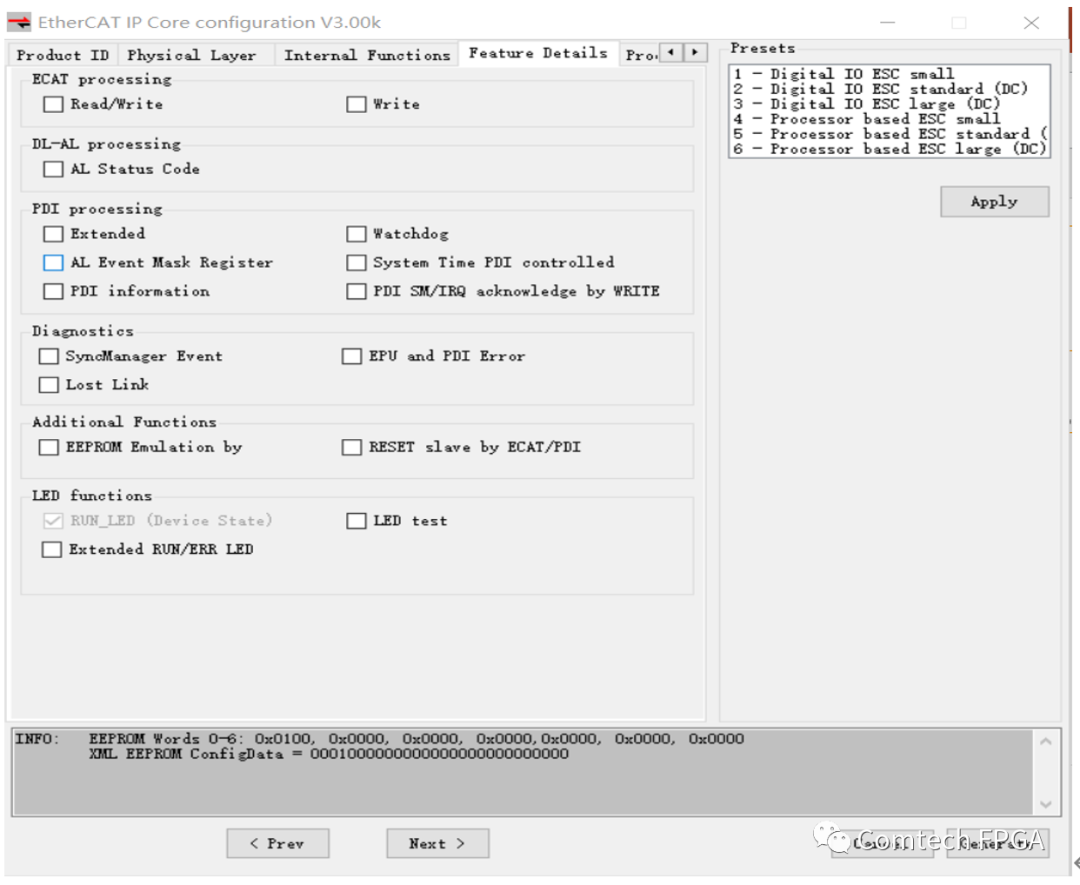

E. ECATProcessing /PDI Processing/LED status;

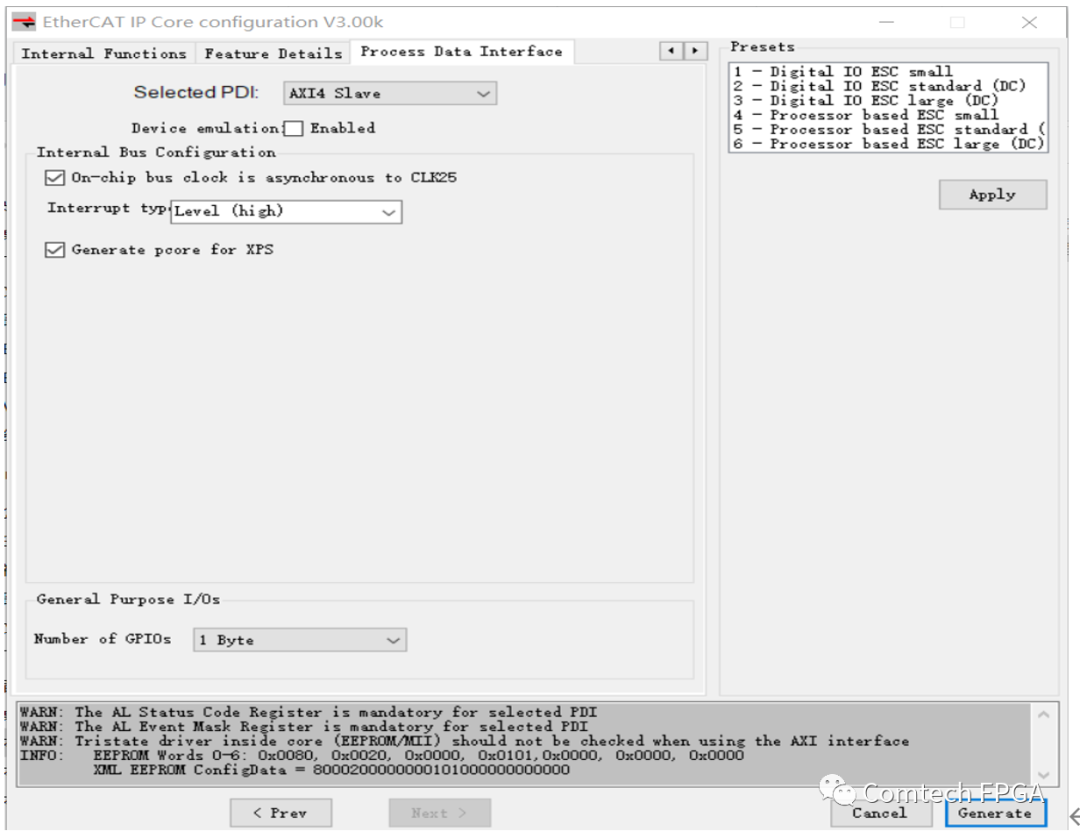

F. ESC跟CPU的接口;

G. 最后一步Generate;

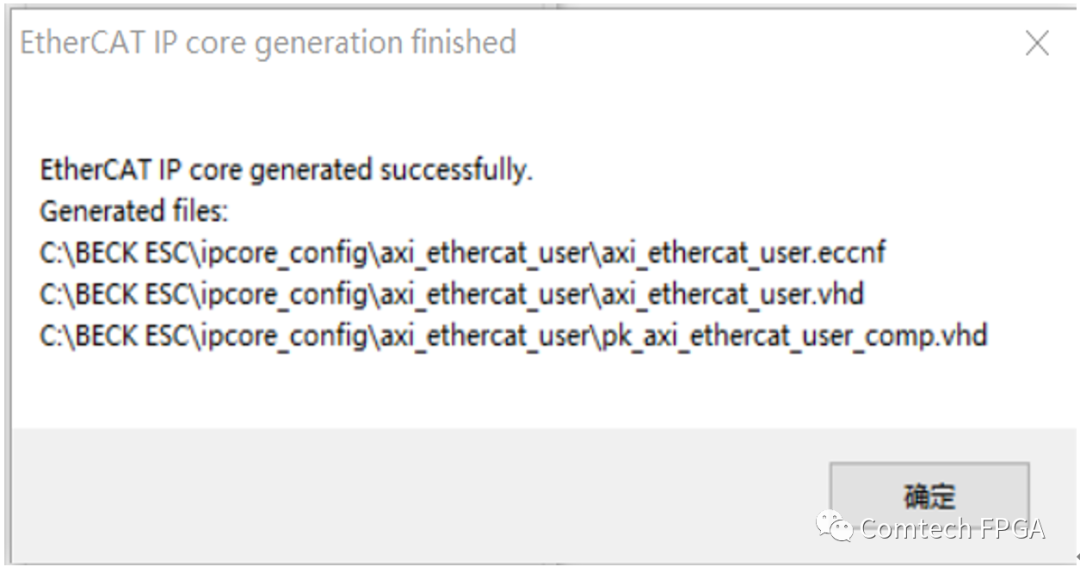

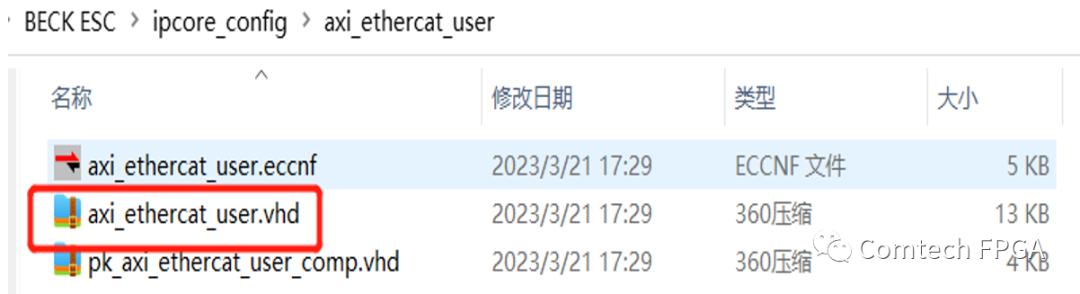

H. 生成的文件如下,不同的配置生成的文件有差异;

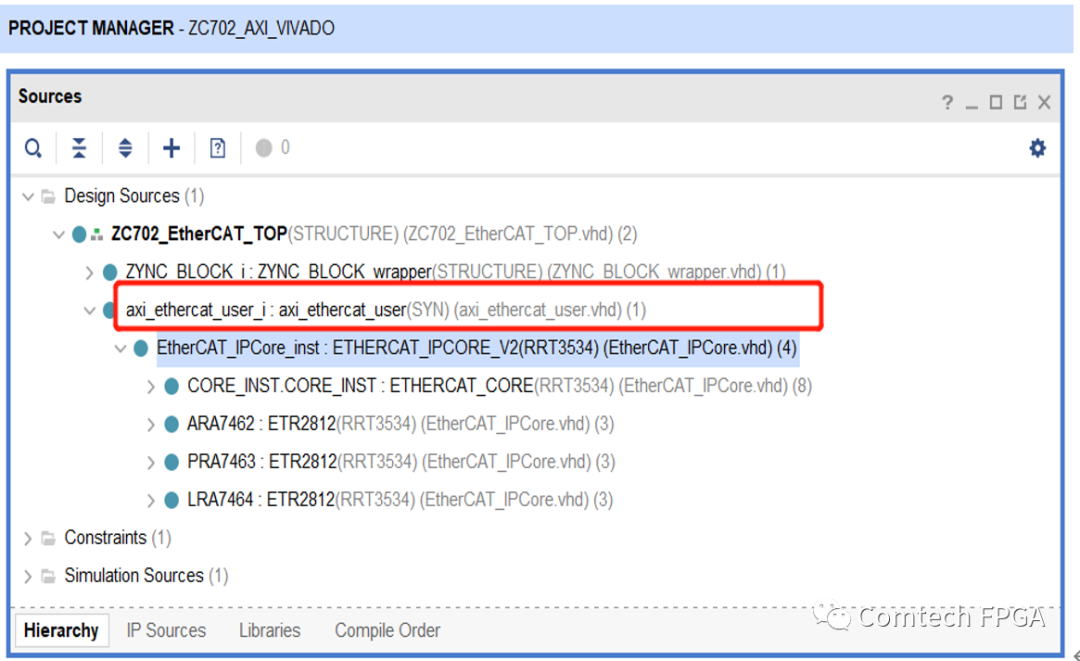

J. 把生成的文件加入到工程中,截图如下;

K. 导入License,如果没有授权的License,无法综合;

I. 综合、实现后生成BitStream并将其下载到FPGA。使用EtherCAT主机与EtherCAT从机通信;

J. EtherCAT从站需要SII EEPROM(或其他非易失性存储器),其中包含用于设备识别的EtherCAT从站信息(ESI);

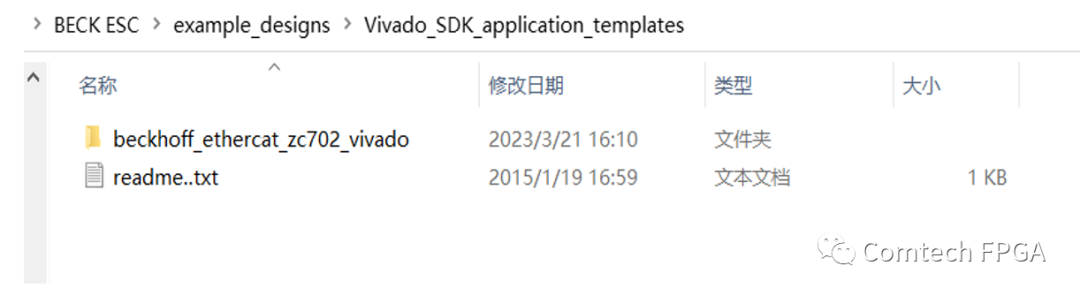

M. 打开SDK,添加应用文件,细节参考readme.txt;

N. 注意事项:

ESCIP 和 PHY 不能一起复位,IP核复位后,再让PHY复位。

ESC in resetstate → PHY disabled

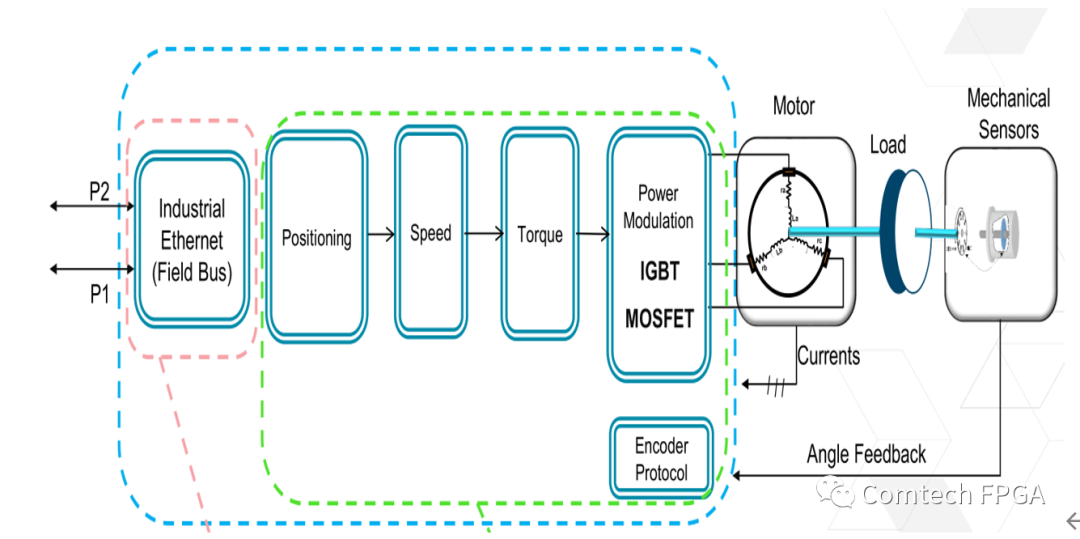

7、工业控制系统产品架构图:

8、AMD推荐方案:

ZYNQ7000 SOC器件+Ethernet PHY(2x100Base-T)

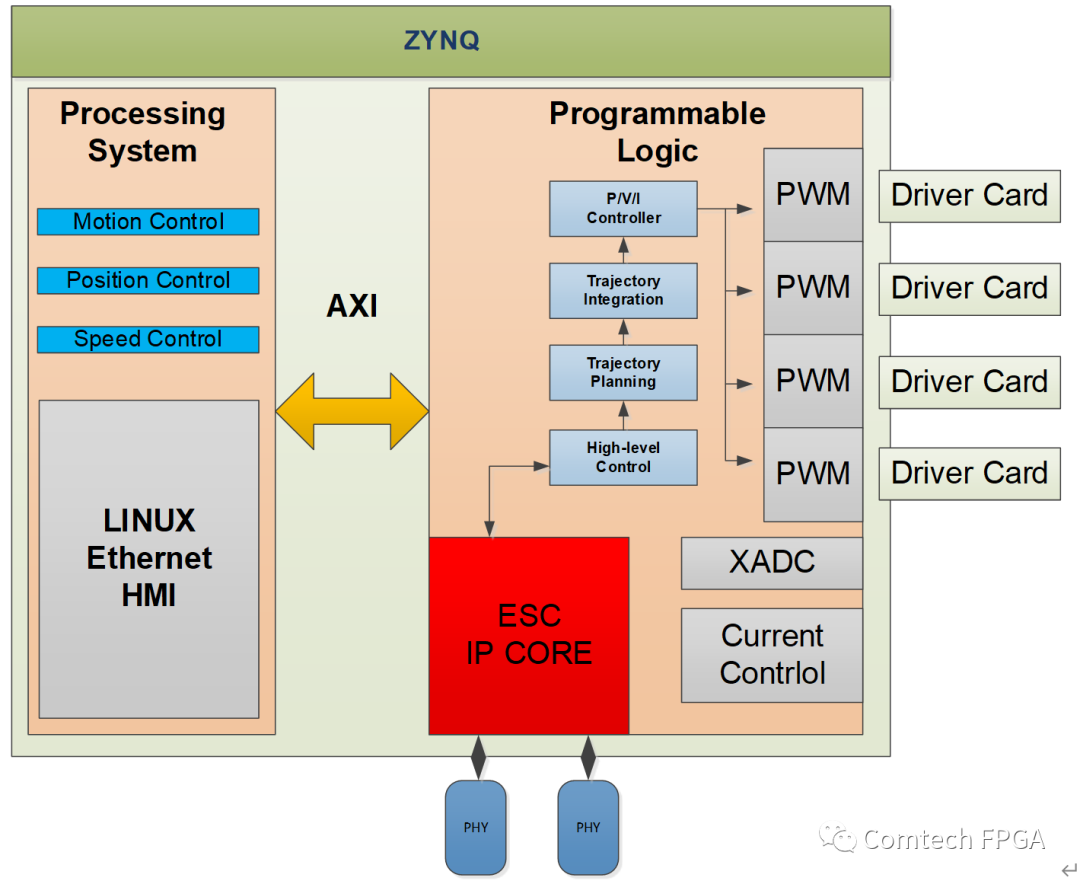

9、基于ZYNQ的ESC方案框图:

10、AMD ZYNQ 优势:

A. PS端:ARM Cortex-A9 766MHZ,可实现超强的性能及复杂的应用;

B. PL端:EtherCATSLAVE Controller IP容易布署,消耗相应的逻辑资源;

C. BECKOFFEtherCAT SLAVE Controller IP 应用广,经过市场验证,性能稳定;

D. BECKOFFEtherCAT SLAVE Controller IP 在AMD多个平台上进行过优化,量身定 制。同等功能,相比于其它厂商的平台,消耗资源少5%-10%。

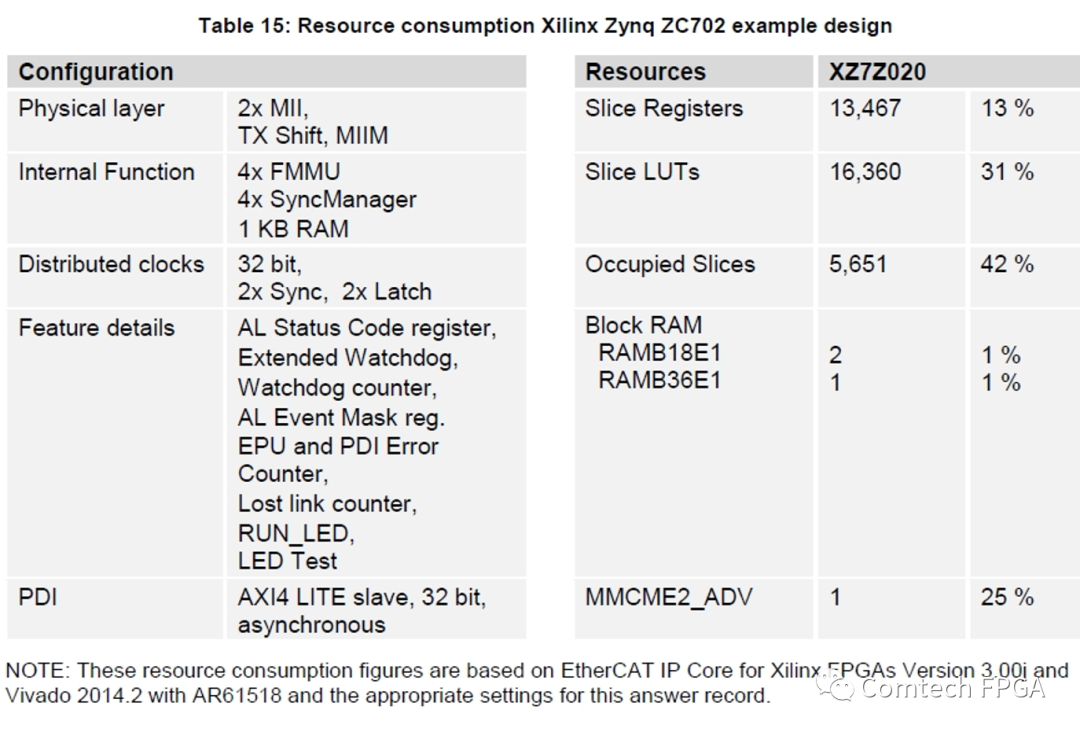

11、EtherCAT Resource :

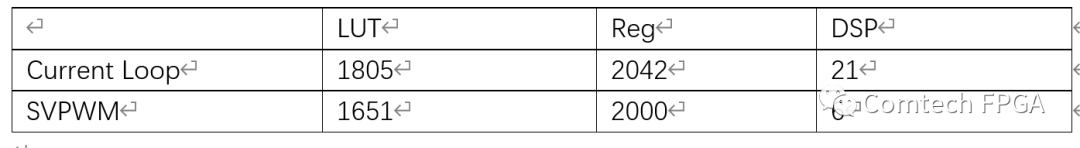

12、一路电流环+SVPWM:

审核编辑:刘清

- 相关推荐

- 热点推荐

- FPGA

- 控制器

- 以太网

- EtherCAT总线

- AMD芯片

-

【NUCLEO-F412ZG申请】EtherCAT从站设计2016-11-07 2729

-

【MYS-6ULX-IOT试用申请】基于I.MX 6UL的EtherCAT从站的设计2017-06-02 6568

-

完全自主Ethercat从站-FPGA实现2017-08-22 9504

-

亚信将于2018 TAIROS展出全新2/3端口EtherCAT从站控制器2018-08-21 2943

-

亚信电子展出全新AX58100 EtherCAT从站控制器2018-09-06 7451

-

无DDR的EtherCAT从站参考设计包括BOM及框图2018-10-16 2928

-

【亚信电子】AX58200 EtherCAT从站马达控制开发套件环境架设演示2020-04-20 2171

-

亚信 AX58100 EtherCAT从站设备仿真功能设计教学2021-02-08 4831

-

开源!ZYNQ IgH EtherCAT主站方案分享2021-10-29 5694

-

【新产品发布】亚信电子推出最新EtherCAT从站双核微控制器解决方案2021-11-24 1112

-

用于C2000™微控制器的EtherCAT从站堆栈解决方案2022-11-09 950

-

基于AMD器件的EtherCAT从站方案2023-04-08 2099

-

EtherCAT转Modbus网关的 EtherCAT从站配置案例2023-11-16 1494

-

EtherCAT总线如何对从站固件进行升级?2024-02-27 2403

-

如何让EtherCAT从站间自由“对话”?2025-09-09 1176

全部0条评论

快来发表一下你的评论吧 !