如何使用高速和高电流栅极驱动器实现更高的系统效率

描述

我们生活在一个设计师似乎不断追求更高效率的世界里。我们希望用更少的功率输出更多的电源!更高的系统效率需要团队努力,包括(但不限于)性能更好的栅极驱动器、控制器和新的宽带隙技术。

具体而言,大电流栅极驱动器可以通过最小化开关损耗来帮助提高整体系统效率。当 FET 打开或打开和关闭时,会发生开关损耗。要打开FET,栅极电容必须充电超过阈值电压。栅极驱动器的驱动电流有利于栅极电容的充电。驱动电流能力越高,电容充电或放电的速度就越快。能够源出和吸收大量电荷可最大限度地减少功率损耗和失真。(传导损耗是FET中其他类型的开关损耗。传导损耗由内阻或RDS(开启),其中 FET 的 .FET随着电流的传导而耗散功率。

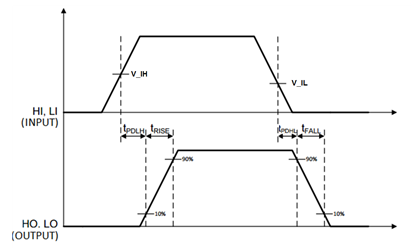

换句话说,目标是最大限度地减少需要高频功率转换的系统中的开关转换时间段。突出此类性能的栅极驱动器规格是上升和下降组合时间。参见图1。

图 1:典型上升和下降时间图

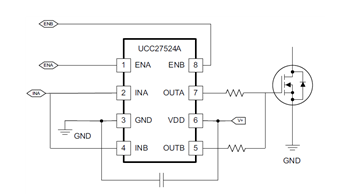

如果你想更上一层楼,延迟匹配等栅极驱动器特性可以有效地使驱动电流能力翻倍。延迟匹配是两个通道之间内部传播延迟的匹配。这是通过并联双通道栅极驱动器的输出或将通道连接在一起来实现的。例如,TI 的 UCC27524A 具有极其精确的 1ns(典型值)延迟匹配,可将驱动电流从 5A 增加到 10A。

图 2 显示了 UCC27524A 的 A 和 B 通道组合成一个驱动器。INA 和 INB 输入连接在一起,OUTA 和 OUTB 也是如此。一个信号控制并联组合。

图 2:具有并联输出的 UCC27524A,可实现双倍驱动电流能力

提高系统效率的一个结果是功率密度增加。对更高功率密度的需求是隔离电源、DC/DC 砖和太阳能逆变器的功率因数校正 (PFC) 和同步整流模块等应用的趋势,在这些应用中,设计人员被限制在相同尺寸(或更小!)以获得相同数量的输出功率。

TI 的产品组合包括具有高电流、快速上升和下降时间以及延迟匹配的栅极驱动器。请参阅表 1。

| 类别 | 装置 | 描述 | 上升/下降时间 | 延迟匹配 |

|

大电流驱动器 |

UCC27714 | 4A、600V 高边和低边驱动器 | 15纳秒, 15纳秒 | 是的 |

| UCC27524A | 5A、高速低边双驱动器 | 7纳秒, 6纳秒 | 是的 | |

| UCC27211A | 4A、120V 高边和低边驱动器 | 7.2秒,5.5秒 | 是的 |

表 1:大电流栅极驱动器

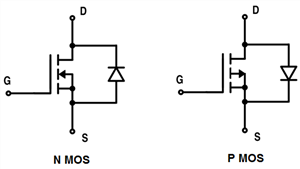

高速栅极驱动器可以通过降低FET的体二极管的功耗来提高效率。体二极管是寄生二极管,对于大多数类型的FET是固有的。它由p-n结点形成并且位于漏极和源极之间。图1所示为典型MOSFET电路符号中表示的体二极管。

图1:MOSFET符号包括固有的体二极管

限制体二极管的导通时间将进而降低其两端所消耗的功率。这是因为当MOSFET处于导通状态时,体二极管上的电压降通常高于MOSFET两端的电压。由于对于相同的电流水平,P = I×V(其中P是功耗,I是电流,V是电压降),通过MOSFET通道的传导损耗显着低于通过体二极管的传导损耗。

这些概念在电力电子电路的同步整流中发挥作用。同步整流通过用诸如功率MOSFET的有源控制器件代替二极管来提高这些电路的效率。减少体二极管导通使这种技术的优点最大化。

让我们考虑一个同步降压转换器。当高侧FET关断并且电感器中仍然存在电流时,低侧FET的体二极管变为正向偏置。小死区时间对避免直通很有必要。在此之后,低侧FET导通并开始通过其通道导通。相同的原理适用于通常在DC / DC电源和电动机驱动设计中发现的其它同步半桥配置。

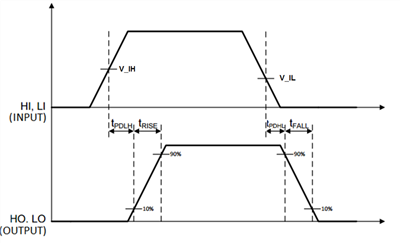

负责高速接通的一个重要的栅极驱动器参数是导通传播延迟。这是在栅极驱动器的输入端施加信号到输出开始变高的时间之间的时间。这种情况的一个示例如图2所示。该想法是,当FET重新导通时,体二极管将关断。快速导通传播延迟可以更快地导通FET,从而最小化体二极管的导通时间,进而使损耗最小化。

TI的产品组合包括具有行业领先的高速导通传播延迟的栅极驱动器。参见表1。

| 类别 | 设备 | 描述 | 开启传播延迟 |

| 高速驱动器 | UCC27517A | 4A / 4A高速低侧栅极驱动器 | 13ns |

| UCC27611 | 4A / 6A高速低侧栅极驱动器 | 14ns | |

| UCC27201A | 3A,120V高侧和低侧驱动器 | 20ns |

表1:高速驱动器

系统效率是一个团队努力的结果。本博客系列介绍了高速和高电流栅极驱动器是关键件。

审核编辑:郭婷

-

利用高电流栅极驱动器实现更高的系统效率2022-11-14 739

-

高电流栅极驱动器如何帮助系统实现更高的效率2021-12-23 1436

-

栅极驱动器是什么,为何需要栅极驱动器?2021-07-09 6349

-

高电流栅极驱动器助力实现更高的系统效率2019-08-07 2338

-

高速栅极驱动器助力实现更高系统效率2019-03-08 2426

-

隔离式栅极驱动器的揭秘2018-11-01 2724

-

隔离式栅极驱动器揭秘2018-10-25 4282

-

实现隔离式半桥栅极驱动器的设计基础2018-10-16 3024

-

实现隔离式半桥栅极驱动器的设计途径2018-09-26 1890

-

如何实现更高的系统效率——第二部分:高速栅极驱动器2017-03-01 2158

-

如何利用高电流栅极驱动器实现更高的系统效率2017-01-12 1421

全部0条评论

快来发表一下你的评论吧 !