模拟电磁干扰是否可能

描述

如今,由高频多相 DC/DC 转换器提供强大支持的千兆赫兹 (GHz) 处理器以GHz速度与存储器进行通信。在这些频率上,组件和印刷电路板 (PCB) 寄生阻抗会产生与频率有关的电压降,而天线结构和 PCB 谐振接着又引发电磁干扰 (EMI)、信号完整性和电源完整性 (SI/PI) 问题。在先前的一篇博文中,我仔细研究了满足与超快速功率晶体管(比如:LMG5200 半桥 GaN 开关)的电磁兼容性的难题。在这篇博文中,我们将察看能够在制造之前帮助确定 PCB 问题区域的高度精细复杂的软件工具。

设计高速、混合信号 PCB 需要经验丰富的工程人员和设备资源 - 因此,开发成本会非常高,特别是在需要对一块电路板实施多次迭代以实现电磁兼容性的时候。EMI、SI 和 PI 设计问题会拖延产品发布,而且如果在产品发布之后未被发现,则势必导致客户退货、产品召回以及消费者信心的缺失。一家公司的盈利能力取决于其产品的谨慎分析,而且由于工作频率不断提高,就愈发需要了解 PCB 的电磁 (EM) 场运行方式了。

幸运的是,相同的高速 GHz 处理器和电路板已经在电路设计中实现了一种新的范式:非常先进的电路仿真。正如许多人已经知道的那样,可以运用电路仿真来优化电路性能,甚至完成已知 PCB 器件的最坏情况电路分析。但是,能否对那些作为导致 EMI 和 SI/PI 问题发生之根源的“隐性”PCB 寄生元件进行仿真呢?幸运的是,如今的回答绝对是肯定的!

在过去的几年里我一直关注着 3-D EM 求解器的进展,并且对 Computer Simulation Technology (CST) 专门围绕 3-D EM 分析所做的工作印象非常深刻。例如,我快速地把 LMG5200 评估板 CAD 文件作为一个 OBD++ 文件植入了 CST EMC Studio,并采用一个宽带激励信号对 PCB 平面、印制线和组件阻抗进行了特性分析。

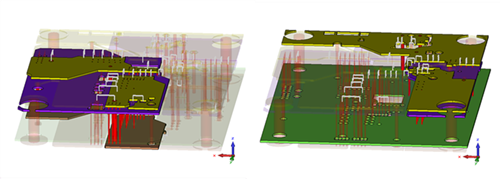

在推进任何高速电路板设计的过程中,仔细地检查电路板走线、平面结构、过孔和组件布局是一个基本要素。在 CST EMC Studio 中,我发现电源地被连接至第二层上的一个较小的分离平面(图 1)。当我把激励信号施加至连续且不间断的所示接地平面(而不是该分离平面)时,辐射发射的仿真结果有了显著的改善。该结果与之前采用 TEM 单元测量的结果相当地一致,正如我在早先的一篇博文中论述的那样。

图 1:CST EMC Studio 中的层堆叠可视化

图 1 中左侧的插图示出了输入“电源地”是如何连接至第二层上的一个分离平面(紫色平面)的。而位于右侧的插图则示出了第三层上的接地平面(用绿色表示)。

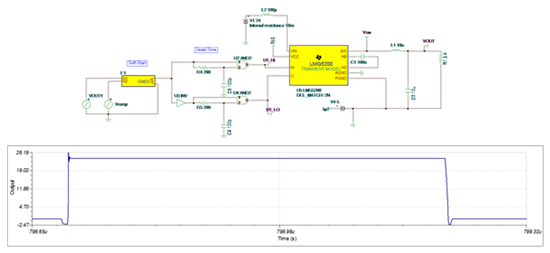

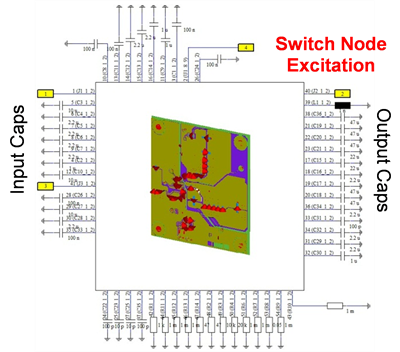

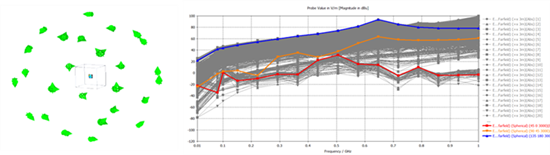

采用 TINA-TI™ 软件进行的 LMG5200 的 SPICE 电路仿真预测了 LMG5200 在 60W、24V 至 12V 电源转换中的开关操作特性,并示于图 2。该仿真可能也采用 CST Design Studio 做过。接着,将此开关波形应用于图 3 所示的采用 CST Design Studio 的“协同仿真”中的 3-D EM 仿真结果。然而值得注意的是,3-D EM 仿真是计算密集型的工作 - 在复杂的电路板网格中求解 Maxwell 方程很耗时间!当采用一台具有一个图形处理单元和 8 GB 内存的四核计算机时,3-D EM 仿真的运行需要超过 3 个小时的时间。输入 / 输出电容器和激励信号在 CST Design Studio 的内部被表示为端口,而电场结果则示于图 4。

图2:用于3-D EM仿真的激励信号

图3:协同仿真——SPICE激励信号应用于3-D EM场仿真

图4:探头和电场在 3 米时的测量范围

图4中的仿真结果是对放置在 3m 探测范围内的电路板周围的每个电场探头的记录。在特定频率上产生的谐振与我在前一篇博文中提供的实测结果相当地一致。从仿真结果可以看到,放在某些位置的探头具有较高的辐射级别,因而可洞察电路板上潜在的问题区域。

从功能强大的3-D EM 仿真器的这种基本应用可以清楚地看到,当试图设计高速电源转换器、配电网络 (PDN) 和其他高速信号/通信总线时,对 PCB 的微波性能进行仿真是可行的,而且越来越重要。采用宽带隙半导体器件(如 LMG5200)的电路板设计将不得不处理皮秒级的上升时间和超过 40V/ns 的电压转换速率。当推进符合电磁兼容性要求的解决方案时,诸如此类的电源转换有必要对电磁场工作特性拥有更高的灵敏度。

审核编辑:郭婷

-

电源滤波器是否会产生自身的电磁干扰2024-12-25 995

-

电磁干扰训练系统原理是什么2024-07-22 1101

-

海上电磁干扰训练系统2024-07-15 789

-

电磁干扰系统技术有哪些2024-05-10 1499

-

电磁干扰是怎么产生的 电磁干扰屏蔽简易方法2024-01-10 17485

-

怎样识别电磁干扰源?2023-09-13 3250

-

电磁干扰是怎么产生的 电磁波干扰的途径有几种2023-06-19 8878

-

模拟电磁干扰是否可能?2022-11-02 565

-

非隔离式电源的共模电流可能成为一个电磁干扰源?2021-04-20 3553

-

该怎样预防电磁干扰对模拟集成电路造成影响?2018-08-14 7327

-

电磁干扰的定义_电磁干扰原理2017-11-01 19125

-

出色模拟工程师必备系列(一):电磁干扰(EMI)2016-11-04 3413

-

如何成为出色的模拟工程师(一):电磁干扰(EMI)2012-11-22 64098

-

电磁干扰源对DCS系统有哪些干扰?2011-11-21 4495

全部0条评论

快来发表一下你的评论吧 !