半桥DC-DC转换器设计方案降低数据中心功耗

电源/新能源

描述

转载自All About Circuits官网,作者Hiroshi Takei

为了控制电源,数据中心已开始广泛采用基于48V总线电压的新型机架架构。学习如何设计半桥DC-DC转换器以实现这种48V系统。

为满足数据存储日益增长需求,必须扩容并建立新的数据中心。这种扩展最终会显著增加功耗,随之而来的是如何控制电源。

服务器机架采用48V总线电压是一种降低数据中心功耗十分有效的方法。不过,只有使用精心选择的高效MOSFET才能搭建这样的架构。

数据中心通常需要大量电力,设计得当的情况下,48V总线系统是减少功耗的有效方法。

开放式机架架构如何解决功耗问题

为了提高能效,必须解决功耗问题。开放计算项目(OCP)①提出开放式机架架构,采用48V总线电路而不是传统12V总线电路降低功率损耗。

要了解这种方法的工作原理,首先回顾一下采用I2R计算电线功率损耗,其中R代表电线电阻,I代表电线电流。根据电流与电阻之间的这种简单关系,相同电阻的情况下,电流越小,功耗越低,效率越高。

开放式机架架构下,考虑12V总线电路与48V总线电路为服务器机架提供相同电量时产生的功耗:48V总线电路传输的电流仅为12V总线传输电流的1/4。因此,假设48V和12V总线电路电阻相同,48V总线损耗的功率仅为12V总线的1/16。

采用半桥DC-DC转换器搭建开放式机架

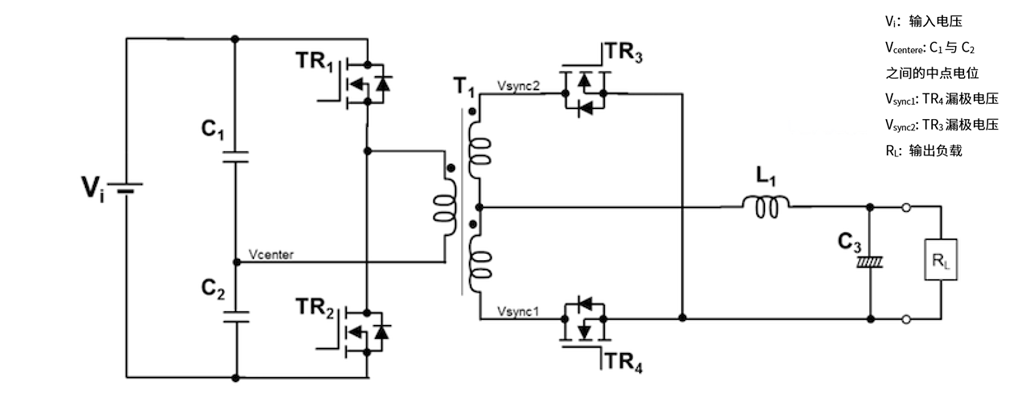

在理论基础上实际应用开放式机架架构时,可考虑使用半桥DC-DC转换器,如图2所示。这种转换器可以有效地将48V总线电压降到1.2V,减小系统总功耗。

图2. 简易半桥DC-DC转换器

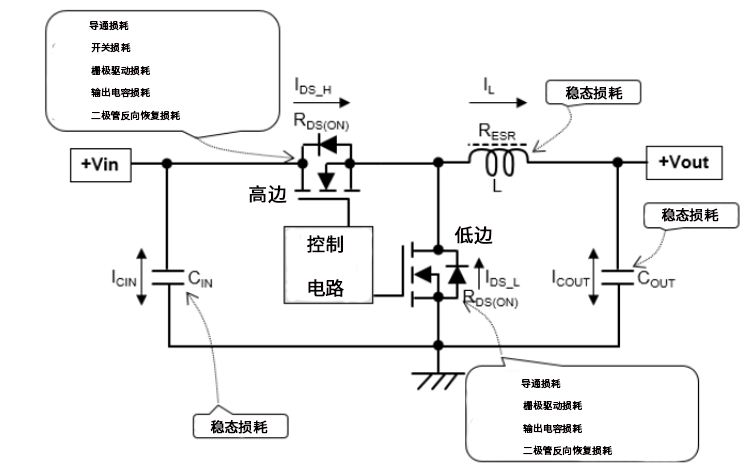

半桥DC-DC转换器最大功耗源于开关操作。除开关损耗外,还包括栅极驱动损耗、输出电容损耗、二极管反向恢复损耗和导通损耗,所有这些损耗都将影响DC-DC转换器的整体效率。

图3. 降压DC-DC转换器损耗来源

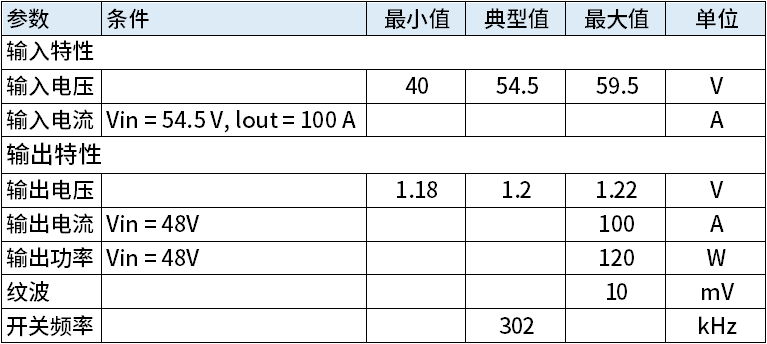

正确选择功率MOSFET,可显著降低图3所示各种损耗。选择用于半桥DC-DC转换器的MOSFET时(如用于48V总线系统),需要考虑几个因素和主要限制。此类系统的典型特性如图4所示。

图4. 半桥DC-DC转换器输入和输出特性如图2所示。

任何规格的MOSFET,必须确定输入特性(输入电压和电流)以及输出特性(纹波、开关频率、电压、电流和功率)。此外,必须知道电路拓扑结构,以及MOSFET用于原边还是副边。

东芝方法

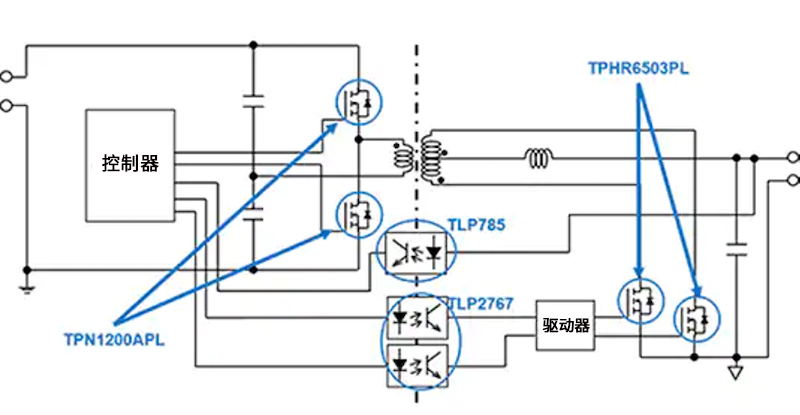

采用图5所示参考设计②和参数以及图4概括的特性,东芝研究了实现最高效48V总线系统所需的最有效、最实用的功率MOSFET。

图5.支持48V总线系统的半桥DC-DC转换器评估板。

图6方框图显示东芝开发的设计,采用特定MOSFET总效率达92.8%(Vin=54.5V,30%负载),证明是实现高效率并将转换器尺寸减小到仅为160mm×100mm的理想选择。

图6. 1.2V/100A输出隔离式DC-DC转换器方框图,

48V总线电压直接转换为1.2V。

原边主要受开关损耗影响,因此输入电容小的MOSFET产品具有优越性,TPN1200APL③可在中负载至重负载(40A至100A)条件下实现高效率。减小输入电容和导通电阻,导通电阻仅为9.8mΩ,可以实现这种高效率。

在副边,内置二极管在MOSFET导通之前工作,因而副边以导通损耗为主。因此,导通电阻小的MOSFET效果最好,东芝TPHR6503PL④在中负载至重负载条件下具有很高的效率。

这种硅n沟道MOSFET具有高速开关能力,漏极-源极导通电阻仅为0.41mΩ。同时具有栅极电荷、输出电荷小,漏电流低的特点。

一切为了降耗

OCP提出的开放式机架架构使用48V总线电路降低功耗,提高效率。而支持48V总线系统的半桥DC-DC转换器是一种有效配置方法。

这种方法需要仔细选择MOSFET才能达到预期效果。东芝的研究表明,根据他们开发的紧凑高效的设计,原边可使用TPN1200APL MOSFET,副边可使用TPHR6503PL。

东芝提供优质高效的MOSFET,VDSS从30V到250V,每类VDSS包括不同的导通电阻类型,因此工程师设计DC-DC转换器时,可以找到适用的MOSFET。

审核编辑:汤梓红

-

如何降低DC-DC转换器的纹波噪声2024-03-13 3732

-

半桥DC-DC转换器电路图 半桥DC-DC电路介绍及PCB布局注意点2023-07-25 9235

-

半桥DC-DC转换器PCB设计指南2023-06-05 1876

-

基于LM5036“智能”型半桥DC/DC电源设计方案2023-04-03 2252

-

基于LM5036智能型半桥DC/DC电源设计方案分享2022-11-10 734

-

DC-DC转换器和AC-DC转换器的区别及功能2021-11-17 7228

-

什么是DC-DC转换器?DC-DC转换器是如何命名的?2021-11-09 5190

-

半桥式DC-DC变换器设计2021-09-15 2298

-

非隔离式的DC-DC转换器解析2020-12-09 5651

-

电子书:DC-DC 转换器的应用与设计方案2019-03-14 7732

-

多芯片集成在隔离型DC-DC转换器的实现2018-10-24 2050

-

DC-DC转换器2010-03-09 4130

-

LM2717-ADJ双降压式DC-DC转换器的设计方案2009-12-29 1574

-

利用超低电流、脉冲频率调制(PFM) DC-DC转换器降低待2009-09-18 3920

全部0条评论

快来发表一下你的评论吧 !