CXL SSD的性能会与NVMe SSD有何区别?

存储技术

描述

CXL SSD也是利用存储网络行业协会(SNIA) NVM编程模型(NVM Programming Model)的另一种选择,因为非易失性DIMM成本较高,而Intel正在逐步停止对Optane的支持。当CXL SSD与使用该模型的下一代程序搭配时,企业将会看到益处。这种新型存储技术应该会为未来的计算系统提供急需的提升。 CXL SSD在需要大量内存的应用程序中可能会变得流行。然而,可能不清楚为什么CXL SSD的性能会与NVMe SSD有所不同。

从本质上讲,CXL 技术在 CPU 内存空间和连接设备上的内存之间保持内存一致性。这支持资源共享(或池化)以获得更高的性能,降低软件堆栈的复杂性,并降低整体系统成本。CXL 联盟已经确定了将采用新互连的三类主要设备: 类型1设备:智能 NIC 等加速器通常缺少本地内存。通过 CXL,这些设备可以与主机处理器的 DDR 内存进行通信。 类型2设备:GPU、ASIC 和 FPGA 都配备了 DDR 或 HBM 内存,并且可以使用 CXL 使主机处理器的内存在本地可供加速器使用,并使加速器的内存在本地可供 CPU 使用。它们还共同位于同一个缓存一致域中,有助于提升异构工作负载。 类型 3 设备:内存设备可以通过 CXL 连接,为主机处理器提供额外的带宽和容量。内存的类型独立于主机的主内存。

CXL 协议和标准

CXL 标准通过三种协议支持各种用例:CXL.io、CXL.cache 和 CXL.memory。

CXL.io:该协议在功能上等同于 PCIe 协议,并利用了 PCIe 的广泛行业采用和熟悉度。作为基础通信协议,CXL.io 用途广泛,适用于广泛的用例。

CXL.cache:该协议专为更具体的应用程序而设计,使加速器能够有效地访问和缓存主机内存以优化性能。

CXL.memory:该协议使主机(例如处理器)能够使用加载/存储命令访问设备连接的内存。

这三个协议共同促进了计算设备(例如 CPU 主机和 AI 加速器)之间内存资源的一致共享。从本质上讲,这通过共享内存实现通信简化了编程。用于设备和主机互连的协议如下:

类型 1 设备:CXL.io + CXL.cache

类型2设备:CXL.io + CXL.cache + CXL.memory

类型 3 设备:CXL.io + CXL.memory

Compute Express Link 与 PCIe:这两者有什么关系?

CXL 建立在PCIe的物理和电气接口之上,其协议建立了一致性、简化了软件堆栈并保持与现有标准的兼容性。具体来说,CXL 利用 PCIe 5 功能,允许备用协议使用物理 PCIe 层。当支持 CXL 的加速器插入 x16 插槽时,设备会以每秒 2.5 千兆传输 (GT/s) 的默认 PCI Express 1.0 传输速率与主机处理器的端口进行协商。只有双方都支持 CXL,CXL 交易协议才会被激活。否则,它们作为 PCIe 设备运行。

CXL 1.1 和 2.0 使用 PCIe 5.0 物理层,允许通过 16 通道链路在每个方向上以 32 GT/s 或高达 64 GB/s 的速度传输数据。

CXL 3.0 使用 PCIe 6.0 物理层将数据传输扩展到 64 GT/s,支持通过 x16 链路进行高达 128 GB/s 的双向通信。

CXL 2.0 和 3.0 有什么新功能?

首先在内存池方面,CXL 2.0 支持切换以启用内存池。使用 CXL 2.0 交换机,主机可以访问池中的一个或多个设备。尽管主机必须支持 CXL 2.0 才能利用此功能,但内存设备可以是支持 CXL 1.0、1.1 和 2.0 的硬件的组合。在 1.0/1.1 中,设备被限制为一次只能由一台主机访问的单个逻辑设备。然而,一个 2.0 级别的设备可以被划分为多个逻辑设备,允许多达 16 台主机同时访问内存的不同部分。

例如,主机 1 (H1) 可以使用设备 1 (D1) 中一半的内存和设备 2 (D2) 中四分之一的内存,以将其工作负载的内存需求与内存池中的可用容量完美匹配. 设备 D1 和 D2 中的剩余容量可由一台或多台其他主机使用,最多可达 16 台。设备 D3 和 D4 分别启用了 CXL 1.0 和 1.1,一次只能由一台主机使用。 CXL 3.0 引入了对等直接内存访问和对内存池的增强,其中多个主机可以一致地共享 CXL 3.0 设备上的内存空间。这些功能支持新的使用模型并提高数据中心架构的灵活性。

其次来到交换方面; 通过转向 CXL 2.0 直连架构,数据中心可以获得主内存扩展的性能优势,以及池内存的效率和总体拥有成本 (TCO) 优势。假设所有主机和设备都支持 CXL 2.0,则“切换”通过 CXL 内存池芯片中的交叉开关集成到内存设备中。这可以保持较低的延迟,但需要更强大的芯片,因为它现在负责交换机执行的控制平面功能。通过低延迟直接连接,连接的内存设备可以使用 DDR DRAM 来扩展主机主内存。这可以在非常灵活的基础上完成,因为主机能够访问处理特定工作负载所需的尽可能多的设备的全部或部分容量。 CXL 3.0 引入了多层交换,支持交换结构的实施。CXL 2.0 支持单层交换。借助 CXL 3.0,启用了交换结构,其中交换机可以连接到其他交换机,从而大大增加了扩展的可能性。

第三,“按需”内存范例; 类似于拼车,CXL 2.0 和 3.0 在“按需”的基础上为主机分配内存,从而提供更高的内存利用率和效率。该架构提供了为标称工作负载(而不是最坏情况)配置服务器主内存的选项,能够在需要时访问池以处理高容量工作负载,并为 TCO 带来更多好处。最终,CXL 内存池模型可以支持向服务器分解和可组合性的根本转变。在此范例中,可以按需组合离散的计算、内存和存储单元,以有效地满足任何工作负载的需求。

第四,完整性和数据加密 (IDE); 分解——或分离服务器架构的组件——增加了攻击面。这正是 CXL 包含安全设计方法的原因。具体来说,所有三个 CXL 协议都通过完整性和数据加密 (IDE) 来保护,IDE 提供机密性、完整性和重放保护。IDE 在 CXL 主机和设备芯片中实例化的硬件级安全协议引擎中实现,以满足 CXL 的高速数据速率要求,而不会引入额外的延迟。应该注意的是,CXL 芯片和系统本身需要防止篡改和网络攻击的保护措施。在 CXL 芯片中实现的硬件信任根可以为安全启动和安全固件下载的安全和支持要求提供此基础。

第五,将信令扩展到 64 GT/s; CXL 3.0 带来了标准数据速率的阶跃函数增加。如前所述,CXL 1.1 和 2.0 在其物理层使用 PCIe 5.0 电气:32 GT/s 的 NRZ 信号。CXL 3.0 秉承了以广泛采用的 PCIe 技术为基础构建的相同理念,并将其扩展到 2022 年初发布的最新 6.0 版 PCIe 标准。使用 PAM4 信号将 CXL 3.0 数据速率提高到 64 GT/s。我们涵盖了 PCIe 6 中 PAM4 信令的详细信息——您需要知道的一切。 得益于CXL的出现,开发者可以简化和改进低延迟连接和内存一致性,显著提高计算性能和效率,同时降低 TCO。此外,CXL 内存扩展功能可在当今服务器中的直接连接 DIMM 插槽之上实现额外的容量和带宽。CXL 使得通过 CXL 连接设备向 CPU 主机处理器添加更多内存成为可能。当与持久内存配对时,低延迟 CXL 链路允许 CPU 主机将此额外内存与 DRAM 内存结合使用。大容量工作负载的性能取决于大内存容量,例如 AI。考虑到这些是大多数企业和数据中心运营商正在投资的工作负载类型,CXL 的优势显而易见。

什么是基于CXL的固态硬盘?

CXL和PCIe之间的区别可能不太明显。在信号级别上,这两者确实是相同的,但两者的协议不同。CXL选择比PCIe更快的协议,尽管CXL.io支持标准的PCIe I/O设备。 CXL的开发是为了支持从服务器主板(远程内存)中脱离出来的大型内存池,以增加驻留在服务器主板(近端内存)上的内存。所有这些内存都映射到服务器的内存地址空间中,并在服务器处理器芯片的内存管理单元的管理下。 与PCIe不同,CXL需要管理一致性。任何内存地址的内容,无论是近端内存还是远程内存,都可能比处理器缓存中的该地址的副本更新。除非另一个处理器尝试读取该内存地址,否则这不是一个大问题。CXL的内存一致性方案被精细地规定,以确保旧数据永远不会出现在处理器中,如果其他处理器的缓存中存在更新版本,则始终会出现。 软件通过字节语义(byte semantics)访问CXL.mem或CXL.cache设备上的内存——软件将其视为服务器主板上的内存。如果固态硬盘是CXL设备,则还必须通过CXL.mem协议与软件和通信,就好像它是内存一样。 标准固态硬盘通过PCIe总线上的NVMe使用块语义进行通信。对于CXL标准,这种通信已变成了CXL.io。 CXL管理必然较慢的远程内存和近端内存之间的不同时间。CXL SSD将其推向了极致:驱动器可以选择像标准固态硬盘一样缓慢地运行,而CXL通道仍然使用内存语义(memory semantics)将数据传输到处理器。预计将看到CXL SSD拥有相对巨大的缓存,以最小化这种缓慢的操作。

Samsung:这就是正确的路径

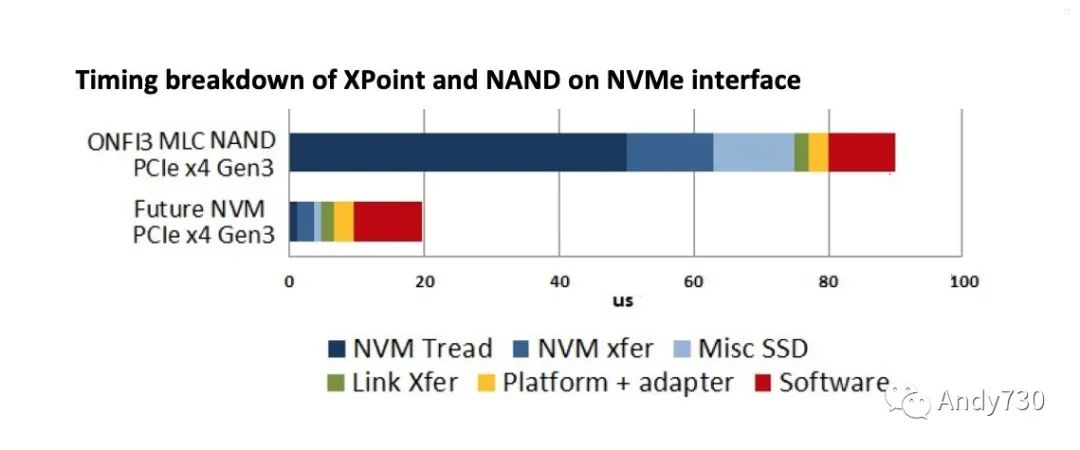

Samsung是CXL接口SSD的支持者,该公司在2022年的Flash Memory Summit上展示了一种称为“内存语义SSD”(MS-SSD)的技术。 内存语义SSD的理论基础是,从软件角度来看,驱动器中的持久介质是通过内存字节语义而不是通常用于SSD的块语义访问的。 I/O语义(块语义)通过中断驱动系统运行,这或许是自上世纪80年代以来的惯例。当时,软件的I/O例程可以增加毫秒级的延迟,而不会被注意到。这是应对比处理器慢得多的I/O设备的好方法。 在21世纪初期,当SSD开始广泛使用时,SSD用户注意到I/O例程会减慢SSD的速度。对这个软件的新的关注提高了它的速度,但是由处理器中断管理的磁盘I/O的基本结构限制了改进的程度。 同时,DRAM总线必须尽可能地快,这在90年代已经变成了同步的,并且随着这一变化,总线被剥夺了任何暂停以等待慢速存储设备的能力。只有内存可以连接到内存通道。存储必须通过I/O通道。 当持久性内存出现时,软件成为一个问题。这在以下图中有形象的描述。

上下两个条形图中红色部分表示由软件的I/O堆栈造成的延迟。对于代表NVMe NAND闪存SSD的上方条形图来说,这是整体访问时间中可管理的一部分。在包括Intel Optane持久内存模块的下方条形图中,红色部分约占总延迟的一半。 50%的速度损失是无法接受的,这促使开发了更快的接口CXL。CXL以近似于内存速度运行,但不同于双数据率内存总线,它可以与不同速度的内存一起使用。 通过设计带有CXL接口的SSD,Samsung打开了将SSD用作内存的大门。因此,所有SNIA和各种软件公司为支持像Optane这样的持久内存所做的工作都可以用于廉价的基于NAND闪存的存储。SNIA NVM编程模型是软件使用以发挥Intel Optane持久内存功效的协议,现在还有了一个额外的用途:它将支持CXL接口上的NAND闪存SSD。 然而,由于NAND闪存速度较慢,Samsung的设计使用大型DRAM缓存尽可能多的SSD。Samsung在Flash Memory Summit上展示的2TB原型机配备了惊人的16GB内部DRAM缓存。这样大的缓存可能会成为CXL SSD的标准。 然而,这样的大缓存也会产生好处。在Samsung分享的基准测试中,该公司表示,相比现有的SSD,它能将随机读取性能提高约1900%。Samsung声称,MS-SSD可以作为服务器内存的2TB扩展呈现给主机。这个内存的平均延迟取决于SSD内部缓存的命中率。 这个SSD的全部2TB不需要都映射为内存。Samsung的设备可以分成内存区域和SSD区域,由CXL.mem或CXL.io服务,在Samsung称之为“双模式”操作中提供更多的灵活性。

持久性的可能性

Samsung的第一代原型不支持内存持久性。这需要一些工作,因为在停电期间需要保持整个16GB的DRAM存活,或者直到其全部内容都能够写入SSD的NAND闪存。这两种情况都需要大量储存的能量,可以是电池或超级电容器。公司的目标是在第二个原型中包括持久性内存操作,该原型原定于去年年底完成。 如果CXL SSD作为持久性内存被接受,存储管理员的工作将发展成与Intel Optane成为主流时相同。软件和硅供应商希望自动数据管理软件可以隐藏存储管理员的任何问题,但是会有数据安全方面的考虑,因为敏感数据可能存储在CXL SSD和映射到内存-存储层次结构较慢的传统SSD中。

其他CXL SSD的发展

Samsung不是唯一一个计划支持CXL接口的SSD的公司。Kioxia公开讨论了一种基于公司专有XL-Flash芯片设计的概念验证CXL SSD。XL-Flash是NAND闪存,专注于速度,可能是针对3D XPoint存储器的推出而设计的,这些存储器最初被一些公司视为标准NAND闪存SSD的威胁。Kioxia的CXL SSD设计侧重于64字节事务的速度,特别是64字节随机写入。 该公司解释说,它预计其设计的性能几乎与DRAM一样快,比Optane快。它支持的内存大小比近内存DRAM大两个数量级,比近内存Optane持久性内存DIMM大10倍。Kioxia的设计使用了一个大型预取缓冲区,但与Samsung的设计不同之处在于添加了硬件压缩以帮助提高速度。数据较小,SSD需要的带宽较少,可以加速写入。该公司的目标是在本季度推出其CXL SSD仿真器。 此外,韩国科学技术高等研究院的计算机架构和存储系统实验室(CAMEL)与RISC-V和OpenExpress合作,正在模拟CXL SSD的运行,以更好地了解它可能提供的性能优势。它编程一个仿真器来模拟基于Samsung超快速Z-NAND芯片的32GB SSD的操作——与Kioxia XL-Flash有些类似——并将其操作与具有大型DRAM的系统进行比较。 性能高度依赖于SSD中数据的局部性;这是很自然的,因为高局部性意味着大多数SSD访问会命中SSD的DRAM缓存,而不是它的NAND闪存。对于高局部性,CXL SSD提供的数据仅比CPU的本地DRAM的延迟高2.4倍。然而,在局部性较低的情况下,CXL SSD的延迟是DRAM的84倍。显然,CXL SSD为数据集高度局部化的应用程序带来了更多的性能。 CAMEL还发现,在高局部性应用程序中,NVMe SSD的延迟是CXL SSD的129倍。然而,在局部性较低的应用程序中,其延迟仅比CXL SSD高约50%。 这种局部性敏感性反映了Samsung的发现,其CXL SSD在缓存命中期间以大约2000万IOPS的速度运行,具有次微秒级的延迟,对于128字节的随机读取。 Source: Jim Handy, Understand how the CXL SSD can aid performance, 22 Mar 2023

编辑:黄飞

-

NVMe SSD性能影响因素分析2023-11-13 2849

-

Xilinx FPGA高性能NVMe SSD主机控制器,NVMe Host Controller IP2024-03-27 1411

-

NVMe P4600的速度部分低于SATA SSD?2018-11-28 4691

-

在Xilinx ZCU102评估套件上启用NVMe SSD接口2020-09-03 6895

-

开放通道SSD有何作用2021-11-09 2537

-

如何为工业应用设计NVMe SSD呢2022-03-07 1577

-

西部数据推出新款高性能NVMe SSD2018-05-24 2227

-

NVMe SSD与SATA SSD的性能对比2018-07-27 37597

-

影响SSD性能的因素有哪些 NVMe SSD性能解析2018-11-05 10139

-

Western Digital 发布ZNS NVMe SSD2019-06-24 6539

-

NVMe和SATA SSD的区别2019-12-18 25467

-

Flashtec系列的最新成员 Flashtec NVMe 3108 PCIe Gen 4企业NVMe SSD控制器2020-09-11 3753

-

重新定义NVMe SSD外形2020-09-23 4076

-

SATA SSD对比M.2 SSD有何区别2021-02-21 14438

-

浪潮NVMe SSD的性能2022-08-03 2876

全部0条评论

快来发表一下你的评论吧 !