VCS+VERDI的reverse反向运行功能

电子说

描述

背景

假设一种场景,在调试环境的时候,运行到15min的时候,环境出现bug,需要去debug。也许错误的第一现场并不是15min的时候,可能在14min30s-15min之间,那么如果正向执行就需要14min30s以上。所以这个时候如果能够直接反向运行到14min30s,就可以节省很多时间。就像jojo的奇妙冒险中吉良吉影的招式,败者食尘一样,逆转时间

编译选项

要实现这个功能,依赖于VCS和VERDI的联合调试,所以在编译的时候需要使用下面的指令

vcs -full64 -sverilog -ntb_opts uvm-1.2 -lca -kdb -debug_access+reverse

除了常规的选项以外,-kdb选项是用于生成kdb数据库,支持verdi的联合调试,而lca是kdb的依赖选项。

最后的-debug_access+reverse则是最关键的开关,需要加上这个选项才是实现反向运行。

编译完成以后,进行仿真的时候,需要使用./simv -verdi,启动仿真。这样就能够直接调用verdi进行联合仿真。

测试代码

本次的测试代码就是简单的4行打印。

module test ();

import uvm_pkg::*;

`include "uvm_macros.svh"

initial begin

`uvm_info("a","hello uvm!",UVM_NONE)

`uvm_info("b","hello uvm!",UVM_NONE)

`uvm_info("c","hello uvm!",UVM_NONE)

`uvm_info("d","hello uvm!",UVM_NONE)

end

endmodule

reverse

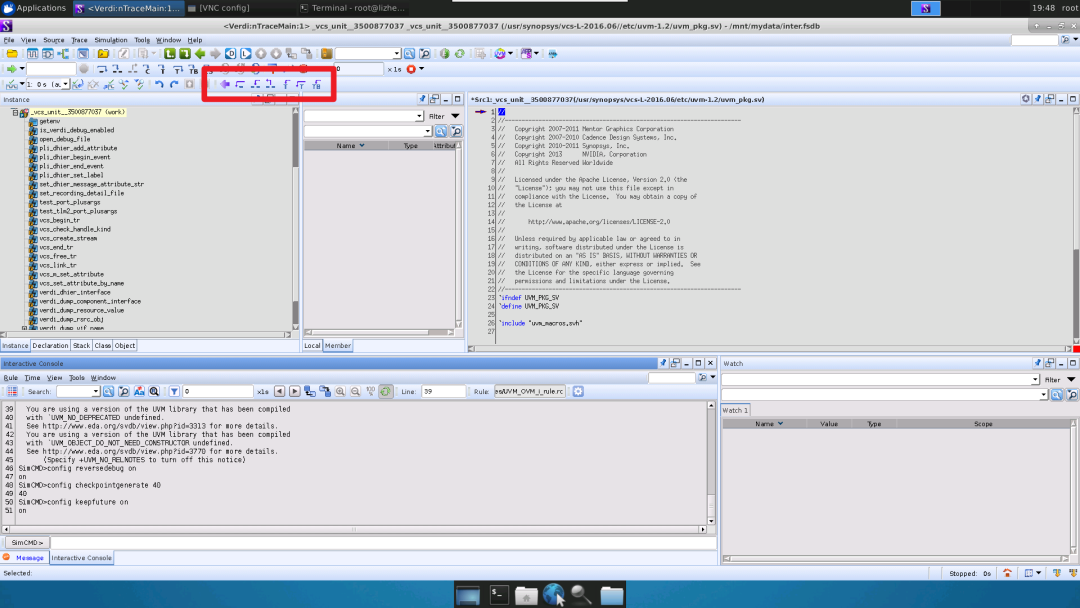

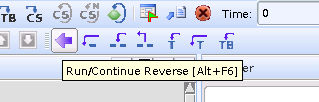

启动verdi之后,注意图中红色框框中的一排按钮,这就是reverse功能的按钮。从图标形状来开,和联合仿真的正向交互式仿真是一致,功能上他们其实也是对偶的。

reverse按钮

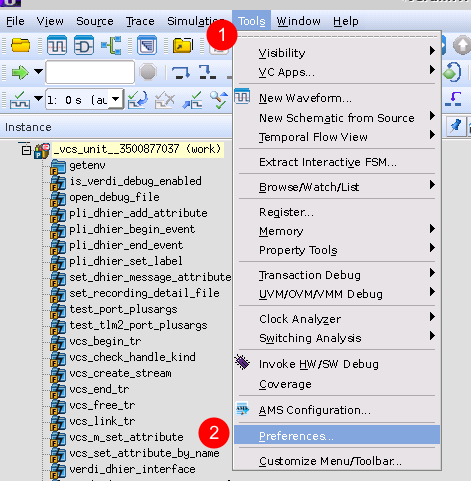

如果你开起了reverse选项,但是仍然没有出现这一排按钮,那么就需要在tools下的perferences中,开启reverse按钮。

perferences

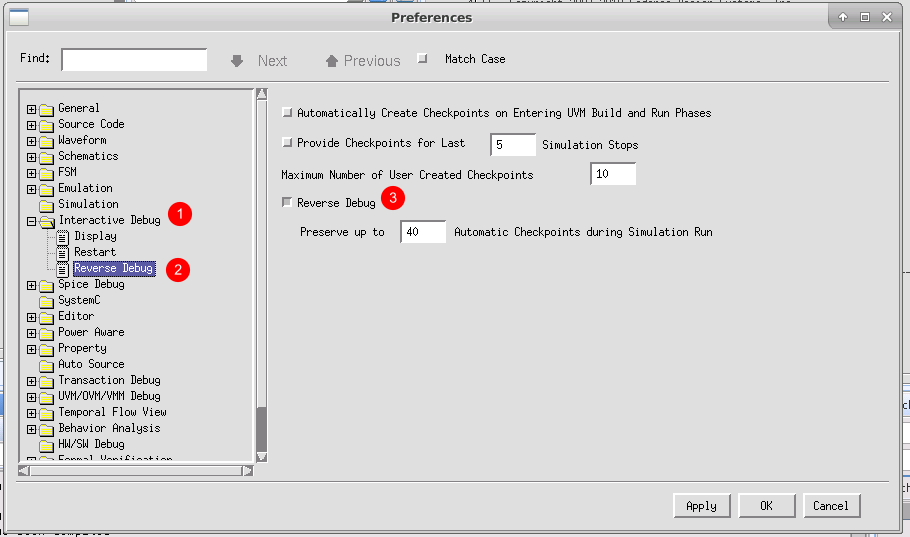

在perferences中的interactive debug下,找到reverse debug

reverse

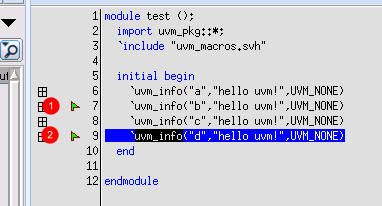

接下来可以在代码中设置两个断点进行测试。直接单击代码左侧即可甚至断点。和C的单步调试是一样的,直接run就能在断点处停止。

设置断点

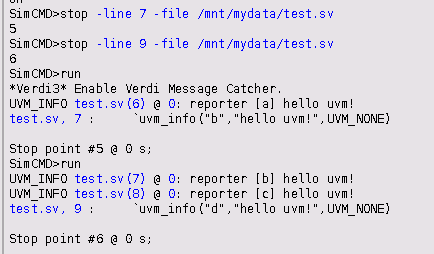

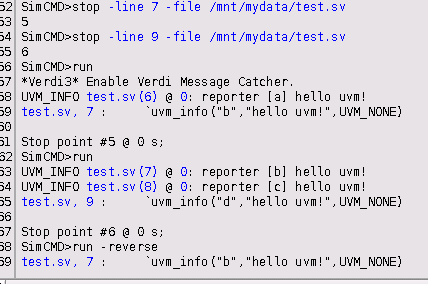

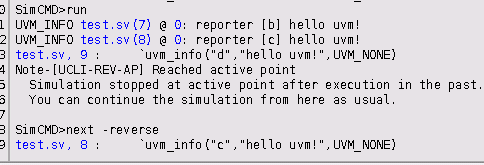

我们跑到第九行的断点,可以看到中间在七行停止了一次,最后在第九行停下来,6 7 8行的信息都已经打印出来了。

前向运行

那么如果我们需要回到第七行,就可以直接进行点击下图中的run reverse按钮。

run reverse

然后就能够回到上一个断点处

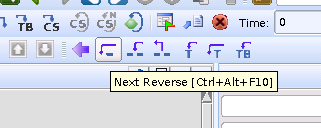

当然也可以,点击旁边的next reverse按钮进行反向单步运行

反向单步

就能够从第九行回到第八行

其他按钮和这两个类似,但是正向调试的反向版本。

本次分享了VCS+VERDI的reverse反向运行功能,可以将整个仿真反向运行,从而减少正向仿真的时间消耗。

当然,这必须在VCS+VERDI的联合调试下才可以,如果是VCS单独仿真,dump波形,再使用VERDI离线调试就不能使用。而联合仿真也会大幅度降低运行速度,所以推荐在早期debug验证环境的时候使用。

审核编辑:刘清

-

芯来e203移植开发分享(一)——vcs+verdi仿真环境搭建2025-10-27 247

-

在Linux上用vcs+verdi对demo_nice进行仿真没有成功的原因?2023-08-12 621

-

请问如何更新bin/run.makefile以支持VCS+Verdi工具?2023-08-11 596

-

Verdi环境配置、生成波形的方法2023-05-29 9323

-

如何用vcs+verdi仿真Verilog文件2023-05-11 3038

-

如何用vcs+verdi仿真Verilog文件并查看波形呢?2023-05-08 8117

-

全网最实用的Verdi教程12023-05-05 22886

-

利用vcs+verdi仿真工具蜂鸟E200系列处理器仿真分析2022-11-17 4423

-

VCS+Verdi如何安装?怎么破解?2021-06-21 7678

-

怎样去使用Makefile+VCS+Verdi做个简单的Test Bench?2021-06-18 4316

-

vcs和verdi的调试及联合仿真案例2020-09-22 10082

-

请教VCS和verdi怎么联合使用2015-01-22 8230

全部0条评论

快来发表一下你的评论吧 !