RA2快速设计指南 [8] I/O端口配置(2)

描述

9. I/O端口配置(2)

9.2 设置端口并将其用作GPIO

有两种方法可以设置端口并将其用作GPIO:一种是使用端口控制寄存器(PCNTR1),另一种是使用PmnPFS寄存器。

方法1:端口控制寄存器(PCNTR1)

• 通过向端口控制寄存器1(PCNTR1)的端口方向位 (PDRn) 写入“1”,选择一个引脚作为输出。

• 端口方向位 (PDRn) 是可读写的。将该值设置为“1”将选择该引脚作为输出。I/O端口的默认状态为“0”(输入)。可以在RA2 MCU上读取端口方向寄存器。

• 相应端口控制寄存器 (PCNTR1) 中的端口输出数据位 (PODRn) 是可读写的。读取PODR时,也会读取输出数据锁存器的状态(不是引脚电平)。

• 端口控制寄存器 2 (PCNTR2) 中的端口输入位 (PIDRn) 是只读的。读取PCNTR2寄存器中的 PIDRn 位以读取引脚状态。

方法2:端口mn引脚功能

选择 (PmnPFS) 寄存器

• 端口模式寄存器 (PMR) 是可读写的,用于指定各个引脚是用作GPIO还是用作外设引脚。复位后,所有PMR寄存器均置0,这会将所有引脚都设置为GPIO。如果PMR寄存器置1,则该对应的引脚将用于实现外设功能。外设功能由该引脚的MPC设置定义。

• 将引脚设置为输出时,建议先将所需的端口输出值写入数据锁存器,然后将方向寄存器设置为输出。尽管在所有系统中此操作都不太重要,但这可以防止在设置端口时出现意外的输出毛刺。

通常,使用PCNTR1配置端口有助于提高访问速度,但可用的配置功能较少。使用PmnPFS寄存器将获得更多可用的配置功能,但访问速度较慢。

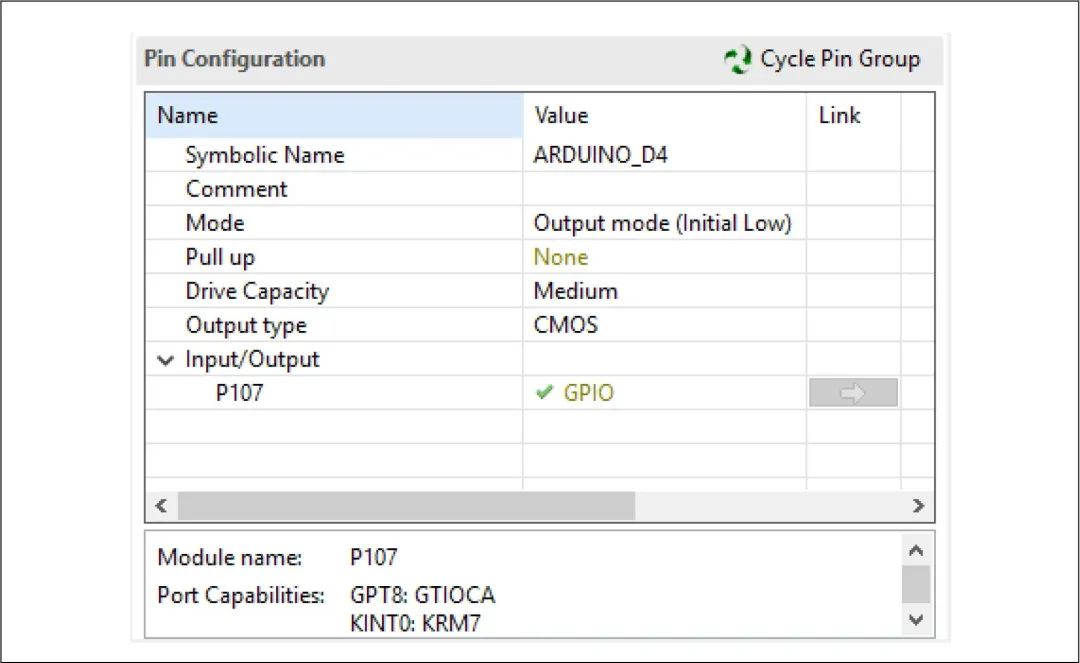

Renesas FSP提供了引脚配置工具,以在复位后配置GPIO引脚,如图19所示。配置GPIO后,可以在FSP中使用HAL层API对该GPIO进行控制

图19. 使用FSP配置器将P107配置为输出和低电平

9.2.1 内部上拉

• 端口0到9上的大多数引脚都可以选择使能上拉电阻。上拉由每个端口mn引脚功能选择 (PmnPFS) 寄存器中的上拉 (PCR) 位控制。每个PmnPFS寄存器中的PCR位用于控制端口上的相应引脚。

• 首先,必须通过PmnPFS寄存器中的相关位将该引脚设置为输入。将PCR位置“1”以使能上拉,将其置“0”以禁用上拉。

• 复位后,会将所有PCR寄存器清零,因此将禁用所有上拉电阻。

• 每当将某个引脚指定为外部总线引脚、GPIO输出或外设功能输出引脚时,上拉就会自动关闭。

9.2.2 漏极开路输出

• 配置为输出的引脚通常用作CMOS输出。

• 端口0到上的大多数引脚都可以选择配置为NMOS漏极开路输出。

• 每个端口9mn引脚功能选择 (PmnPFS) 寄存器中的N沟道漏极开路控制 (NCODR) 位控制哪些引脚以漏极开路模式工作。将每个寄存器中的适用位置“1”会使输出形式变为漏极开路。将每个寄存器中的适用位置“0”会将端口设置为CMOS输出。

9.2.3 驱动能力

RA2A1产品可以使能驱动能力输出,其驱动能力可设为低或中驱动能力输出。其他RA2产品无此功能。

• 驱动能力的切换由每个端口mn引脚功能选择 (PmnPFS) 寄存器中的驱动能力控制寄存器 (DSCR) 位控制。

• 复位后,会将所有DSCR寄存器清零,因此会将所有引脚设置为低驱动能力输出。设置“00”以外的值会更改所选引脚的输出的驱动能力。

• 引脚的最大总输出因产品及封装而异。具体请参见MCU硬件手册“电气特性”章节的内容。

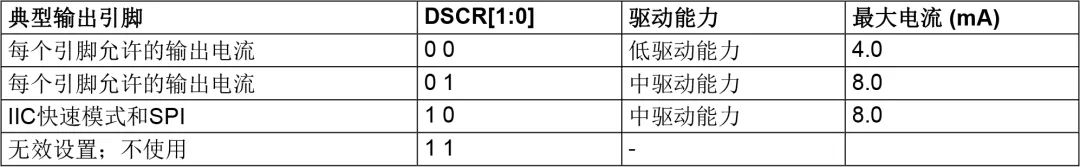

• 驱动能力的差异如下所示。实际输出电流会因产品和引脚类型而有所不同。详细信息请参见MCU硬件手册。

表10. 引脚驱动能力

输出驱动能力可能会对电路板设计的整体性能造成重大影响。为每个输出选择驱动能力时,应考虑以下几点:

• 建议首先将所有引脚设置为低驱动能力(默认)并评估性能。

• 根据电路板布局的不同,驱动能力设置为中或高的引脚可能会产生较高的EMI辐射。

• 较长的走线可能需要更高的驱动能力,才能使信号正确传播到接收器。

9.3 设置和使用端口外设功能

端口mn引脚功能选择寄存器 (PmnPFS) 用于配置每个端口的特性。PSEL 位用于选择为每个端口选择的外设功能。

• 由于大多数引脚具有多种功能,因此RA2 MCU提供了引脚功能控制寄存器 (PmnPFS),可用于更改分配给引脚的功能。

• 每个引脚都有自己的PmnPFS寄存器。

• 每个PmnPFS寄存器都允许将引脚用于外设功能(PSEL位)、用作IRQ输入引脚(ISEL位)或用作模拟输入引脚(ASE位)。如果ASEL位置“1”(将引脚用作模拟输入引脚),则应将该引脚的PMR位置1以用于GPIO,并将该引脚的PDR位置1以用于输入。

• 请参见《硬件手册》中“I/O端口”一章的“每种产品的外设选择设置”部分。

• 为了确保外设引脚上没有非预期的边沿输入或输出,确保在修改引脚的PmnPFS寄存器之前将目标引脚的端口模式控制 (PMR) 位清零。

• 复位后,所有PmnPFS寄存器均受到写保护。为了对这些寄存器执行写入操作,必须首先使用写保护寄存器 (PWPR) 来使能写入。

• 设置PmnPFS寄存器时应格外小心,切勿将一个功能分配给多个引脚。用户不应这样做,但MCU允许上述操作。如果发生这种情况,则引脚上的功能将处于未定义状态。

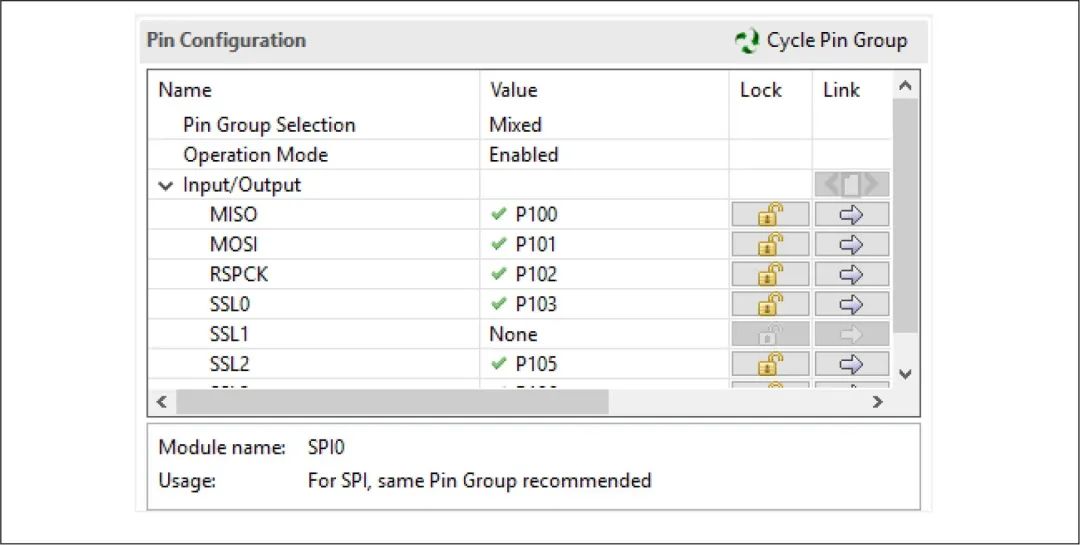

• 图20为使用Renesas FSP的引脚配置器使能QSPI引脚的示例。

图20. 使用Renesas FSP中的引脚配置器使能QSPI引脚

-

RA2快速设计指南 [3] 时钟电路2023-10-24 1575

-

RA6快速设计指南 [14] I/O端口配置 (3)2023-07-05 1837

-

RA6快速设计指南 [13] I/O端口配置 (2)2023-07-03 2148

-

RA2 MCU ADC转换时间测试方法2023-05-24 1156

-

RA2快速设计指南 [9] I/O端口配置(3)2023-04-14 1869

-

RA2快速设计指南 [7] 寄存器写保护和I/O端口配置2023-04-10 2603

-

RA2快速设计指南 [6] 存储器2023-04-06 2234

-

FPB-RA2E2-快速入门指南2023-01-11 525

-

如何将引脚RA2用于其他I/O或只是输入?2019-10-29 2584

全部0条评论

快来发表一下你的评论吧 !