通过自举扩展运算放大器工作范围

描述

当现成的运算放大器(op amp)不能提供特定应用所需的信号摆幅范围时,工程师面临两种选择:使用高压运算放大器或设计分立解决方案,不过这两种选择的成本可能都很高。

对许多应用来说,第三种选择——自举——可能是比较廉价的替代方案。除了动态性能要求极为苛刻的应用,自举电源电路的设计是相当简单的。

自举简介

常规运算放大器要求其输入电压在其电源轨范围内。如果输入信号可能超过电源轨,可以通过电阻衰减过大输入,使这些输入降至电源范围以内的电平。这样处理并不理想,因为它会对输入阻抗、噪声和漂移产生不利影响。同样的电源轨也会限制放大器输出,闭环增益的大小存在一个限值,以避免将输出驱动到饱和状态。

因此,如果要求处理输入和/或输出上的大信号偏离,则需要宽电源轨和能在这些电源轨上工作的放大器。ADI 的 24V 至 220V 精密运算放大器 ADHV4702-1 是适合这种情况的出色选择,不过自举低压运算放大器也能满足应用要求。是否使用自举主要取决于动态要求和功耗限制。

自举会创建一个自适应双电源,其正负电压不是以地为基准,而是以输出信号的瞬时值为基准,有时称之为飞轨(flying rail)配置。在这种配置中,电源随着运算放大器的输出电压(VOUT)上下移动。因此,VOUT始终处于中间电源电压,并且电源电压能够相对于地移动。使用自举可以非常容易地实现这种自适应双电源。

实际上,自举必须符合一些准则,有些准则微不足道,但没有一个准则是特别麻烦的。如下是最基本的准则:

-

输出负载不得过大。

-

响应速度不得低于运算放大器的压摆率。

-

必须能处理所需的电压水平和相关的功耗。

工作原理

飞轨概念是指正负电源轨连续调整,使其电压始终关于输出电压对称。这样,输出始终位于电源范围内。

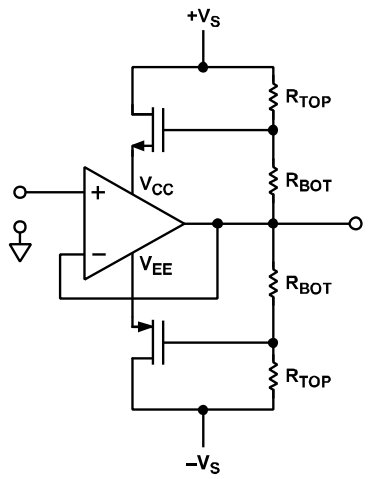

电路架构包括一对互补分立晶体管和一个阻性偏置网络。NPN 发射极(或 N 沟道 MOSFET 的源极引脚)提供 VCC,PNP 发射极(或 P 沟道 MOSFET 的源极引脚)用作 VEE。晶体管被偏置,使得所需的电源电压出现在放大器的+VS和–VS引脚上,这些电压通过电阻分压器从高压电源获得。图 1 显示了简化高压跟随器原理图。

图 1. 简化高压跟随器原理图

理论上,自举可以为任何运算放大器提供任意高的信号顺从电压。而在实际上,电源调整比例越大,动态性能越差,因为运算放大器的压摆率限制了电源对动态信号的响应速度。放大器在最大额定电源电压或接近该电压下工作时,电源引脚为跟上动态信号而需要横越的范围最小。当运算放大器在接近其最高额定电源电压下工作时,其他误差源(如噪声增益)也会降低。

不需要电源移动很远(或非常快)的低频和直流应用,是自举的最佳候选应用。因此,高压放大器能提供比动态特性相当的低压放大器更好的动态性能,尤其是当二者均偏置为各自的最大工作电源电压并且自举到相同信号范围时。自举也会影响直流性能,因此在直流精度和高电压两方面均经过优化的运算放大器可提供自举配置能实现的最佳直流和交流性能组合。

采用ADHV4702-1 的范围扩展器设计

ADHV4702-1 是一款精密 220 V运算放大器。有了该器件,就不需要自举传统低压运算放大器,220 V以下信号范围的高压设计得以简化。如果应用需要更高电压,那么可以应用自举技术,轻松地将电路工作范围增加两倍以上。下面说明一个基于ADHV4702-1 的 500 V放大器设计示例。

电压范围

如上所述,扩展器电路的范围在理论上是无限的,但存在如下一些实际限制:

-

电源电压和电流额定值

-

电阻和场效应晶体管(FET)功耗

-

FET 击穿电压

直流偏置电平

首先,考虑提供给放大器的电源电压。任何在器件额定电源电压范围内的电压都有效。然而,功耗是基于所选择的工作电压在放大器和 FET 之间分配。对于给定的原始电源电压,运算放大器电源电压越低,FET 中的漏源电压(VDS)越高,功耗也相应地进行分配。应选择适当的运算放大器电源电压,从而以最有利于散热的方式在器件之间分配功耗。其次,使用下式计算将原始电源电压(VRAW)降低到放大器期望电源电压(VAMP)所需的分压比:

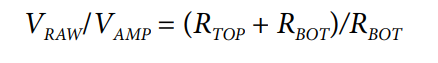

其中,RTOP为顶部电阻,RBOT为底部电阻。

对于下例,考虑运算放大器标称电源电压为±100 V。对于需要±250 V 摆幅范围的应用,通过下式计算分压比:

然后,使用便于获得的标准值电阻设计电阻分压器,尽可能接近地实现此分压比。请注意,由于涉及高电压,电阻功耗可能比预期要高。

静态功耗

对于所选电阻值,应选择能够应对相应静态功耗的电阻尺寸。相反,如果电阻的物理尺寸受限,应选择适当的电阻值来将散热限制在额定范围内。

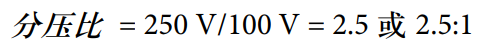

在该示例中,RTOP达到 150 V,RBOT达到 100 V。使用额定功率为 1/2瓦的 2512 电阻,设计必须将每个电阻器的功耗(V2/R)限制在 0.5 W 以下。计算每个电阻的最小值,如下所示:

将较高值电阻(45kΩ)作为功耗的限制因素,RBOT 值产生一个2.5:1 分压器,同时观测静态功耗限值为

其功耗为(100 V)2/30 kΩ = 0.33 W。

瞬时功耗

考虑到电阻的瞬时电压取决于放大器的输出电压以及电源电压,本例中任何时刻每个分压器上的电压可能高达350 V(VCC = 250 V且 VOUT = –100 V)。正弦输出波形在 VCC和 VEE分压器中产生相同的平均功耗,但任何非零平均输出都会导致一个分压器的功耗高于另一个分压器的功耗。对于满量程直流输出(或方波),瞬时功耗为最大功耗。

在此示例中,为将瞬时功耗保持在 0.5 W 以下,每个分压器中两个电阻之和(RSUM)不得小于以下值:

因此,电阻比为 1.5:1(对于 2.5:1 分压器)时,各个电阻的最小值如下:

-

RTOP = 147 kΩ

-

RBOT = 98 kΩ

FET 选择

承受最坏情况偏置条件所需的击穿电压主要决定 FET的选择;当输出饱和,使得一个 FET 处于最大 VDS,另一个 FET处于最小 VDS 时,便可明白这一点。在前面的示例中,最高绝对 VDS 约为 300 V,即总原始电源电压(500 V)减去放大器的总电源电压(200 V)。因此,FET 必须承受至少 300 V电压而不被击穿。

功耗必须针对最坏情况 VDS 和工作电流来计算,并且必须选择指定在此功率水平下工作的 FET。

接下来考虑 FET 的栅极电容,因为它会与偏置电阻一起形成一个低通滤波器。击穿电压较高的 FET 往往具有较高的栅极电容,而且偏置电阻往往为 100 kΩ,因此不需要多少栅极电容就能显著降低电路的速度。从制造商的数据手册中获得栅极电容值,计算 RTOP和 RBOT并联组合所形成的极点频率。

偏置网络的频率响应必须始终快于输入和输出信号,否则放大器的输出可能超出其自身的电源范围。暂时偏离到放大器电源轨之外会有损坏输入的风险,而暂时饱和或压摆受限会有造成输出失真的风险。任何一种状况都可能导致负反馈暂时丢失和不可预测的瞬态行为,甚至可能因为某些运算放大器架构中的相位反转而闩锁。

性能

直流线性度

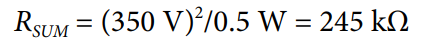

图 2 显示了增益误差与输入电压的关系(直流线性度),增益为 20,电源为±140 V。

图2. 增益误差与输入电压的关系

压摆率

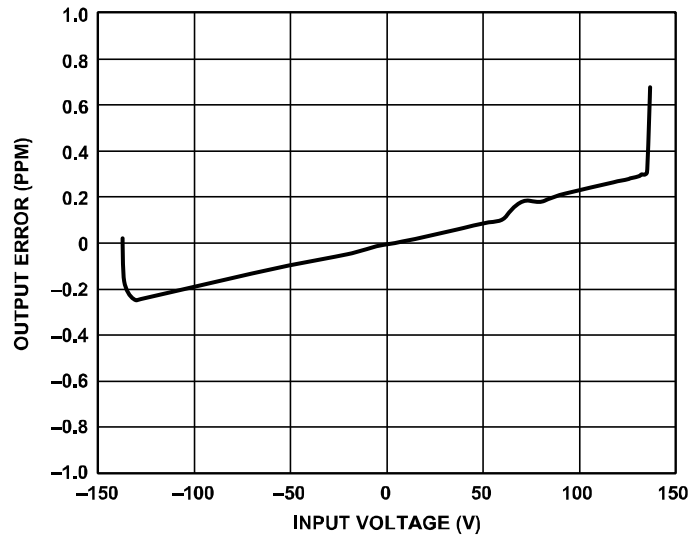

图 3 显示了压摆率曲线,增益为 20,电源为±140 V,测量值为 20.22 V/μs。

图 3. 压摆率

实现更高速度的权衡

功耗

如前所述,工作电压较高时,FET 的击穿电压(和相关的栅极电容)以及电阻值也必须较高。较高的电阻和电容值都会造成带宽降低,唯一可用的调整因素是电阻值。降低电阻值会提高带宽,但代价是功耗增加。

空间

低阻值、高功率的电阻尺寸较大,需占用较多电路板空间。以电容的形式在RBOT上增加一些引线补偿可以改善电路的频率响应。此电容与 RBOT和 RTOP电阻形成一个零点,抵消 FET栅极电容所形成的极点。极点和零点相消,因此可以选择更高阻值的电阻,从而降低直流功耗。

结论

在需要较高电压但使用典型高压运算放大器不经济的应用中,常常会让常规运算放大器自举。自举有其优点和缺点。还有一个选择,ADHV4702-1 提供一种高达 220 V的精密高性能解决方案,无需自举。但是,当信号范围要求超过 220 V时,该器件可以自举以处理超过标称信号范围两倍以上的电压,同时提供比自举低压放大器更高的性能。

原文标题:通过自举扩展运算放大器工作范围

文章出处:【微信公众号:亚德诺半导体】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- 亚德诺

-

运算放大器输入电压范围怎么算2023-12-26 3638

-

【世说芯品】通过自举扩展运算放大器工作范围2023-05-08 2409

-

通过自举扩展运算放大器工作范围2023-04-13 917

-

运算放大器需要考虑的电压范围2023-03-17 9166

-

扩展标准运算放大器的输入电压范围2023-01-12 3511

-

什么是运算放大器2022-11-08 1954

-

常规运算放大器的自举电路设计2021-09-13 3212

-

LTC3714:英特尔兼容、宽工作范围、带内部运算放大器的降压控制器数据表2021-05-25 765

-

AN-1593:通过自举扩展运算放大器工作范围2021-03-21 627

-

如何通过自举扩展运算放大器工作范围2019-03-03 6301

-

详解如何利用自举扩展运算放大器工作的范围2019-01-23 5415

-

运算放大器输入和输出共模与差分电压范围详解2018-09-21 13094

-

运算放大器输入和输出共模与差分电压范围2014-08-13 6065

-

运算放大器,运算放大器是什么意思2010-03-09 4138

全部0条评论

快来发表一下你的评论吧 !