RA2快速设计指南 [9] I/O端口配置(3)

描述

9. I/O端口配置(3)

9.4 设置和使用IRQ引脚

• 某些端口引脚可以用作硬件中断线(IRQ)。有关哪些引脚可用于您的MCU的信息,请参见《硬件手册》中“I/O端口”一章的“每种产品的外设选择设置”部分。

• 要将端口引脚设置为用作IRQ引脚,必须将其PFS寄存器中的中断输入功能选择位(ISEL)置“1”。

• 引脚可同时用于IRQ和外设功能。要使能此功能,需设置引脚的PFS寄存器的ISEL位和PSE位。

• 具有相同编号的IRQ功能必须在一个引脚上使能。

• IRQ引脚可以在检测到以下情况时触发中断:

⎯ 低电平

⎯ 下降沿

⎯ 上升沿

⎯ 上升沿和下降沿

使用IRQ控制寄存器(IRQCRi)选择要使用的触发器。

• 数字滤波可用于IRQ引脚。滤波器基于以四个可选时钟速率(PCLKB、PCLKB/8、PCLKB/32、PCLKB/64)之一进行的重复信号采样。它们可以滤除短脉冲:在特定滤波速率下,任何少于3个样本的高脉冲或低脉冲。滤波器可用于滤除这些线路中的振铃和噪声,但是由于速率过快而无法滤除诸如机械开关弹跳之类的长时间事件。使能滤波会给硬件IRQ线增加一小段响应延迟时间(滤波时间)。

• 可以针对每个IRQ引脚单独使能数字滤波。此过程通过设置每个IRQ的IRQCRi寄存器中的IRQ引脚数字滤波器使能(FLTEN)位来实现。

• 可为每个IRQ引脚单独配置数字滤波的时钟速率。此过程通过设置每个IRQ的IRQCRi寄存器中的IRQ引脚数字滤波器设置(FCLKSEL[1:0])位来实现。

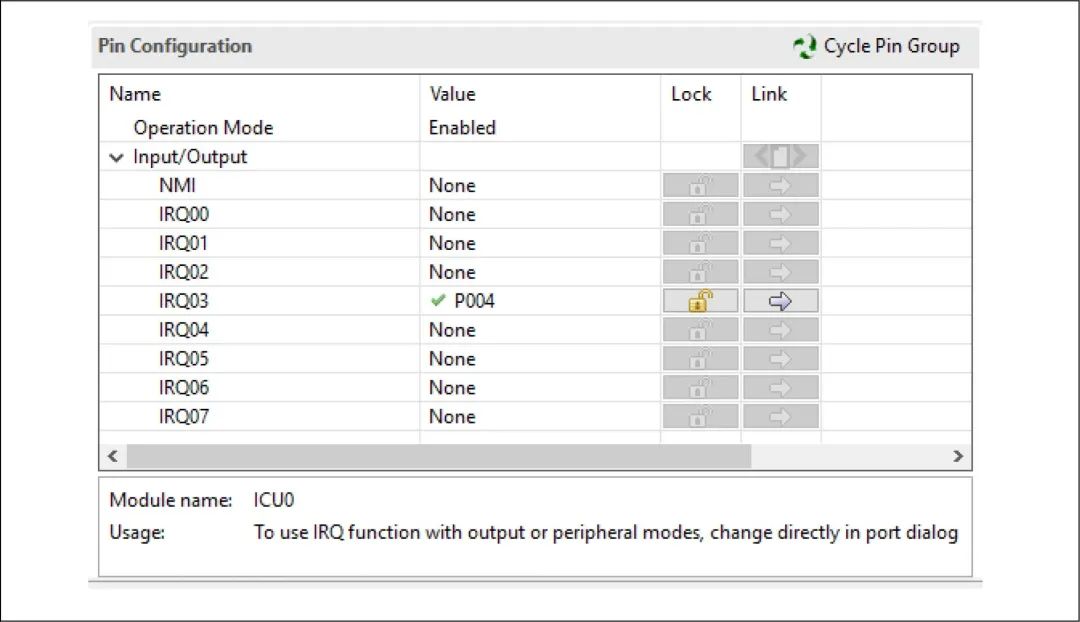

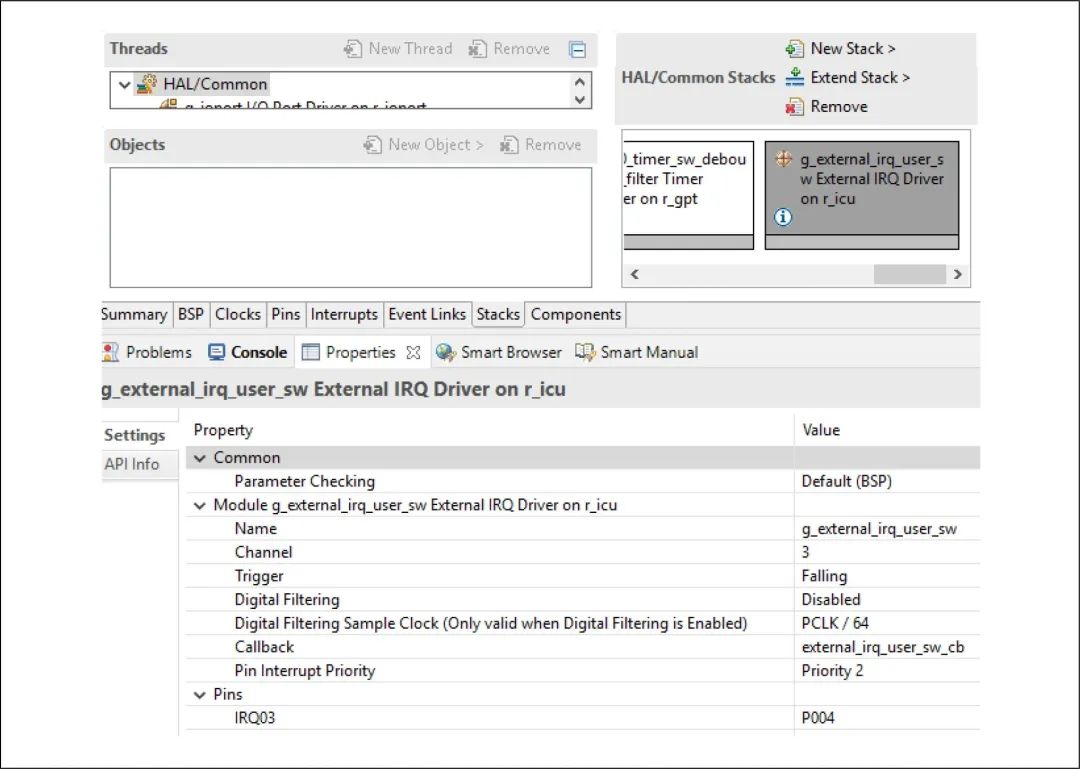

• 图21和图22给出了使用Renesas FSP使能和配置IRQ引脚的示例。

图21. 使用Renesas FSP配置器将P004配置为IRQ03

图22. 使用Renesas FSP配置器配置IRQ03

9.5 未使用引脚的处理

注:某些引脚需要特定的端接:有关具体建议,请参见《硬件手册》中的“未使用引脚的处理”部分。

悬空的未使用引脚会消耗额外的功率,并使系统更容易受到噪声问题的影响。使用下面详述的方法之一对未使用的引脚进行处理:

1

第一种选择是将引脚设置为输入(复位后的默认状态),然后使用电阻将其连接至Vcc或Vss。不同的连接方法对MCU来说没有区别;但是,从系统噪声的角度来看,有的方法可能更具优势。Vss可能是最典型的选择。避免将引脚直接连接到Vcc或Vss,因为对端口的方向寄存器(用于将端口设置为输出)执行意外的写入操作可能会导致输出短路。

2

第二种方法是将引脚设置为输出。无论是将引脚电平设置为高还是低都无关紧要;但是,将引脚设置为输出并将输出设置为低电平会在内部将引脚连接至接地层。这可能有助于解决整个系统的噪声问题。将未使用的引脚设置为输出有一个缺点,即必须通过软件控制来完成端口配置。在将方向寄存器设置为输出前MCU一直保持在复位状态时,该引脚将为悬空输入,可能会消耗额外的电流。如果可以接受在此期间消耗额外的电流,则该方法可消除第一种方法所需的外部电阻。

3

将引脚保留为输入并使用外部电阻将它们处理的一种变化方式是使用MCU多个端口上的内部上拉电阻。这与将引脚设置为输出有相同的限制(需要程序来设置端口),但是由于产品不会驱动引脚,因此确实可以减少因引脚意外接地、短接到相邻引脚或Vcc而产生的影响。

9.6 不存在的引脚

每个RA2 MCU系列都有多种封装尺寸,总引脚数也各有不同。对于小于该MCU系列最大封装尺寸(通常为100引脚、64引脚、24引脚)的任何封装,需将PDR寄存器中不存在的端口的对应位置“1”(输出),并将PODR寄存器中不存在的端口的对应位置“0”。通过查看《硬件手册》中“I/O端口”部分的“I/O端口规范”表,用户可以查看每个MCU封装上可用的端口。例如,端口0上的P007和P008仅在100引脚封装中可用。请注意,不需要对不存在的引脚进行额外处理。

9.7 电气特性

常规GPIO端口通常需要CMOS电平输入(高电平≥ 0.8 * Vcc,低电平≤ 0.2 * Vcc)。某些GPIO端口具有施密特触发输入,在输入要求方面略有不同。有关更多信息,请参见《硬件手册》中的“电气特性”部分。

-

RA2快速设计指南 [3] 时钟电路2023-10-24 1509

-

RA6快速设计指南 [14] I/O端口配置 (3)2023-07-05 1778

-

RA6快速设计指南 [13] I/O端口配置 (2)2023-07-03 2087

-

RA2 MCU ADC转换时间测试方法2023-05-24 1109

-

RA2快速设计指南 [11] 外部总线、SDADC24和OPAMP2023-04-19 1943

-

RA2快速设计指南 [8] I/O端口配置(2)2023-04-12 2130

-

RA2快速设计指南 [7] 寄存器写保护和I/O端口配置2023-04-10 2543

-

RA2快速设计指南 [6] 存储器2023-04-06 2118

-

如何将引脚RA2用于其他I/O或只是输入?2019-10-29 2577

-

PIC18F46J50来自RA1和RA2的奇数输出2019-05-10 1623

全部0条评论

快来发表一下你的评论吧 !