EDA工具里的功耗是怎么计算出来的?

电子说

1.4w人已加入

描述

在当下的芯片设计中,工艺越先进,芯片规模越大,功耗就越发敏感,降低功耗的诉求越来越紧迫。

功耗优化一定是建立在计算和数据的基础上的。那么对于EDA而言,功耗是怎么算出来的呢?今天,就让小编带领大家一起从EDA的视角,来洞察功耗计算的零零总总。

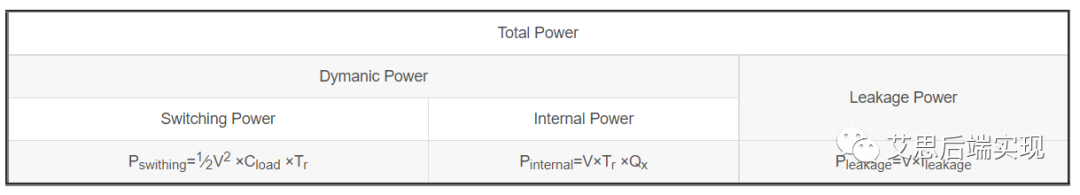

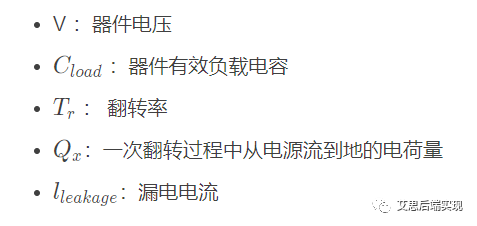

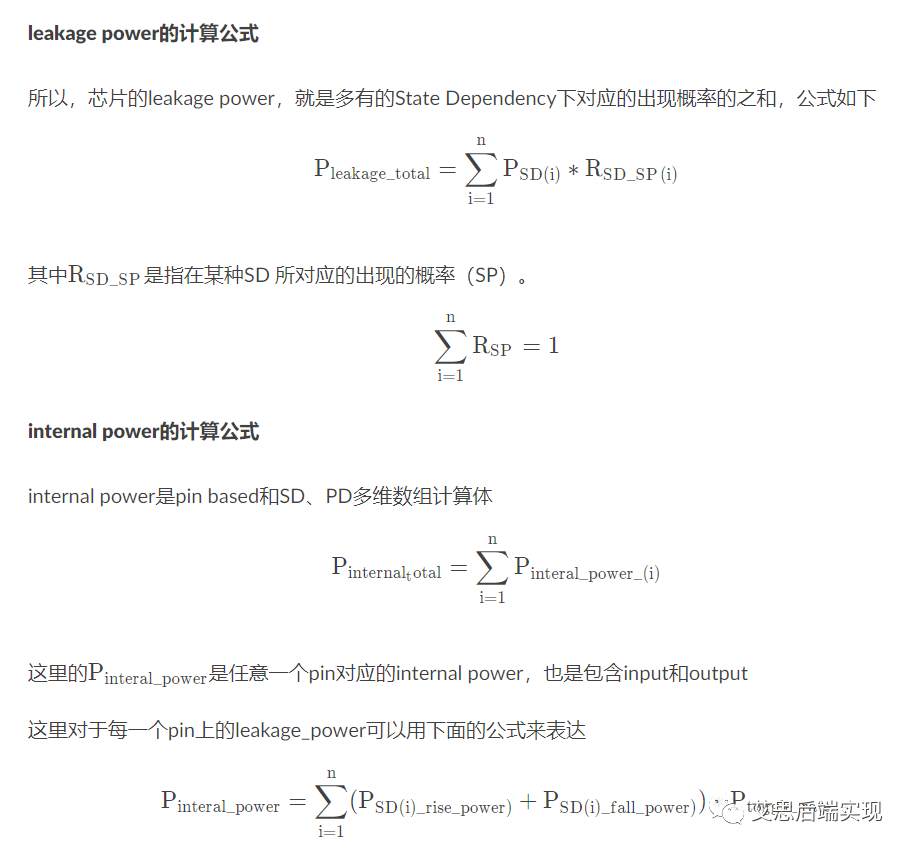

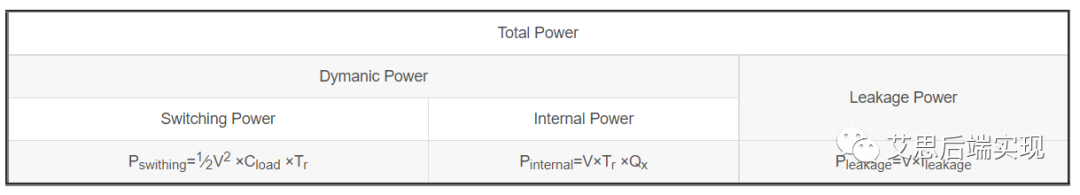

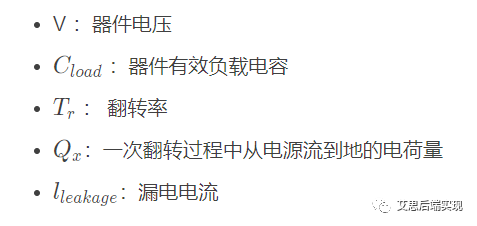

开篇之前,先复习一下功耗的计算公式: 注解

注解

注释:SDPD是一种瞬态值。在芯片常规的工作中,某一时刻,芯片是某一种固定的SDPD,所以一个芯片的实际工作状态(功耗)是由各种SDPD按照出现的比率描述的一个完备值(各种SDPD出现概率总和是100%)

注释:SDPD是一种瞬态值。在芯片常规的工作中,某一时刻,芯片是某一种固定的SDPD,所以一个芯片的实际工作状态(功耗)是由各种SDPD按照出现的比率描述的一个完备值(各种SDPD出现概率总和是100%)

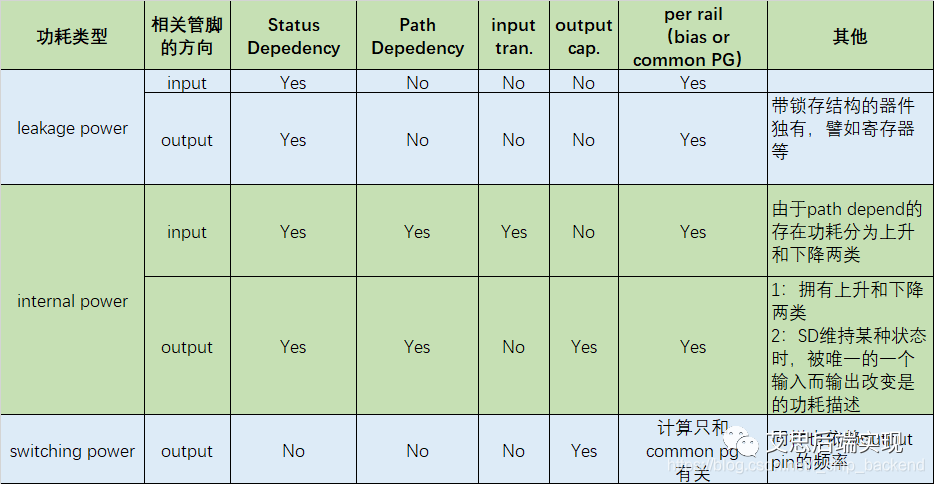

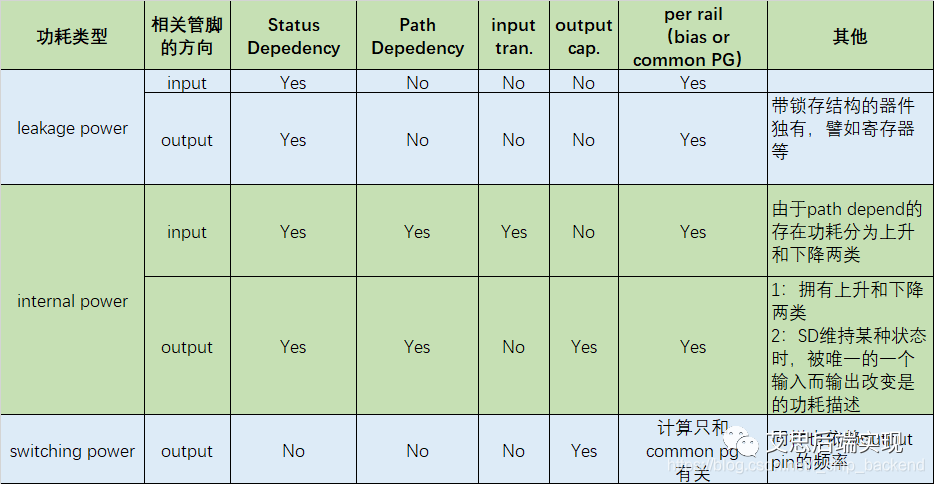

据上,器件的功耗的相关性可以用如下的表格来归类

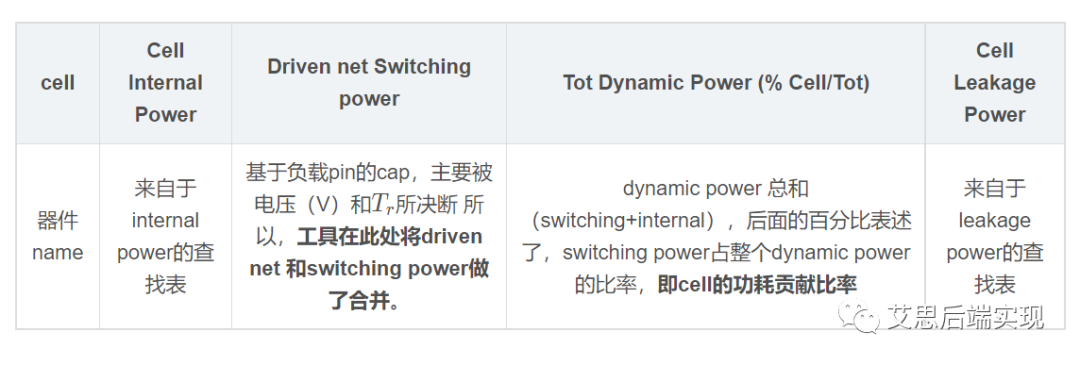

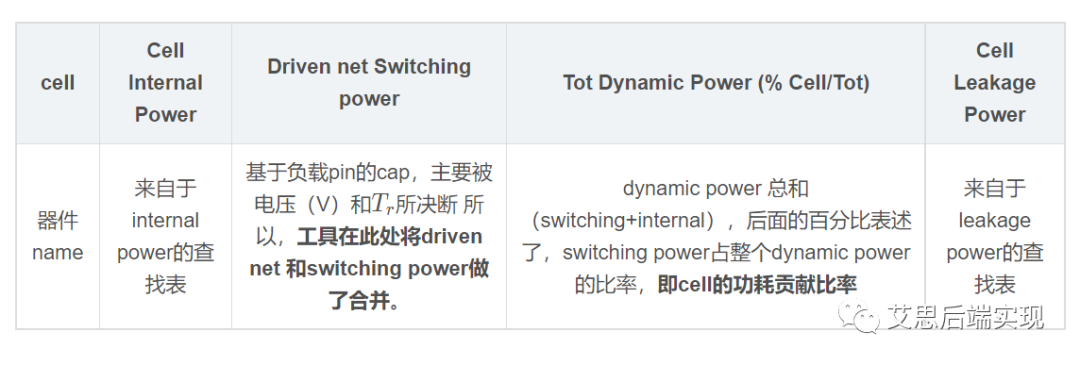

EDA工具提供了相应的信息和抽取方式来拟合library的描述。以常用的DC工具里的

表头解析: DC也会把器件分类进行功耗报告打印:

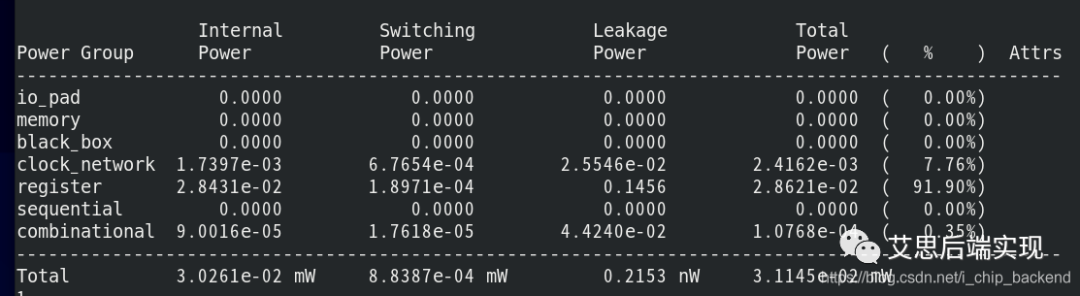

DC也会把器件分类进行功耗报告打印:

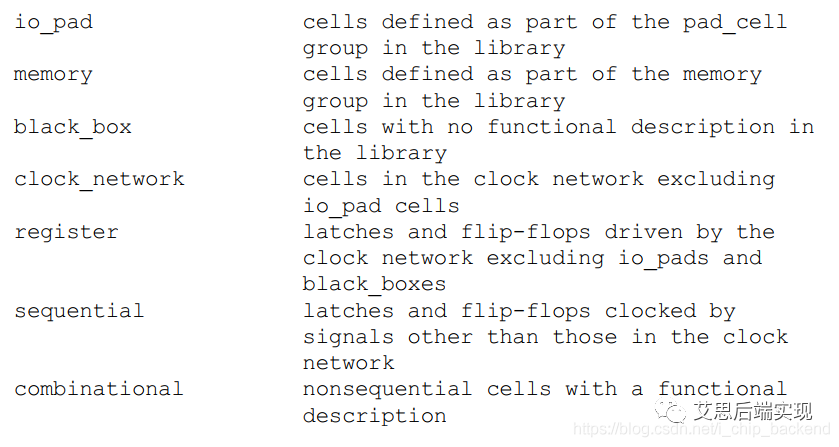

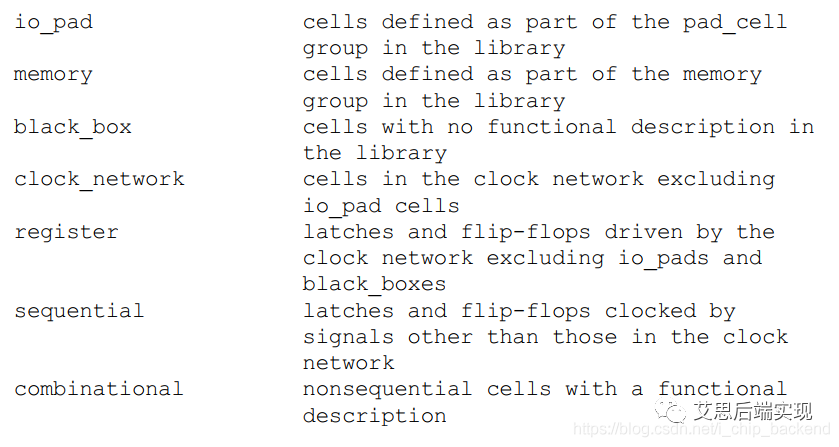

对于器件的分类方法见下表:

通常,

通常,

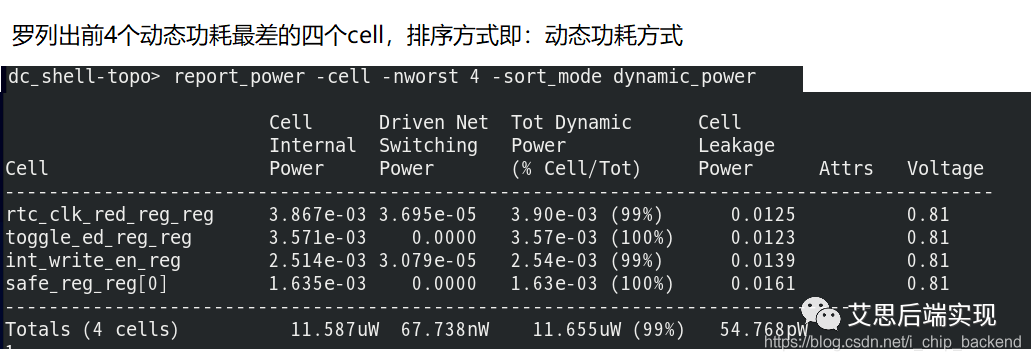

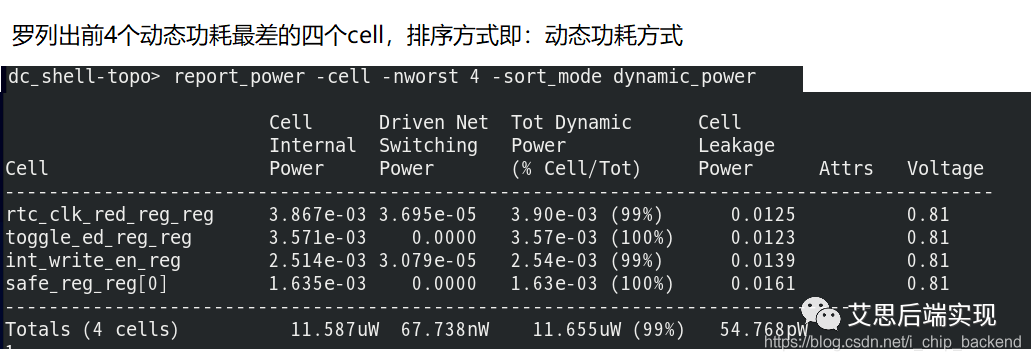

但是通常不太会这么做,因为去看每一个cell或者net的功耗意义并不很大,反而是找到芯片里边的最差功耗的cell或者net会比较有趣(设计里的功耗大户)。

譬如关心cell的动态功耗,这时可以使用下列命令来罗列:

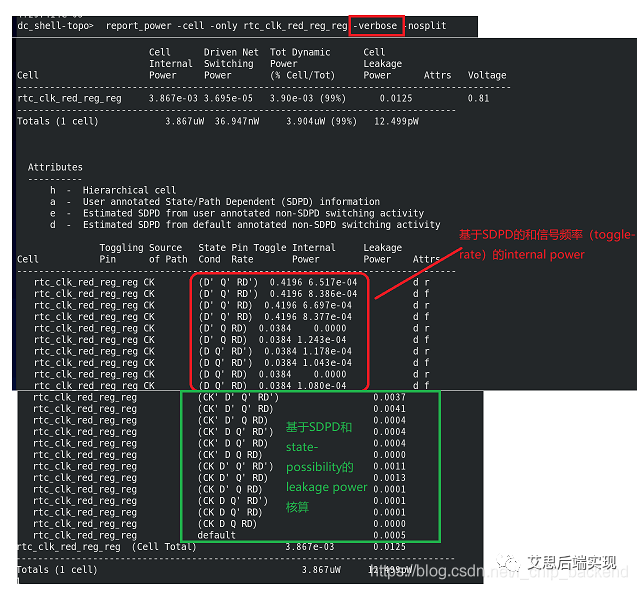

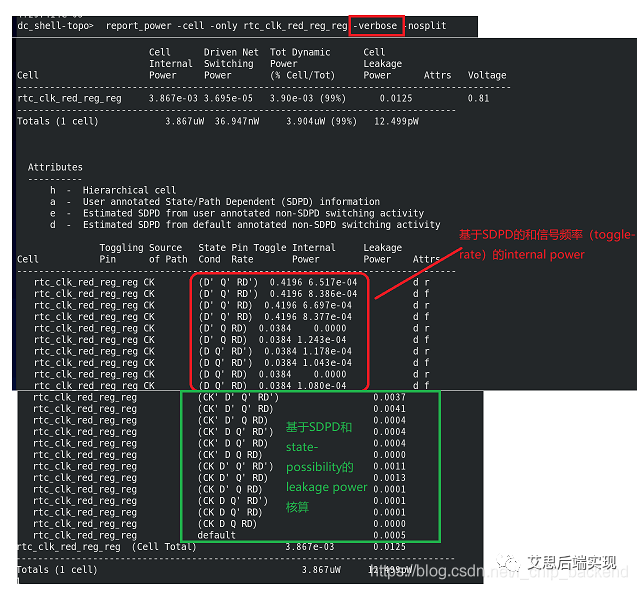

如果用户对功耗最大的cell比较感兴趣,可以使用-verbose的选项

罗列出更多的细节:

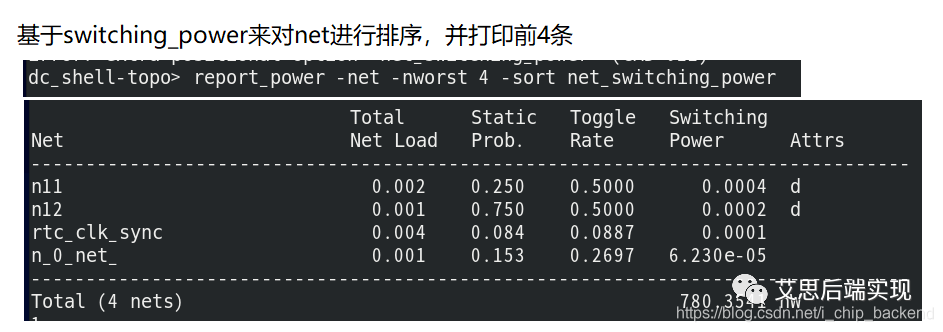

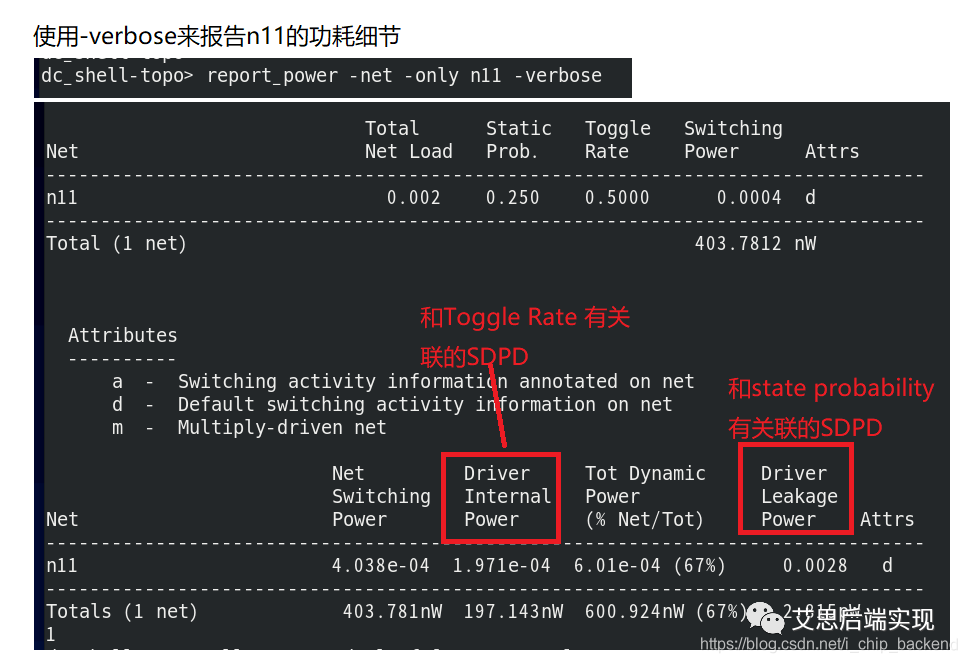

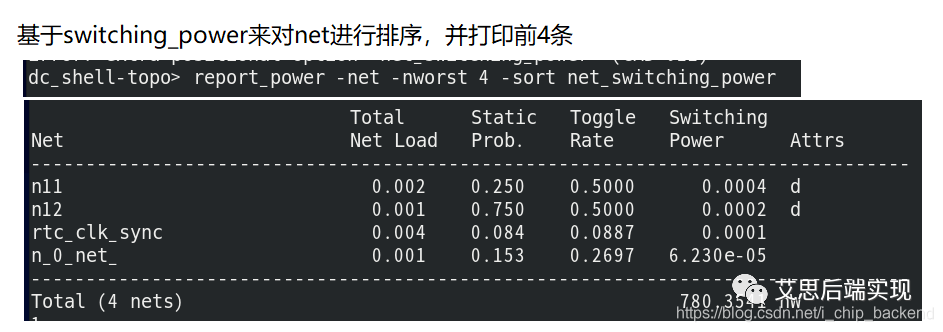

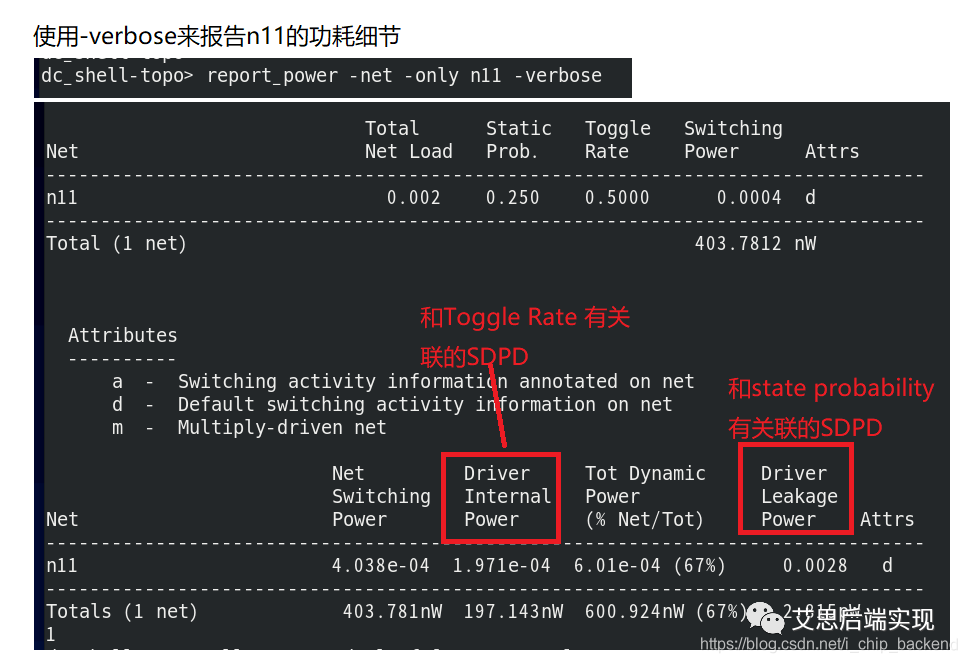

类似的也可以针对net类型进行sort、verbose的报告。

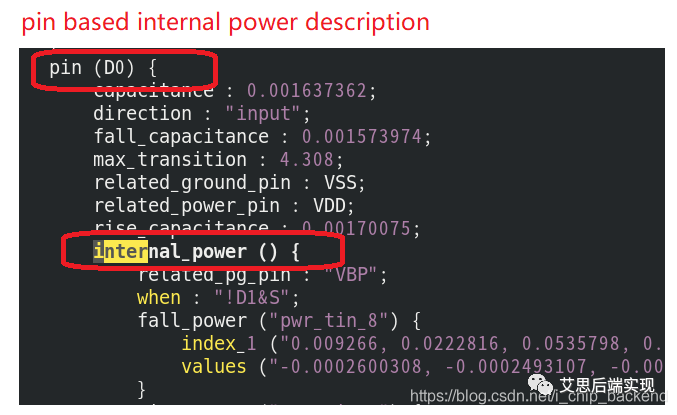

对于internal power,其在在library里的描述是pin based的

在

在 可以看出,EDA工具为了简化对功耗的核算,使用了归一化的操作,这样可以大大减少报告数量和歧义,这个对library的诉求也是得到了一致。

在上文提到一个更为精准化的描述方式,SDPD (Status Dependency Path Dependency),这个对于功耗计算有实际的影响。那么为何在功耗的计算里边会有这个SDPD呢?SDPD又是通过怎么样的方式影响功耗计算呢?一起打开工艺库的信息一探究竟吧!

可以看出,EDA工具为了简化对功耗的核算,使用了归一化的操作,这样可以大大减少报告数量和歧义,这个对library的诉求也是得到了一致。

在上文提到一个更为精准化的描述方式,SDPD (Status Dependency Path Dependency),这个对于功耗计算有实际的影响。那么为何在功耗的计算里边会有这个SDPD呢?SDPD又是通过怎么样的方式影响功耗计算呢?一起打开工艺库的信息一探究竟吧!

花了一些时间一起学习了一下lib,看到这里,大家应该可以理解为什么工具需要使用SDPD的方式来核算internal和leakage的power了吧:所有的计算都是基于基础数据结构和类型

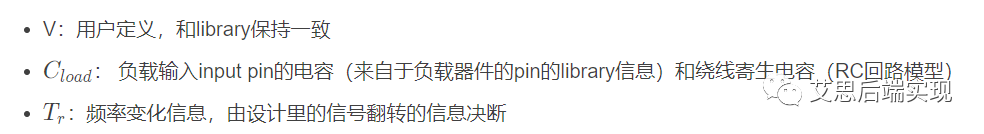

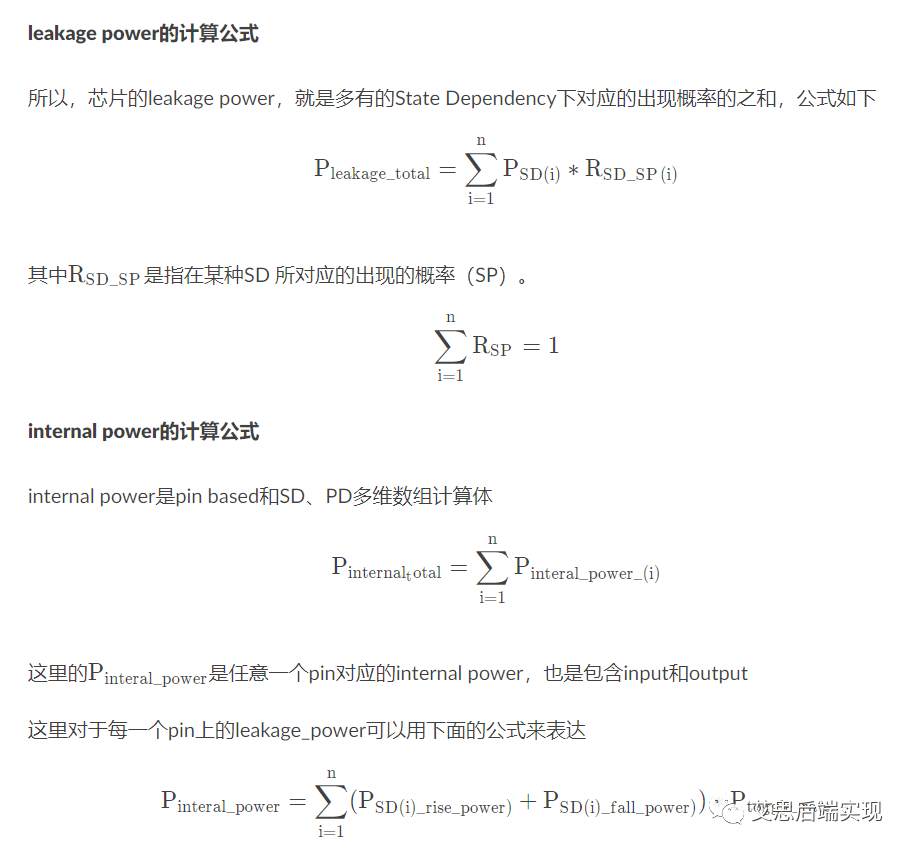

花了一些时间一起学习了一下lib,看到这里,大家应该可以理解为什么工具需要使用SDPD的方式来核算internal和leakage的power了吧:所有的计算都是基于基础数据结构和类型 所以,在对功耗的核算中,工具引入了下面两个重要的参数

所以,在对功耗的核算中,工具引入了下面两个重要的参数

拥有了计算功耗计算的公式,以及自研程序,功耗计算的大门也就向大家彻底打开了。

注解

注解

EDA对功耗评估的分类

基于上述功耗的计算理论,为了方便计算,EDA工具对功耗的评估分为如下几类

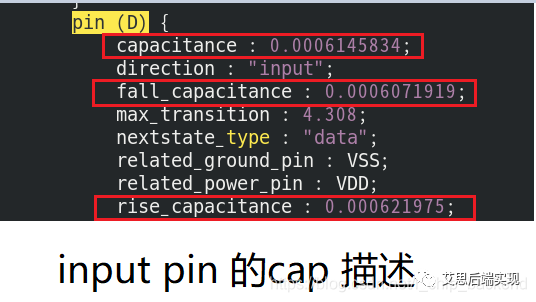

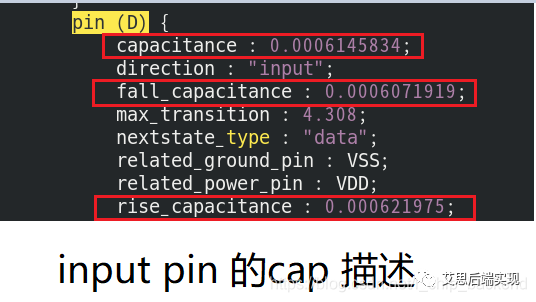

基于library非功耗的信息,计算功耗

基于SDPD的功耗查看

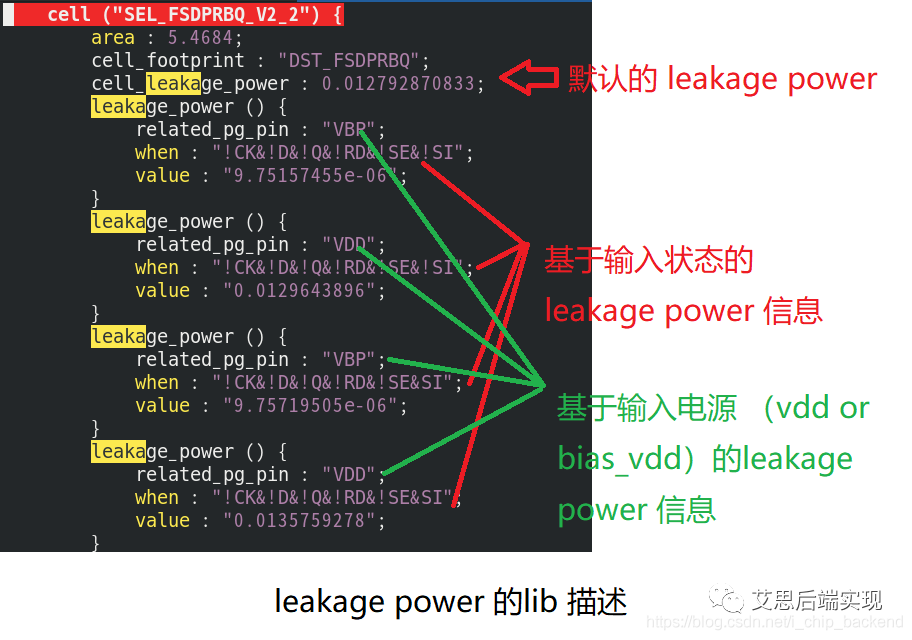

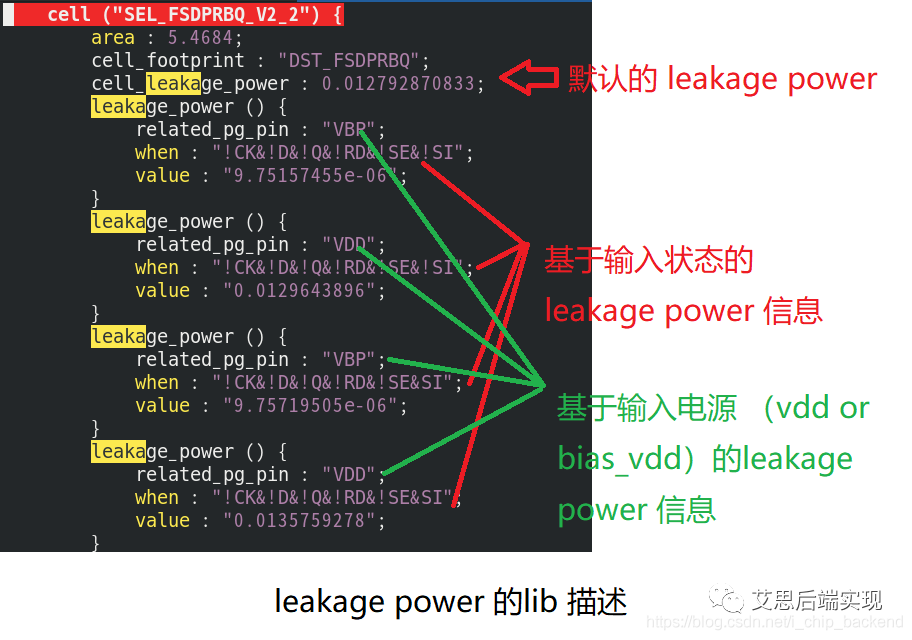

leakage power可以基于SDPD,直接查看library获取功耗- 基于器件输入状态进行功耗查看:器件状态决断SDPD (Status Dependency Path Dependency)

- library同时提供默认的leakage power的功耗信息

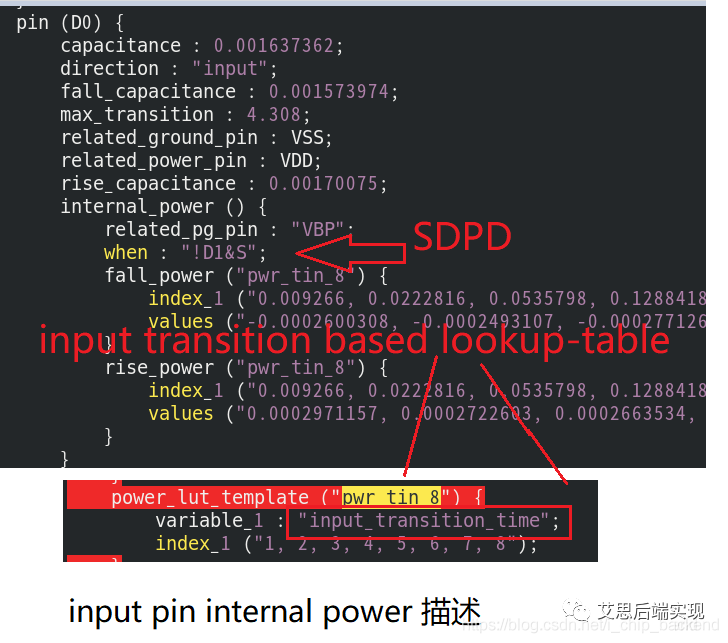

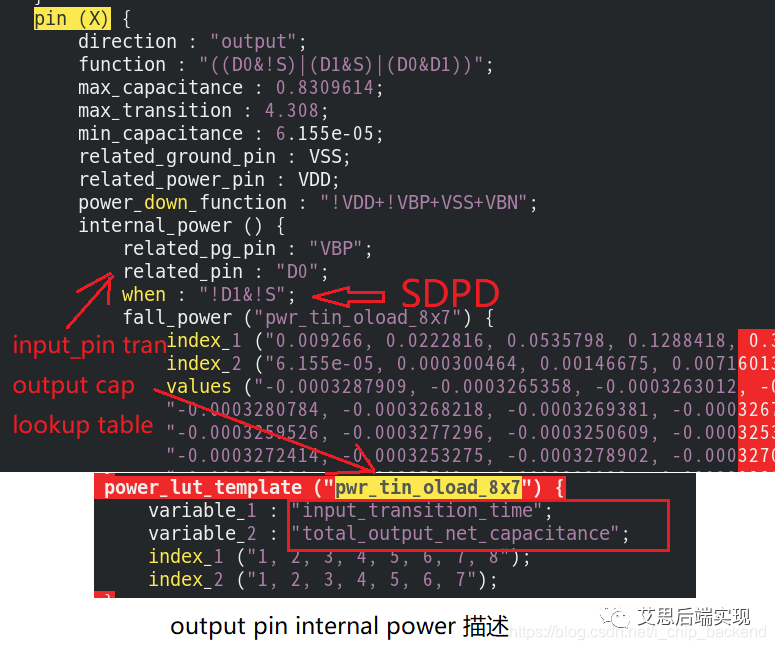

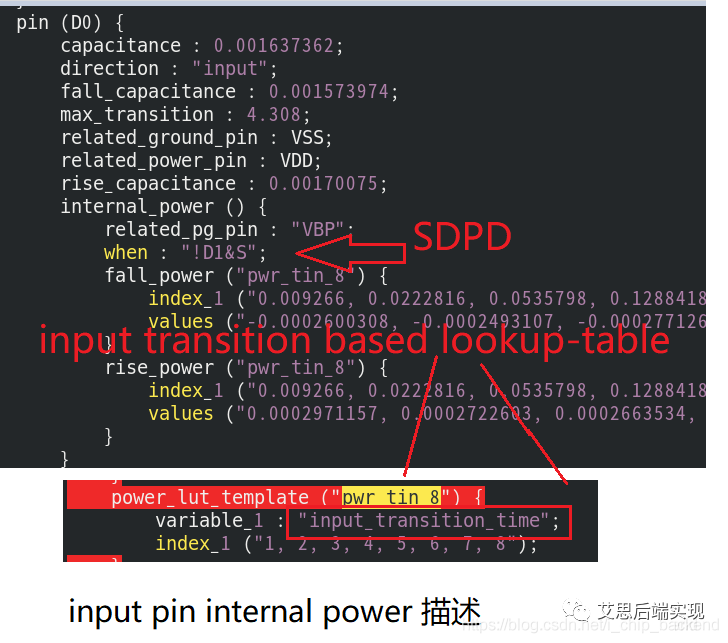

基于SDPD和pin的属性查找表

internal power可以基于SDPD和input/outputl 的RC属性查找表来获取- 基于SDPD的数据查询

- input pin:基于input transiton的查找表

- output pin:基于input transiton和output cap的查找表

- cel的internal power是所有pin在SDPD下的总和

注释:SDPD是一种瞬态值。在芯片常规的工作中,某一时刻,芯片是某一种固定的SDPD,所以一个芯片的实际工作状态(功耗)是由各种SDPD按照出现的比率描述的一个完备值(各种SDPD出现概率总和是100%)

注释:SDPD是一种瞬态值。在芯片常规的工作中,某一时刻,芯片是某一种固定的SDPD,所以一个芯片的实际工作状态(功耗)是由各种SDPD按照出现的比率描述的一个完备值(各种SDPD出现概率总和是100%)据上,器件的功耗的相关性可以用如下的表格来归类

EDA的功耗计算示例

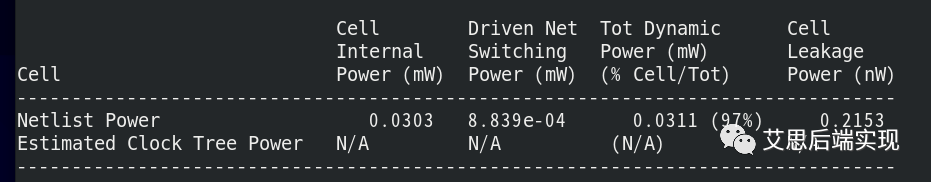

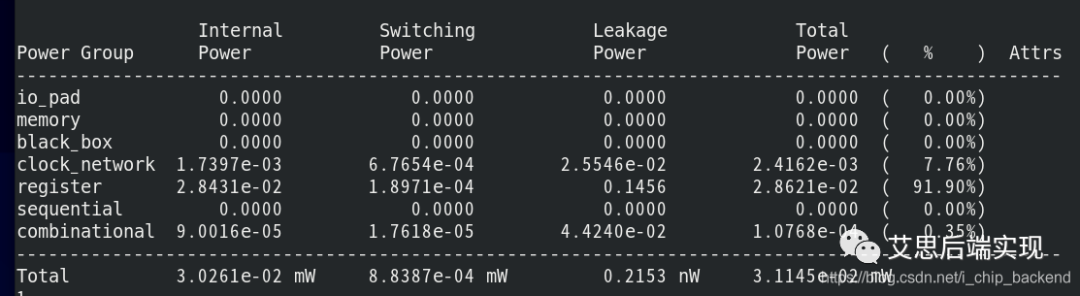

EDA工具提供了相应的信息和抽取方式来拟合library的描述。以常用的DC工具里的report_power命令为例,工具会罗列出下面的功耗信息:

DC也会把器件分类进行功耗报告打印:

DC也会把器件分类进行功耗报告打印:

对于器件的分类方法见下表:

通常,

通常,report_power默认行为是打印类似上述的芯片功耗的总和结果,这些都是每一个器件单独功耗的合计值,当然,也可以使用一些选项打印出某一个cell或者net或的功耗细节。但是通常不太会这么做,因为去看每一个cell或者net的功耗意义并不很大,反而是找到芯片里边的最差功耗的cell或者net会比较有趣(设计里的功耗大户)。

譬如关心cell的动态功耗,这时可以使用下列命令来罗列:

如果用户对功耗最大的cell比较感兴趣,可以使用-verbose的选项

罗列出更多的细节:

类似的也可以针对net类型进行sort、verbose的报告。

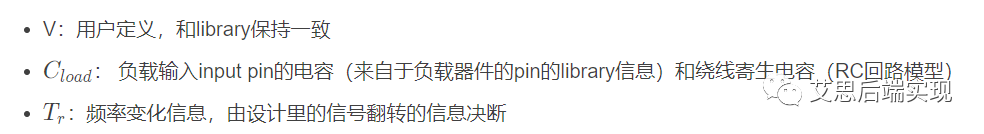

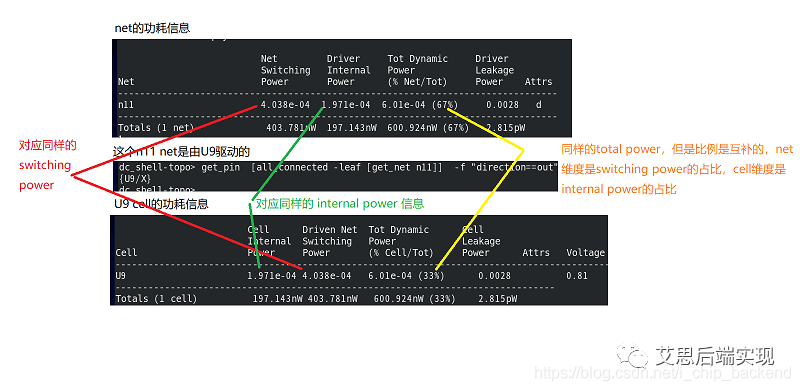

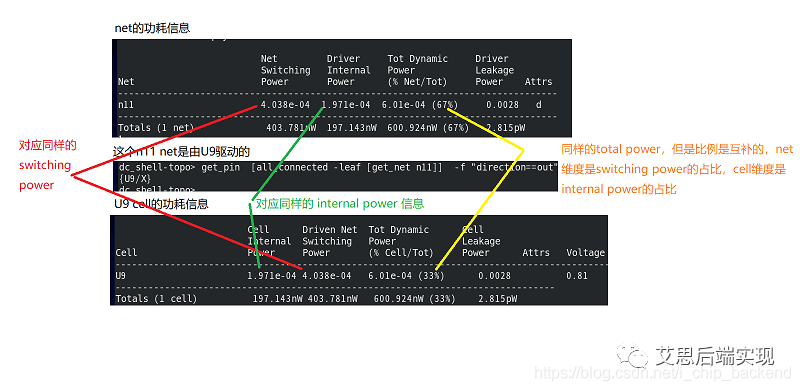

cell、net和pin的功耗归一化

从上文描述中可以看到,net会描述switching power,cell对标的则是internla power和leakage power。但是工具在产生报告的时候,无论是net还是cell都会把三类功耗打印完全,这里是使用output pin对应的net来做的cell、net归一化处理

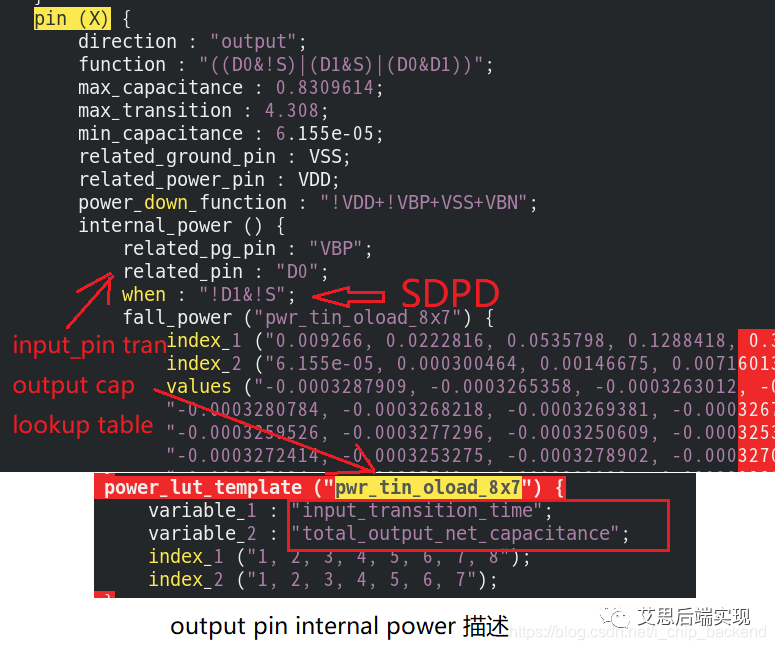

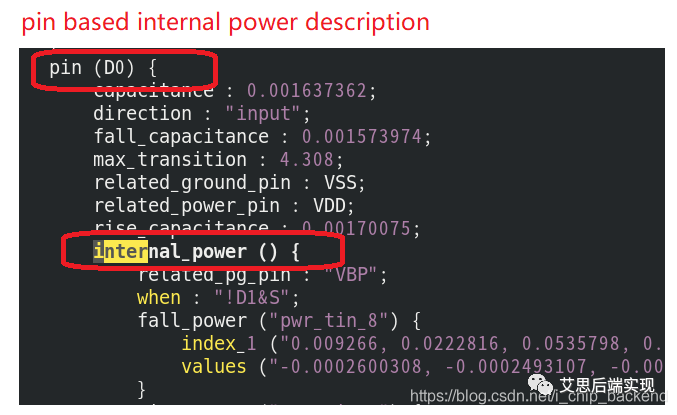

对于internal power,其在在library里的描述是pin based的

在

在report_power命令里边,internal power被整合为cell类型,但是本质上就是所有pin在SDPD下的总和表达。

为了方便表达,工具使用了上述三种对象对功耗进行了分拆,总结如下 可以看出,EDA工具为了简化对功耗的核算,使用了归一化的操作,这样可以大大减少报告数量和歧义,这个对library的诉求也是得到了一致。

在上文提到一个更为精准化的描述方式,SDPD (Status Dependency Path Dependency),这个对于功耗计算有实际的影响。那么为何在功耗的计算里边会有这个SDPD呢?SDPD又是通过怎么样的方式影响功耗计算呢?一起打开工艺库的信息一探究竟吧!

可以看出,EDA工具为了简化对功耗的核算,使用了归一化的操作,这样可以大大减少报告数量和歧义,这个对library的诉求也是得到了一致。

在上文提到一个更为精准化的描述方式,SDPD (Status Dependency Path Dependency),这个对于功耗计算有实际的影响。那么为何在功耗的计算里边会有这个SDPD呢?SDPD又是通过怎么样的方式影响功耗计算呢?一起打开工艺库的信息一探究竟吧!工艺库的功耗描述

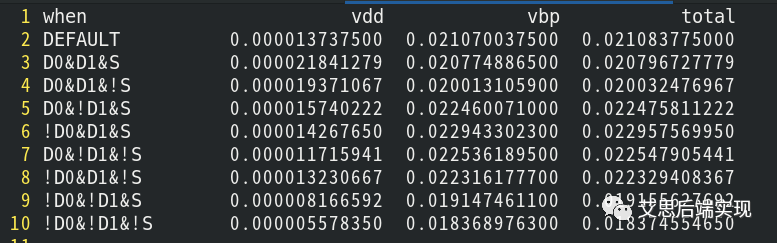

工艺库里的漏电功耗(leakage power)描述

打开一个MUX2 cell的lib描述,看看和leakage power相关的的信息cell ("SEL_MUX2_4") { cell_footprint : "DST_MUX2"; # default leakage power= default_VBP_leak + default_VDD_leak cell_leakage_power : 0.021083775; # 偏置电压对应的功耗 leakage_power () { related_pg_pin : "VBP"; value : "1.37375e-05"; # common-power leakage leakage_power () { related_pg_pin : "VDD"; value : "0.0210700375"; # SDPD !D0&!D1&!S leakage power @ VBP leakage_power () { related_pg_pin : "VBP"; when : "!D0&!D1&!S"; value : "5.57835028e-06"; # SDPD !D0&!D1&!S leakage power @ VDD leakage_power () { related_pg_pin : "VDD"; when : "!D0&!D1&!S"; value : "0.0183689763";

- 漏电电压是由所有的power rail 所构成:譬如这里就有bias和common的区分

-

SDPD是所有输入可能的描述 可以使用脚本快速进行抓取转成列表。

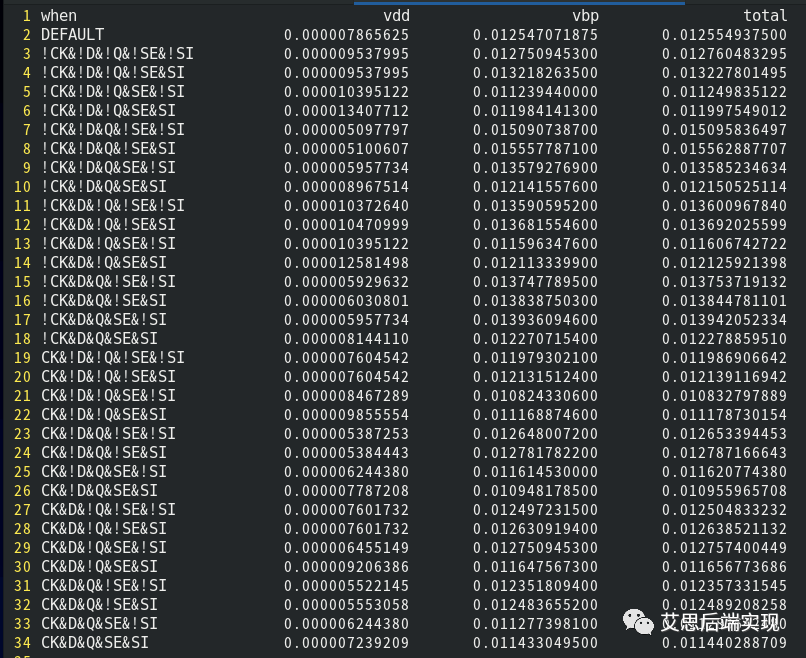

可以看到,这是一个三输入的器件,那么总计会有8中输入可能,lib的leakage的信息基于输入可能性的全完备罗列。 对于一个包含SI和SE的DFF,这里有CLK的器件,对于不同Q的输出,器件的状态也不一样,会导致漏电的不同,所以可以看到FF的漏电信息,包含的输出口Q的影响,这样总共就有4+1=5个管件的组合方式,亦即32中可能,加上默认,全备的漏电信息表格如下:

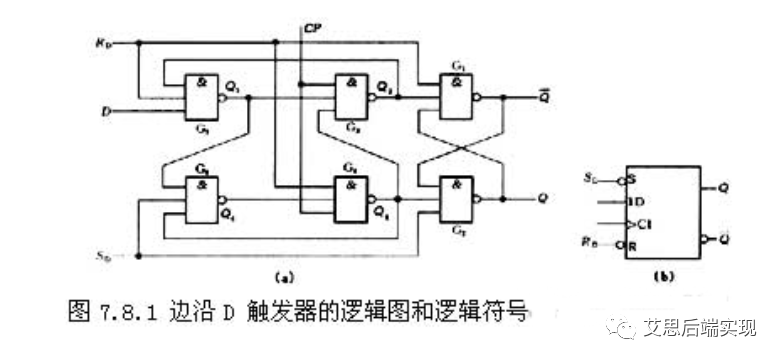

可以看到,这是一个三输入的器件,那么总计会有8中输入可能,lib的leakage的信息基于输入可能性的全完备罗列。 对于一个包含SI和SE的DFF,这里有CLK的器件,对于不同Q的输出,器件的状态也不一样,会导致漏电的不同,所以可以看到FF的漏电信息,包含的输出口Q的影响,这样总共就有4+1=5个管件的组合方式,亦即32中可能,加上默认,全备的漏电信息表格如下:  至于为何会有Q输出管教的信息来组合成为leakage power tabel,一起回顾一下大学课本里的下图就可以领略到其中的原理了:Q和!Q都会反接回来构成类似锁存的结构体:

至于为何会有Q输出管教的信息来组合成为leakage power tabel,一起回顾一下大学课本里的下图就可以领略到其中的原理了:Q和!Q都会反接回来构成类似锁存的结构体:  图片来自网络,侵删

图片来自网络,侵删

工艺库里的内部功耗(internal power)描述

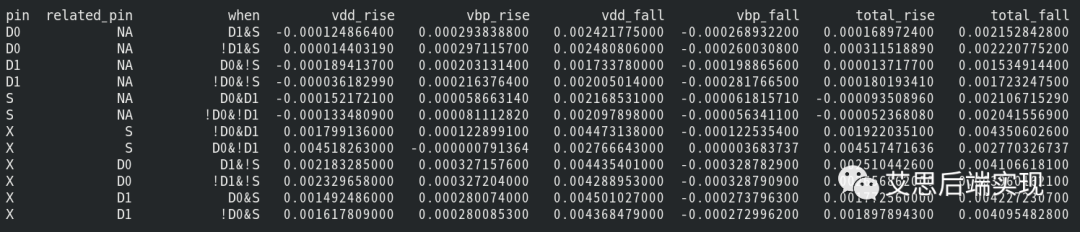

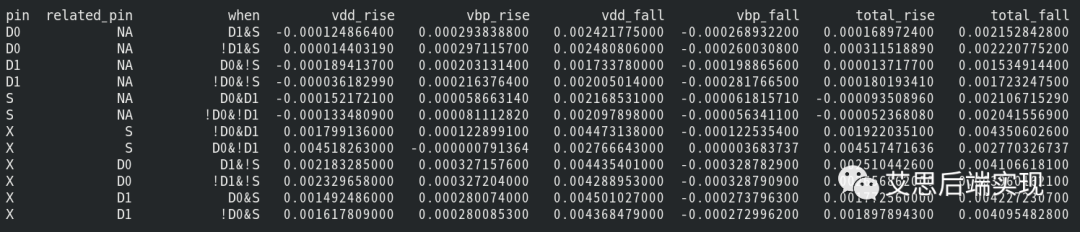

以MUX2 为例,一起看一下interenal power的描述:cell ("SEL_MUX2_4") { ...... pin (S) { capacitance : 0.002820029; direction : "input"; fall_capacitance : 0.002761232; max_transition : 4.308; related_ground_pin : VSS; related_power_pin : VDD; rise_capacitance : 0.002878826; internal_power () { # bias PG related internal_power description related_pg_pin : "VBP"; # condition when : "!D0&!D1"; fall_power ("pwr_tin_8") { index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308"); values ("-5.63411e-05, -5.540512e-05, -6.377697e-05, -4.595821e-05, -6.756144e-05, -6.15605e-05, -6.171516e-05, -6.163207e-05"); } rise_power ("pwr_tin_8") { index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308"); values ("8.111282e-05, 7.08698e-05, 5.968669e-05, 5.155256e-05, 5.807869e-05, 6.204414e-05, 6.182517e-05, 6.175735e-05"); } } internal_power () { # common PG related internal_power description related_pg_pin : "VDD"; # condition when : "!D0&!D1"; # the internal_power during pin S falling edge fall_power ("pwr_tin_8") { index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308"); values ("0.002097898, 0.00210684, 0.001989685, 0.002036636, 0.001995899, 0.001987284, 0.001991492, 0.002053458"); } # the internal_power during pin S rising edge rise_power ("pwr_tin_8") { index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308"); values ("-0.0001334809, -6.114718e-05, -0.000153519, -0.0001819992, -0.0002029397, -0.0002175415, -0.0002181976, } } } ...... pin (X) { direction : "output"; function : "((D0&!S)|(D1&S)|(D0&D1))"; max_capacitance : 0.8309614; max_transition : 4.308; min_capacitance : 6.155e-05; related_ground_pin : VSS; related_power_pin : VDD; power_down_function : "!VDD+!VBP+VSS+VBN"; internal_power () { related_pg_pin : "VBP"; # Path Dependency related_pin : "D0"; # Status Dependency when : "!D1&!S"; # X: falling edge power due to related D0 change. positive unate fall_power ("pwr_tin_oload_8x7") { index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308"); index_2 ("6.155e-05, 0.000300464, 0.00146675, 0.00716013, 0.0349531, 0.170628, 0.832941"); values ("-0.0003287909, -0.0003265358, -0.0003263012, -0.0003258171, -0.0003259071, -0.0003233576, -0.0003219219", ...... "-0.0003294999, -0.0003285813, -0.0003292956, -0.0003293134, -0.0003286557, -0.0003291086, -0.0003283838"); } # X: rising edge power due to related D0 change. positive unate rise_power ("pwr_tin_oload_8x7") { index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308"); index_2 ("6.155e-05, 0.000300464, 0.00146675, 0.00716013, 0.0349531, 0.170628, 0.832941"); values ("0.000327204, 0.000329085, 0.0003304601, 0.0003274369, 0.0003265309, 0.0003275536, 0.0003209762", ...... "0.0003299443, 0.000328975, 0.0003286823, 0.0003299806, 0.0003291929, 0.0003285925, 0.0003283199"); } } } ...... } 可以看到,internal power除过是status dependency,同时也是path dependency。基于internal power的特性,这里也同时需要考虑 input tran和output_cap的状态。 通过脚本抽取,可以看到如下特性:

- 输入pin:会对应一个rise和fall的internal power per rail。对应的,每一个input的internal power也是被其他输入pin的状态所影响。

- 输出pin:在一个input pin的path dependency的情况下,在其他的input pin的status dependency,这个唯一变化的输入pin的变化,会带来相应的rise和fall的internal power

工艺库里的功耗描述小结

上面的阐述比较多,为了方便大家阅读,以下面的表格做一个相关的小结: 花了一些时间一起学习了一下lib,看到这里,大家应该可以理解为什么工具需要使用SDPD的方式来核算internal和leakage的power了吧:所有的计算都是基于基础数据结构和类型

花了一些时间一起学习了一下lib,看到这里,大家应该可以理解为什么工具需要使用SDPD的方式来核算internal和leakage的power了吧:所有的计算都是基于基础数据结构和类型SDPD对于功耗计算的影响

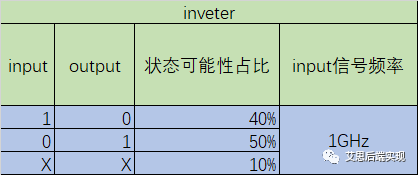

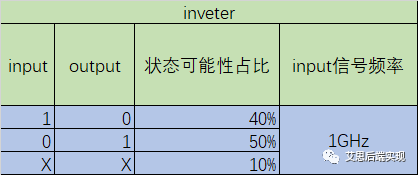

在实际的芯片当中,一个器件在不同时间的表现状态可以不同,这里就像一个真值表,假定设计里边有如下一个inverter器件的工作状态。 所以,在对功耗的核算中,工具引入了下面两个重要的参数

所以,在对功耗的核算中,工具引入了下面两个重要的参数- Status Possibility (SP): 各种状态的出现比率,通常以一个周期的高电平所占比率来体现,譬如一个占空比50%的时钟,那么他的SP就是0.5。这个参数会直接影响leakage pwoer,间接影响internal power

- toggle rate (TR):反转率,通常指一个单位时间(time unit)内信号的反转次数,包含上升沿和下加沿,譬如在一个以ns为单位时间的工艺里,1GHz的信号对应的toggle rate就是2。这个参数会直接影响internal power

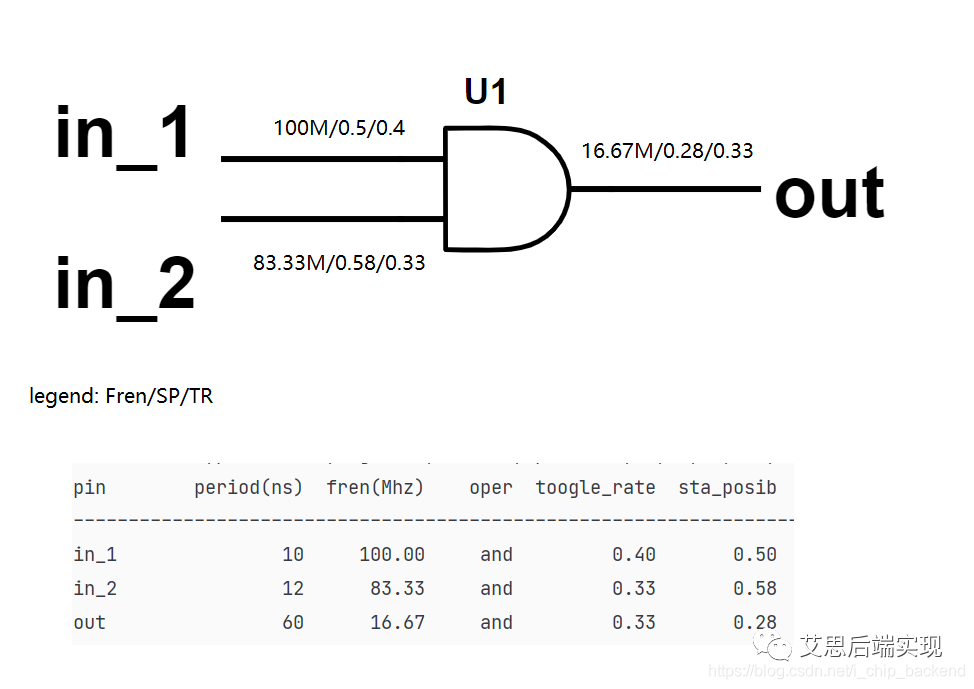

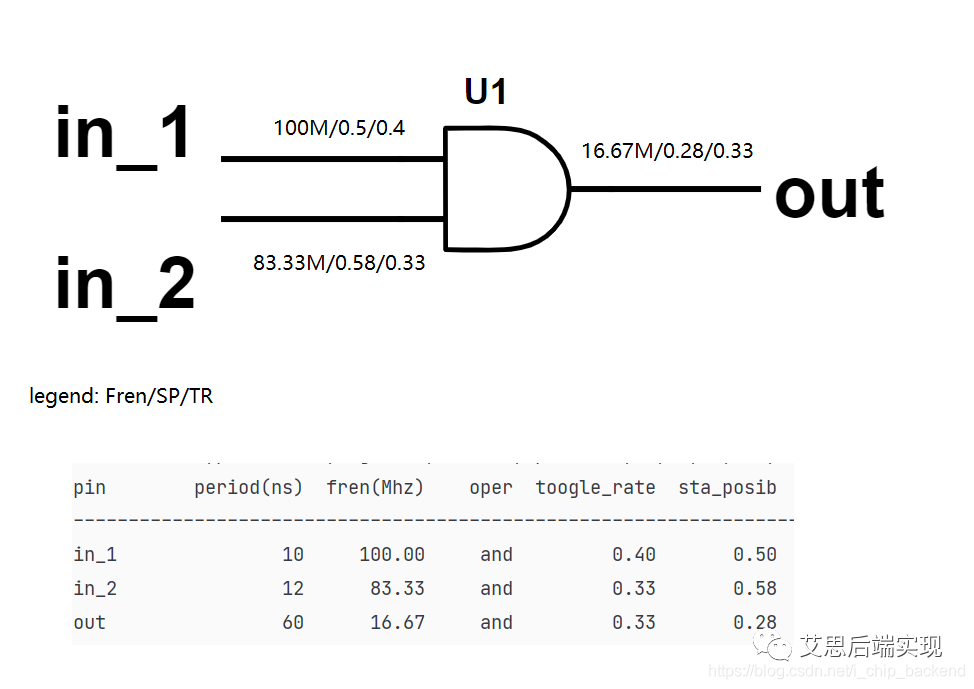

SP和TR计算示例

目前为止,有了TR和SP就可以展开对leakage_power和internal_power的计算。在实际的芯片里边,可以使用一些手段来计算器件的TR和SP,为此,笔者使用python完成了一个这样的一个功能:基于输入管脚对简单组合逻辑进行输出管脚的TR和SP的计算:

拥有了计算功耗计算的公式,以及自研程序,功耗计算的大门也就向大家彻底打开了。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

STM32F1 xcube cryptolib ECDSA计算出来的摘要值和外部验证工具计算出来的签名值对不上怎么解决?2025-03-07 418

-

dd马达偏差量怎么计算出来的2024-07-11 2113

-

IcalibrationFSP 0.0002这个值是怎么计算出来的?2023-12-25 562

-

op1177运放输入阻抗是怎么计算出来的啊?2023-11-28 781

-

求累加器B的结果是怎么计算出来的?2021-10-22 1982

-

请问Calibre电路版图W L是怎么各自计算出来的?2021-06-23 2026

-

PWM的占空比是怎么计算出来的?2020-08-04 4059

-

直流无刷电机的定子绕组绕多少匝是用什么公式计算出来的?2020-04-21 9402

-

最后一个字节的校验码是怎么计算出来的?2019-03-07 3464

-

这个电阻2.2如何计算出来的,oa ob 的最大电流是多少?2018-10-14 2543

-

请问信噪比是怎么计算出来的2018-09-13 6136

-

Apollo的三个问题和解答控制命令计算出来是发布给谁呢?2018-07-15 4816

-

电路是计算出来的2016-10-10 509

-

请老师指点我,附图中C点电压,A点电压是如何计算出来的2013-10-10 4601

全部0条评论

快来发表一下你的评论吧 !