解析PCIe第50万行代码的风格

描述

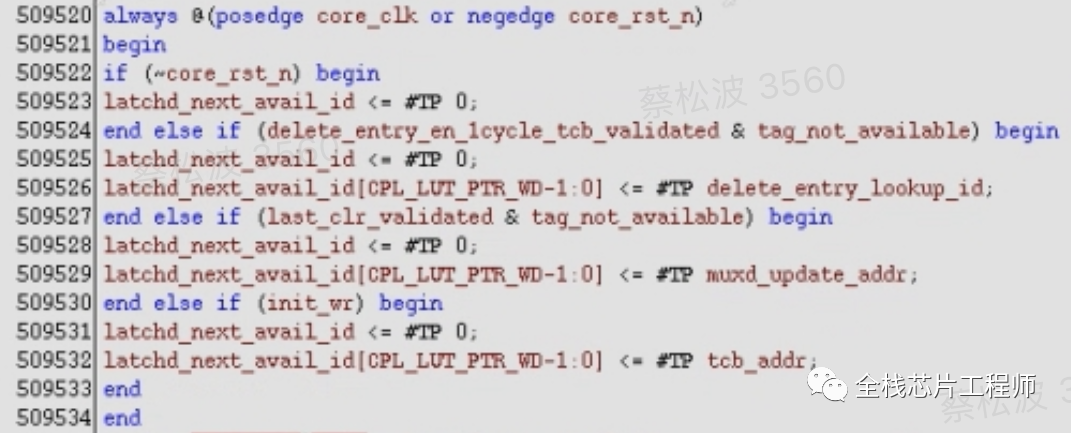

来,看看S家的第509525行PCIe代码,一个寄存器在一个触发信号里面赋值两次,第一句所有bit直接全部赋值0,第二句部分低bit赋值,信号本身是9:0,第二句赋值那个是6:0的宽度。尊贵的ICer,您觉得这样可以吗?

作为当代IC designer,看到这种代码风格首先视觉冲击就很大,辣眼睛。估计就没有做lint,是不是很像多驱动的罪名?跑一下lint看看报错情况。

但必须说明的是,这是S家的老版本代码了,硬核功能OK的,仿真行为也正确。所以这种代码风格的设计意图是后一句覆盖前一句,前一句先把所有bit赋0,后一句再部分低位bit赋值,那么各家综合工具编译会理解错设计者意图吗?个人强烈不推荐这种写法,虽然SV语法也支持这种,各家综合工具编译结果可能有偏差,况且前面的高位赋0,综合工具直接优化掉0的部分,那写出来干嘛?为了接口位宽不变,只是里面用的部分按参数定义位宽吗?还不如直接参数定义总位宽即可,这个就具体问题具体分析,小编造一个简单实例:

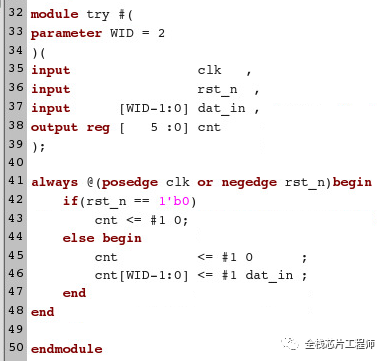

实践出真知,写一个代码实践下:

spyglass运行lint检查:

代码第45行报出来2个warning,我们来分别解析下两个warning:

(一)第一个warning:STARC05-2.2.3.3,用以发现initial value assignments to flip-flops in always constructs,我们知道,……下文请移步知识星球。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

向代码致敬,寻找你的第83行2018-05-04 2771

-

向代码致敬,寻找你的第83行!2018-05-07 2227

-

嵌入式C代码怎么实现?2020-03-18 1634

-

800万行代码的鸿蒙系统,在世界上处于什么水平?2020-09-29 3988

-

【HarmonyOS】800万行代码的鸿蒙系统,在世界上处于什么水平?2020-10-27 1963

-

阿里巴巴推出每秒撰写2万行广告文案的AI新工具2018-07-07 3552

-

微软发布了使用最多的应用程序之一——Windows 计算器的源代码2019-03-11 6162

-

涛思数据开源TDengine,10多万行C代码,登顶GitHub!2019-07-31 14169

-

移植了20万行代码才发现树莓派Pico双核MCU竟是三无产品?是真香还是真不香?2021-10-29 835

-

什么样的Verilog代码风格是好的风格?2022-10-24 2551

-

为什么 MySQL 单表不能超过 2000 万行?2023-06-29 1401

-

再创新高!深开鸿OpenHarmony社区代码贡献量超过200万行!2023-10-13 1340

-

社区代码贡献企业启新篇,深开鸿代码贡献量超过200万行2023-10-18 1519

-

MySQL单表数据量限制:为何2000万行成为瓶颈?2024-02-27 8474

-

深开鸿开源鸿蒙社区主干代码贡献量破650万行2026-01-07 663

全部0条评论

快来发表一下你的评论吧 !