MOS管的米勒效应:如何平衡抑制米勒效应和抑制EMI风险的关系

描述

关于MOS管的米勒效应,已经输出了8篇,今天这一篇是MOS管章节的最后一篇,下一篇就开始整理运放相关的内容。我个人认为今天聊的这个话题至关重要:抑制米勒效应和抑制EMI之间如何平衡。

一道问题

在前面文章《MOS管的米勒效应(3)--如何减小米勒平台》中有提到:如何抑制米勒效应,三种优化策略其中之一就是减小栅极串阻Rg。但是在文章中没有提及减小到多少才算是合适。

照例,先抛出来一道连环问题:想要抑制米勒效应,减小栅极串阻Rg,减小到什么程度才算合适?如何衡量?减小Rg会不会引入其他问题,比如EMI问题?

这道题,大概率不会在技术面试中出现,太细,也太考验基本功。但是,我觉得搞研发的硬件小伙伴想要设计出高质量的电路,有必要花精力研究下。

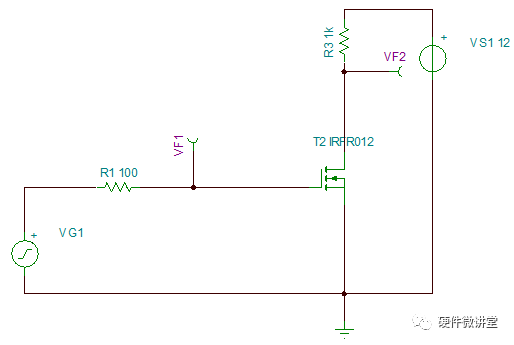

仿真模型的升级

上图,看过前面几篇文章的同学应该不陌生,我们就只用阻性负载,MOS管驱动也很简单,就一个R1=100Ω。VG1设置成5V的阶跃,上升变压为1us。用示波器捕捉波形,如下图所示,示波器的具体设置方法在第(3)篇文章中讲过,这里不做重复。

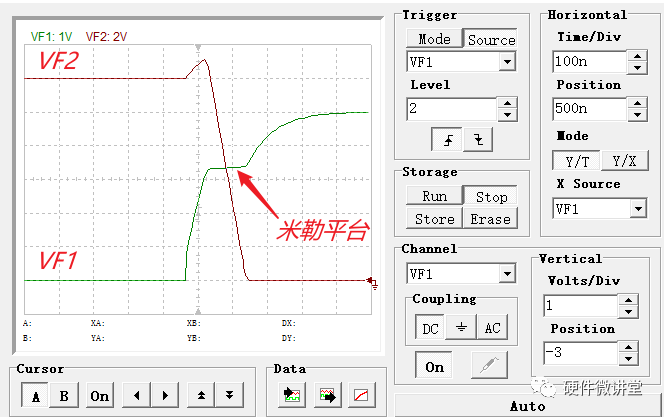

我们尝试调整不同的R1(1Ω/10Ω/50Ω/100Ω),则对应有不同的米勒平台,如下图所示,R1=1Ω时米勒平台时间最短。

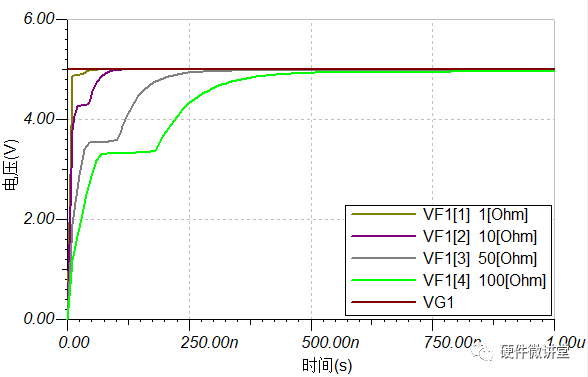

我们把上面的阻性负载换成感性负载,则有如下模型:

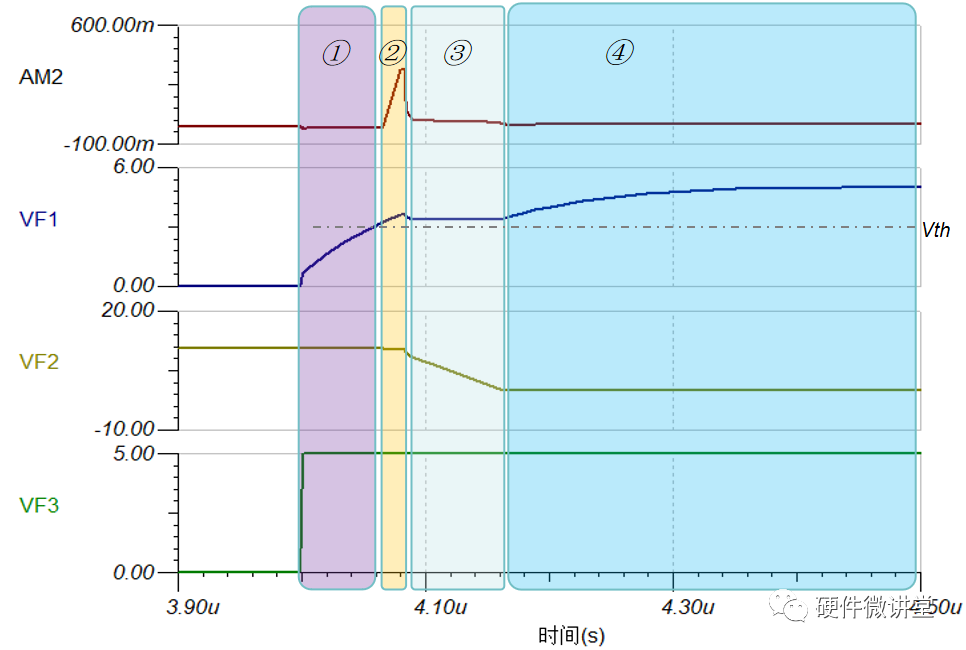

仿真出来是这样,前面文章详细分解过,这里不展开。

这里需要考虑,在咱们的实际电路中,元器件引脚会有寄生电感和寄生电容,PCB走线会有分布电感和分布电容,而MOS管引脚之间还有结电容Cgs、Cgd、Cds等,这些都会对电路的实际性能产生影响。

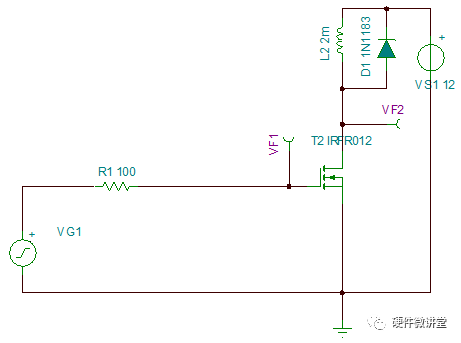

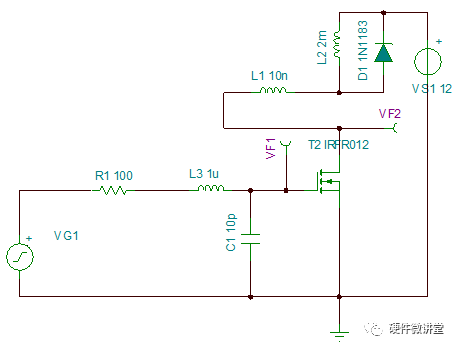

考虑到寄生/分布电容、寄生/分布电感,还有结电容,那上面感性负载的模型可能就要适当发生变化。我们对仿真模型稍作调整,如下图所示:

L3是栅极驱动信号上寄生电感和分布电感的总和,约为1uH。C1为栅极驱动信号上PCB走线的分布电感。这里Cgs、Cgd、Cds都没有画出来。

L1为MOS寄生电感和PCB分布电感的总和。

注意:这里的模型调整可能未必合适,仅供理论分析参考和趋势判断。

仿真验证

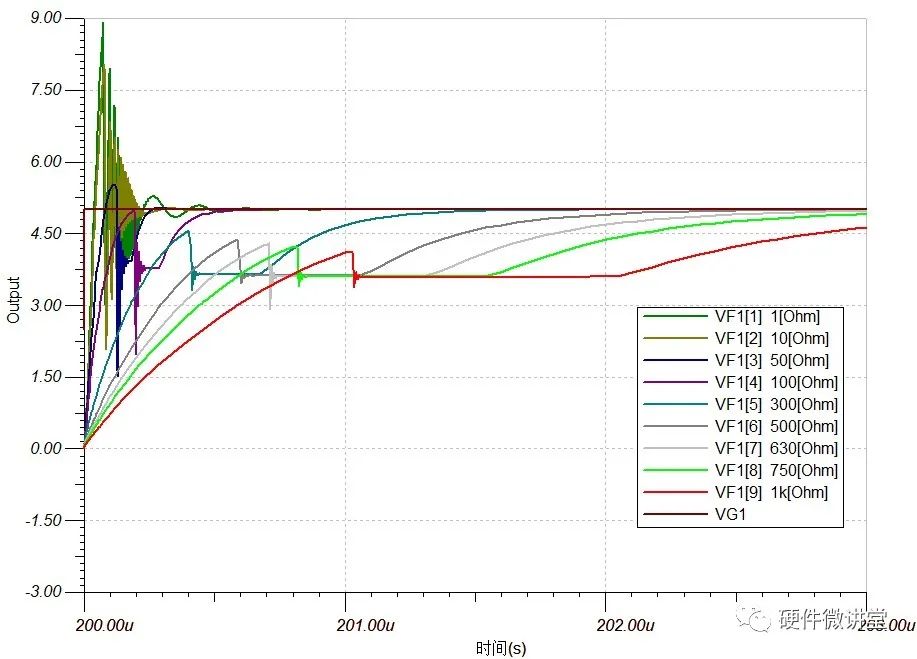

基于上述模型的调整,如果给VG1一个摆幅为0~5V,频率10kHz的方波信号,此时我们把R1(Rg)设置为变量,分别去1~1kΩ中不同的值,我们看下仿真结果会是怎样的。

上图给出的是VF1(即Vgs)的波形,能总结出什么结论么?

①当R1=1Ω,Vgs上发生了剧烈的振荡,而且振荡幅值(能量)很高;

②随着R1的增大,振荡幅值逐渐减小;

③随着R1的增大,米勒平台时间却在增大;

④当R1=1kΩ时,振荡幅值最小,但米勒平台时间最大。

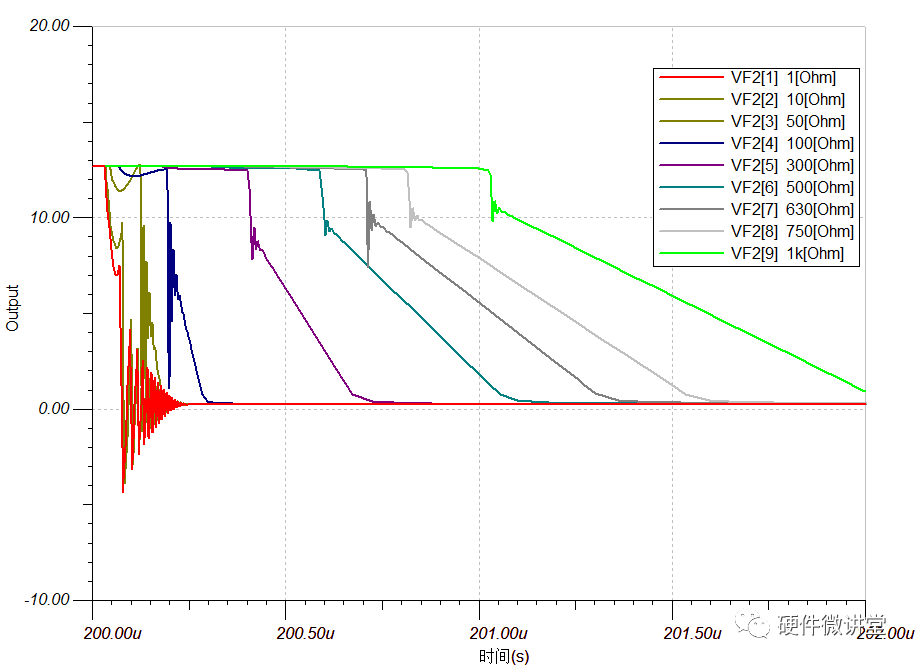

我们再看下VF2(即Vds)的波形,如下图所示:

从VF2(Vds)的变化趋势,能总结出什么结论呢?

①当R1=1Ω,Vds上发生了剧烈的振荡,而且振荡幅值(能量)很高;

②随着R1的增大,振荡幅值逐渐减小;

③当R1=1kΩ时,振荡幅值最小。

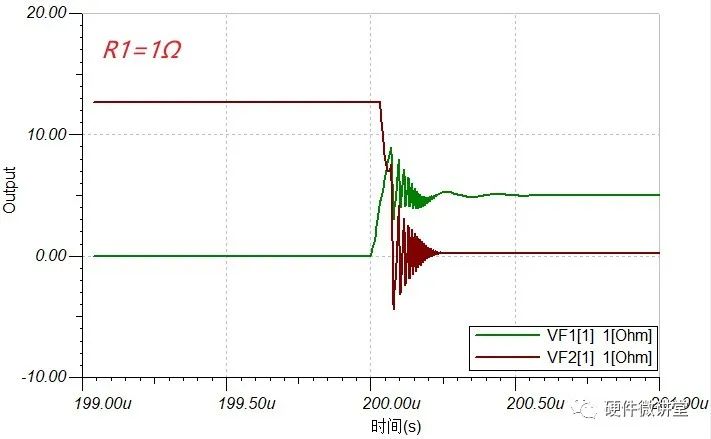

我们再换一个角度,只看R1=1Ω的情况下,如下图所示:

VF1(Vgs)和VF2(Vds)都发生了强烈振荡,说明在此过程中有LC谐振发生,这期间高次谐波能量必然被放大,必然会增加EMI问题的风险。但是我们也注意到此时米勒平台持续时间却是最短的,这样MOS管的开关损耗则可以降低。

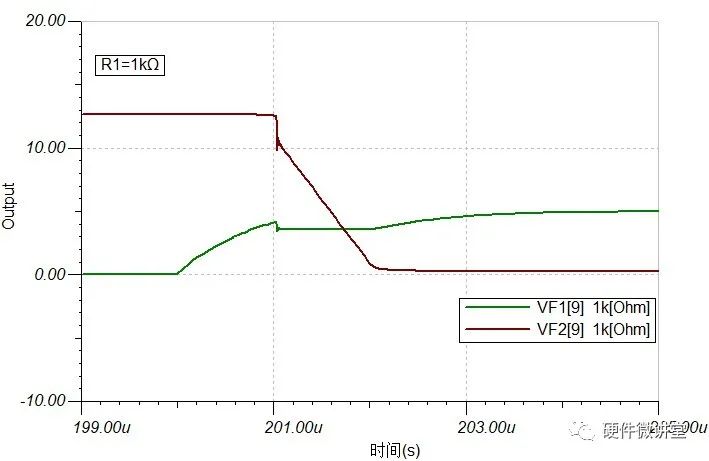

我们再看下R1=1kΩ的情况下,如下图所示:

VF1(Vgs)和VF2(Vds)振荡不明显,但此时米勒平台的时间则大大延长,这样MOS管的开关损耗会增大。

审核编辑:汤梓红

-

MOS管的米勒效应解析2023-02-03 5311

-

MOS管的米勒效应:如何减小米勒平台2023-02-14 14964

-

说说MOSFET中的米勒效应2023-05-16 4278

-

搞懂MOS管的米勒效应2023-07-21 10510

-

米勒效应的本质是什么?2024-01-11 2440

-

MOS管的米勒效应-讲的很详细2025-03-25 629

-

搞懂MOS管,你必须知道的米勒效应2026-01-19 156

-

米勒效应问题2017-12-21 7092

-

揭秘MOS管开关时米勒效应的详情2018-12-19 4017

-

请问MOS管与IGBT都有GS米勒效应吗?2019-09-05 2317

-

详解米勒平台的米勒效应和形成原理2019-02-02 71901

-

米勒电容器寄生导通效应的抑制方法2022-03-17 1291

-

MOS管开关时的米勒效应基本原理2022-08-30 3793

-

浅谈MOS管开通过程的米勒效应及应对措施2023-02-10 12788

-

MOS管开通过程的米勒效应及应对措施2023-11-27 5245

全部0条评论

快来发表一下你的评论吧 !