NMOS晶体管线性区导通电阻详解

模拟技术

2518人已加入

描述

导读

NMOS晶体管工作在线性区时,漏源两端的沟道存在阻性连接,以下文字对这种阻性连接进行简单介绍。

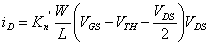

NMOS晶体管工作在线性区时的漏源电流表达式为式(1),在该工作区下阻性沟道直接连接漏源两端,沟道中任意位置氧化层两端的电压只要超过阈值电压,就能产生这种阻性连接。

(1)

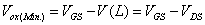

任意位置氧化层两端的电压在为漏端的电压最小,即

(2)

因此,VGS - VDS > VTH 时,就能产生阻性连接。

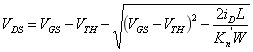

对式(1)进行移项并整理,可得

(3)

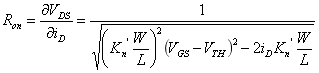

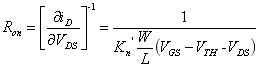

故导通电阻的表达式为

(4)

或者

(5)

式(4)和式(5)即是NMOS晶体管工作在线性区时的导通电阻。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

详解NMOS晶体管的工作过程2025-12-10 1290

-

MOSFET导通电阻参数解读2025-05-26 5120

-

NMOS晶体管和PMOS晶体管的区别2024-09-13 10681

-

NMOS晶体管线性区漏源电流详解2023-04-17 10066

-

降低高压MOSFET导通电阻的原理与方法2023-02-27 3213

-

nmos晶体管的电流方程 nmos晶体管饱和伏安特性方程2023-02-11 5298

-

使用双极性结型晶体管(BJT)和NMOS晶体管的稳定电流源2021-11-01 2592

-

GaN功率晶体管的动态导通电阻测量技术的挑战和方法2021-10-27 8387

-

SiC-MOSFET功率晶体管的结构与特征比较2018-11-30 5551

-

晶体管的分类与特征2018-11-28 2694

-

导通电阻,导通电阻的结构和作用是什么?2010-03-23 5795

-

晶体管线性阶梯波发生器电路图2009-07-01 780

全部0条评论

快来发表一下你的评论吧 !