NMOS晶体管线性区漏源电流详解

模拟技术

描述

导读

之前的文章对MOS电容器进行了简单介绍,因此对MOS晶体管的理解已经打下了一定的基础,本文将对深入介绍NMOS晶体管的结构及工作原理,最后再从机理上对漏源电流的表达式进行推导说明。

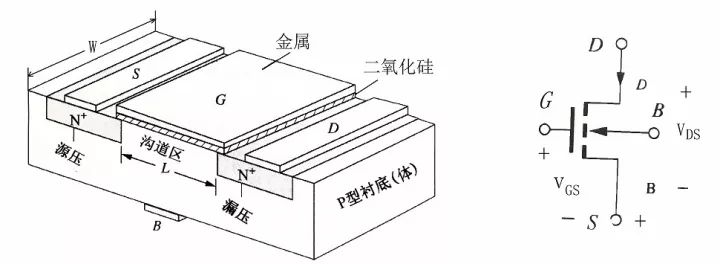

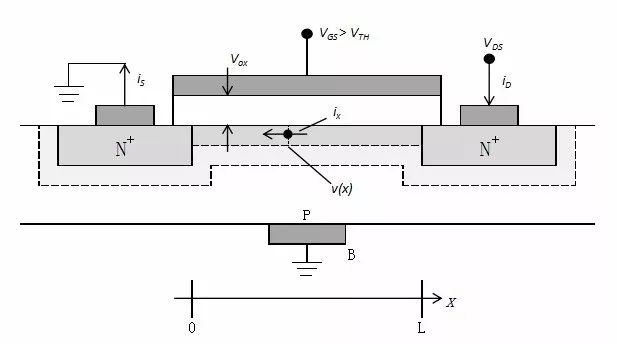

在P型硅MOS电容器中增加两个重掺杂的N型扩散区,就形成了MOSFET,这两个N型区分别为源区和漏区,且与栅的边缘对准。源区和漏区分别和衬底形成PN结,如图1所示,L是沟道长度,W是沟道宽度。

图1 (a)NMOS晶体管结构图 (b)四端MOSFET电路符号

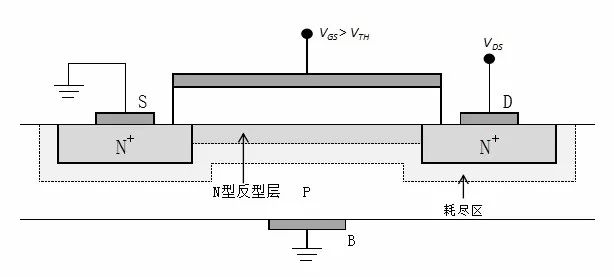

当栅源电压小于阈值电压VTH时,由于MOS电容器的特性,P型衬底与氧化物交界面只有耗尽区,没有可参与导电的自由电子,并且源漏之间存在背靠背的PN结,因此存在很小的漏电流。当极源电压增大到阈值电压VTH以上时,P型衬底与氧化物交界面形成N型反型层,使得源区和漏区相连,形成导电沟道,如图2所示。

图2 NMOS晶体管导电沟道

稳态下,iG和iB都为零,因此流入漏极的电流等于流出源极的电流,即iS=iD

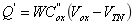

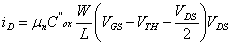

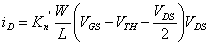

为了推导出漏极电流的表过式,需要考虑导电沟道中电荷的传输过程,在沟道中任意位置,单位长度的电子电荷等于

C/cm (1)

式中C’’ox为单位面积的氧化电容(F/cm2);且该式只适用于Vox-VTH > 0的场合,VTH是栅极的阈值电压;Vox是氧化层上的电压;

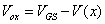

由于漏源电压为VDS,且源极接地,故漏极电压即为VDS,因此沟道中沿沟道方向存在电压梯度,假设沟道与源区N型扩散区的交界点为坐标原点,则沟道与漏区N型扩散区的交界点为坐标L,如图3所示,那么沟道中任意点x处的电压为V(x),且有V(0)=0V,V(L)=VDS,因此氧化层上的电压也随位置的变化而变化

(2)

因此在源端Vox=VGS,在漏端Vox=VGS-VDS。

图3 NMOS晶体管i-v特性电路模型

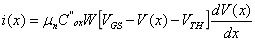

沟道中,任意位置的电子漂移电流等于单位长度的电荷与电子运动速度vn的乘积

(3)

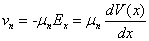

而电子运动速度vn为

(4)

式中μn为电子迁移率,将式(1)、(2)、(4)可得

(5)

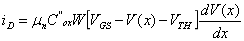

由于沟道中任意位置的电流均相等,且等于漏极电流iD ,则有

(6)

将dx项移至左边,且对x在0 - L之间积分,可得

(7)

(8)

式(8)中,Kn’=μnC’’ox,且只与NMOS的生产工艺有关。该式即为NMOS晶体管工作在线性区时的漏源电流表达式。

需要注意的有:

1)式(8)只适用于Vox-VTH > 0的场合,即 VGS- VDS >VTH的场合;

2)Kn’并不为常数,而是随着VGS的增大而减小;

-

抬升源漏技术如何拯救纳米尺度晶体管2026-04-10 742

-

NMOS晶体管和PMOS晶体管的区别2024-09-13 10704

-

晶体管的漏极与源极有什么区别2024-08-13 13595

-

晶体管和场效应管的本质问题理解2024-01-18 1827

-

NMOS晶体管线性区导通电阻详解2023-04-17 5731

-

NMOS放大器电路模型详解(二)2023-02-16 5161

-

nmos晶体管的电流方程 nmos晶体管饱和伏安特性方程2023-02-11 5310

-

浅析NMOS和PMOS详解以及电路设计2021-11-11 3745

-

使用双极性结型晶体管(BJT)和NMOS晶体管的稳定电流源2021-11-01 2596

-

一文让你秒懂场效应晶体管的所有参数2019-04-04 4210

-

晶体管工作原理2016-06-29 4052

-

晶体管线性阶梯波发生器电路图2009-07-01 781

全部0条评论

快来发表一下你的评论吧 !